# LJMU Research Online

Vukosavic, SN, Peric, LS and Levi, E

AC Current Controller with Error-Free Feedback Acquisition System

http://researchonline.ljmu.ac.uk/id/eprint/3627/

Article

**Citation** (please note it is advisable to refer to the publisher's version if you intend to cite from this work)

Vukosavic, SN, Peric, LS and Levi, E (2016) AC Current Controller with Error-Free Feedback Acquisition System. IEEE TRANSACTIONS ON ENERGY CONVERSION, 31 (1). pp. 381-391. ISSN 0885-8969

LJMU has developed LJMU Research Online for users to access the research output of the University more effectively. Copyright © and Moral Rights for the papers on this site are retained by the individual authors and/or other copyright owners. Users may download and/or print one copy of any article(s) in LJMU Research Online to facilitate their private study or for non-commercial research. You may not engage in further distribution of the material or use it for any profit-making activities or any commercial gain.

The version presented here may differ from the published version or from the version of the record. Please see the repository URL above for details on accessing the published version and note that access may require a subscription.

For more information please contact <a href="mailto:researchonline@ljmu.ac.uk">researchonline@ljmu.ac.uk</a>

http://researchonline.ljmu.ac.uk/

# AC Current Controller with Error-Free Feedback Acquisition System

Slobodan N. Vukosavić, Senior Member, IEEE, Ljiljana S. Perić, and Emil Levi, Fellow, IEEE

Abstract-In this paper, we introduce an improved ac current controller with robustness against the noise in the feedback path. This three-phase current controller is suited for inverter supplied ac machines and grid-connected power converters. Conventional solutions make use of symmetric pulse-width modulation (PWM) techniques with feedback sampling in the middle of the voltage pulses. Single-sample-based feedback acquisition gets affected by the noise and parasitic phenomena. We perform a thorough analytical and experimental study on feedback errors with conventional sampling, and we consider the impact of the lockout time, motor cables, winding capacitance, and anti-aliasing filters. In order to suppress a significant spectral content in the area of low-order harmonics, we apply an improved acquisition technique, which uses a period-average and removes any PWM noise from the feedback signals. Both anti-aliasing filter and proposed period-average filter introduce delays, which impair the control-loop performance. The conventional current controller is then extended to suppress the effects of the delays. Parameter setting procedure is devised to achieve both the bandwidth and the robustness against the parameter changes. Analytical and experimental studies prove that the proposed feedback acquisition technique improves the robustness in the presence of variable delays and switching transients. Experimental tests show that the extended current controller with period-average feedback acquisition reaches the same bandwidth and robustness as the state-of-the-art controller.

*Index Terms*—AC motor drives, current control, high performance control, signal acquisition.

#### I. INTRODUCTION

**E** LECTRICAL drives employ position or speed control as the outer control loop. Most drives comprise a digital current controller as an inner loop [1], [2]. A fast and accurate current loop is crucial for the drive performance [3], [4]. In high-speed drives, it is essential to provide the proper decoupling of transients in *d*-axis (flux) and *q*-axis (torque) [5]–[7] and to achieve a robust operation with relatively large fundamental frequency  $f_e$  for the given sampling frequency  $f_S$  [8]–[11]. In grid-connected inverters, current loop accuracy determines the quality of the current waveforms injected into the grid.

Performance limits of current controllers are mostly related to time delays in computation, modulation, and feedback acquisition [12]. The switching ripple of the current is caused

Manuscript received July 15, 2015; accepted August 31, 2015. Paper no. TEC-00503-2015.

S. N. Vukosavić is with the Electrical Engineering Department, University of Belgrade, 11000 Belgrade, Serbia (e-mail: boban@etf.rs).

L. S. Perić is with Ariom d.o.o., Belgrade 11070, Serbia (e-mail: office@ariom.rs).

E. Levi is with the School of Engineering, Technology and Maritime Operations, Liverpool John Moores University, Liverpool, L3 3AF, U.K. (e-mail: e. levi@ljmu.ac.uk).

Digital Object Identifier 10.1109/TEC.2015.2477267

by pulse-width modulated (PWM)-based voltage actuation, and it coincides with the Nyquist frequency. Consequential antialiasing filtering and feedback-sampling techniques introduce delays which add to computational delays and delays related to the PWM implementation. Closed-loop performance requires the proper modeling and accounting for such delays [8], [9], [11]. Dead-beat and predictive controllers [13] are fast, but their sensitivity to parameter changes reduces their practical use.

1

Most widely used are the proportional-integral (PI) current controllers in synchronous frame [8], [9], [14]. Well-established parameter-setting procedures [7], [8], [12], [14] allow a straightforward implementation with the possibility to achieve a fast step response and the required disturbance rejection. The use of internal model control (IMC) concept [7] results in current controllers that cancel undesired dynamics and achieve the closed-loop bandwidth up to  $f_{BW} = 0.11 \cdot f_S$ . Similar bandwidth is achieved with stationary-frame current controllers in [12], where  $f_{BW} = 0.07 \cdot f_S$ . Gain tuning proposed in [14] considers both the reference tracking and the disturbance rejection and proposes the optimum closed-loop gain and active resistance parameter. The closed-loop bandwidth ranges from  $0.08 \cdot f_{\rm S}$  with no overshoot, up to  $0.14 \cdot f_{\rm S}$  with an overshoot of 40%. The PI controller design in [8] considers exact model and all the relevant delays, using neither Tustin nor other approximations. A comprehensive controller design is based on applying the IMC concept in discrete time domain. The closed-loop gain suggested in [8] is similar to the gain of [14]. The available bandwidth is  $f_{BW} = 0.1 \cdot f_S$ , with a very large value of the fundamental frequency  $f_e$  for the given sampling frequency  $f_S$ . In most recent current control solutions, suggested gain is close to  $k = 0.25 \cdot f_S$ , while the closed-loop bandwidth stays next to  $f_{\rm BW} = 0.1 \cdot f_S$ .

All the controllers acquire the feedback signals by means of synchronous sampling, wherein the current samples are taken at the center of the voltage pulses [1], [8], [9], [12]. In this way, the feedback path has unity gain and a negligible delay. In an ideal case, the feedback is not affected by the switching ripple. In cases where the feedback waveform gets affected by delays of the anti-aliasing filter [15], delays introduced by the lockout time, by the driver circuit and switching delays, the switching ripple affects the samples and introduces an error in the feedback path. Single-sample-based acquisition is also prone to switching transients caused by the cable capacitance, the winding parasitic capacitance and other parasitic LC elements.

The motivation of this paper is to measure and study the sampling errors in a practical PWM converter and to reduce these errors by an improved sampling technique. In order to cope with the associated delays, we propose an enhanced current controller which ensures excellent overall performance. Thus, the main contributions of the paper can be summarized as follows: 1) a detailed study, illustrated with experimental results, of the impact of various parasitic phenomena on accuracy of digital current control; 2) a proposal for an improved method of sampled current averaging that is capable of significant accuracy enhancement of the current feedback signal; and 3) a novel structure of the current controller that utilizes the developed current averaging method and achieves excellent dynamic and steady-state performance.

The paper is organized as follows. Section II at first discusses current sampling errors and then suggests a method for achieving error-free sampling. Section III describes the development of the enhanced current controller. Experimental verification of the developed current controller is provided in Section IV, where a comparison with a state-of-the-art current controller is also included. Section V concludes the paper.

### II. SAMPLING ERRORS AND NOVEL ACQUISITION TECHNIQUE

Practical current controllers acquire the feedback signals from an A/D converter. The converter receives the output currents as continuous, analog signals; it takes the samples at regular  $T_S = 1/f_S$  spaced instants and converts them into digital forms. According to the sampling theorem [16], the sampled analog signal should be free from any spectral content above the frequency of  $f_S/2$ , also called the Nyquist frequency. Otherwise, the train of samples comprises the sampling errors, also called the aliased frequencies.

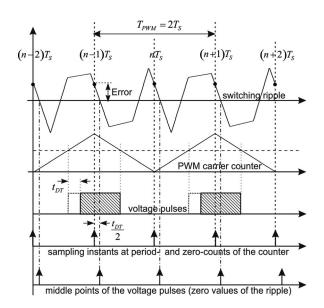

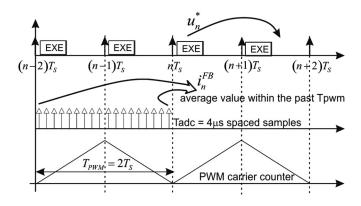

In PWM converters, the feedback currents comprise the switching ripple current, which brings in the frequency components around switching frequency  $f_{\rm PWM}$  and its multiples. Most current controllers [8], [9], [12], [14] use synchronous sampling, where the samples are taken twice in each  $T_{\rm PWM}$  period, in the middle of both positive and negative voltage pulses, as shown in Fig. 1. The sampling instants are spaced by  $T_{\rm PWM}/2$ , thus resulting in  $f_S = 2 \cdot f_{\rm PWM}$ . In cases where the zero-crossing of the switching ripple coincides with the sampling instants, the conventional synchronous sampling provides error-free feedback signals, unaffected by the ripple.

Whenever the switching ripple is shifted with respect to the sampling instants, the feedback signal contains an error. In Fig. 1, the zero-crossing of the switching ripple is delayed by  $t_{DT}/2$  due to the lockout time, and the sample of the current contains an error. At the same time, the zero-crossing of the ripple can be shifted by the intrinsic time-delay of the anti-aliasing low-pass filter (LPF) [15].

Sampling errors are also introduced by disturbances other than the ripple. Conventional sampling is prone to the noise, as it takes a single sample per period  $T_S$ . The noise attenuation of the anti-aliasing LPF is increased by lowering its cutoff frequency [15], [17]. Yet, an LPF with low cutoff frequency delays the feedback and interferes with the control loop [17], [18]. Therefore, the available attenuation is restrained. At the same time, large dv/dt values of the PWM voltage waveforms in conjunction with parasitic capacitance of the cables and windings give rise to poorly damped oscillations [19] of the

Fig. 1. Conventional synchronous sampling of the output currents. The switching ripple is obtained for  $\tau_e = L_S/R_S \gg T_{\rm PWM}$ . The sampling period  $T_{\rm S}$  is equal to  $T_{\rm PWM}/2$ . The current is sampled twice at instants when the PWM carrier reaches either zero or the period count. The same events trigger the control interrupt.

TABLE I

IMPACT OF THE LOCKOUT TIME ON  $I_q$  MEASUREMENT ERRORS

| $\Delta I_{ m rms}/I_{ m nom}$ (%) obtained v | with $I_q = 4$ Å | A, $f_{out} = 27$   | '5 Hz, no cał | ble, and $\tau_{\rm LPI}$ | $F = 5 \ \mu s$ |

|-----------------------------------------------|------------------|---------------------|---------------|---------------------------|-----------------|

| Lockout time $t_{DT}$                         | $2 \mu s$        | <b>3</b> μ <b>s</b> | $4 \mu s$     | <b>5</b> μ <b>s</b>       | $7 \mu s$       |

| Synchronous sampling                          | 1.68             | 1.96                | 2.27          | 2.64                      | 3.33            |

| Averaging in each $T_{\rm PWM}$               | 0.68             | 0.73                | 0.82          | 0.89                      | 0.95            |

TABLE II IMPACT OF THE LPF DELAYS ON  $I_q$  Measurement Errors

| $\Delta I_{\mathrm{rms}}/I_{\mathrm{nom}}$ (%) obtained | with $I_q$ | $= 4 \text{ A}, f_0$ | $_{\rm ut} = 275$    | Hz, no cable | , and $t_{DT} = 3\mu$ |

|---------------------------------------------------------|------------|----------------------|----------------------|--------------|-----------------------|

| LPF time constant $\tau_{LPF}$                          | $5 \mu s$  | <b>10</b> µs         | <b>15</b> μ <b>s</b> | <b>20</b> µs | <b>80</b> µs          |

| Synchronous sampling                                    | 2.05       | 3.40                 | 4.07                 | 4.22         | 2.02                  |

| Averaging in each $T_{\rm PWM}$                         | 0.74       | 0.73                 | 0.71                 | 0.65         | 0.73                  |

TABLE III IMPACT OF THE CABLE LENGTH ON  ${\cal I}_q$  Measurement Errors

| $\Delta I_{\rm rms}/I_{\rm nom}$ (%) obtained with $I_q = 4$ A, $f_{\rm out} = 275$ Hz,<br>$	au_{\rm LPF} = 5\ \mu$ s, and $t_{DT} = 3\ \mu$ s |      |      |      |      |      |

|------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|

| <i>l</i> (m) of the shielded cable                                                                                                             | 0    | 5    | 10   | 15   | 20   |

| Synchronous sampling                                                                                                                           | 2.02 | 2.55 | 4.24 | 5.69 | 7.03 |

| Averaging in each $T_{\rm PWM}$                                                                                                                | 0.72 | 0.78 | 0.82 | 0.83 | 0.91 |

output voltages and currents. Passing through the LPF, these oscillations affect the samples and compromise the feedback signal. Other noise signals may produce similar effects.

In this section, we consider the errors in the feedback path, provide experimental evidence, evaluate the impact of the sampling errors on the closed-loop performance, and propose

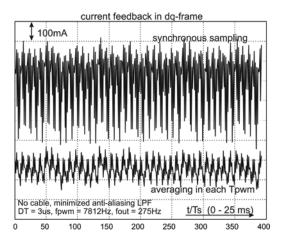

Fig. 2. Waveforms of steady-state q-axis current obtained from the experimental setup of the Appendix. The motor is connected with short wires (no cable), with  $T_{\rm PWM} = 128 \ \mu s, \ t_{DT} = 3 \ \mu s, \ f_{\rm OUT} = 275 \ {\rm Hz}$  and with the minimum indispensable anti-aliasing LPF.

the method for error-free feedback acquisition. The experimental setup used in this section, as well as in Section IV, comprises a six-pole synchronous motor with surface-mounted permanent magnets, supplied from an insulated gate bipolar transistor (IGBT)-based inverter running with  $E_{\rm DC} = 520$  V at  $f_{\rm PWM} =$ 7.812 kHz. The setup is controlled from a digital signal processor (DSP)-based platform, which uses TMS320F28335 device. All the measurements are obtained from internal DSP variables, logged in real time on a dedicated secure digital (SD) card. The relevant parameters are given in the Appendix.

In order to get the proper insight into sampling errors, the experimental results in Tables I–III and Figs. 2–4, discussed shortly, are obtained in steady state, with reduced gains of the current controller. Low gains are used to avoid sustained oscillations, caused by interaction of high gains and erroneous sampling.

#### A. Impact of the Lockout Time

In common PWM converters, the lockout time  $t_{DT}$  ranges from 2 to 4  $\mu$ s [20], [21], and it delays turn-on of the power transistors. Depending on the sign of the output current, delay affects either the on-going or the off-going edge of the successive voltage pulse. As a consequence, the center of the successive voltage pulse is delayed by  $t_{DT}/2$  (see Fig. 1), and the sampling instant misses the zero-crossing of the switching ripple. The feedback signal gets affected by the switching ripple, thus introducing the error in the actual output current. In most cases, erroneous sampling compromises the system performance. Sampling error depicted in Fig. 1 depends on the slope of the current  $di/dt \approx E_{DC} \cdot t_{DT}/L_S$ , and it increases for lower values of the load inductance  $L_S$ . The error gets very large with low-inductance synchronous motors, which have surfacemounted magnets and particularly low  $L_S$ .

Experimental waveforms with the q-axis current errors caused by the sampling process are given in Fig. 2. In the absence of the cable capacitance and with minimized LPF, the errors are related mainly to the lockout time. The upper waveform of Fig. 2 is obtained with conventional synchronous sampling. The lower waveform is obtained by oversampling the signals each  $T_{ADC} = 4 \ \mu s$  and then deriving the average value each  $T_S$  for the past  $T_{PWM} = 2T_S$ .

It is of interest to provide experimental evidence on the error in feedback signals produced by variable  $t_{DT}$ . For this purpose, the experimental setup of the Appendix is tested in steady state, with minimized output capacitance and with the lowest permissible attenuation of the LPF. In Table I, the rms values of the q-axis current measurement errors are given for conventional synchronous sampling. For  $t_{DT}$  ranging from 2 up to 7  $\mu$ s, the errors change between 1.68% and 3.33% of the rated current. In parallel, the feedback samples of  $I_a$  are also obtained by oversampling, wherein the samples are taken each 4  $\mu$ s, and an average of 32 samples is derived in  $T_{\rm PWM}$  period. The latter computation acts as a finite impulse response (FIR) filter with an infinite attenuation at  $f_{\rm PWM} = 1/T_{\rm PWM}$ , thus eliminating the ripple. For this reason, the errors reported in Table I and obtained with the prescribed averaging are introduced by the disturbances other than the ripple, where the most emphasized are the slotrelated harmonics within the motor back-electromotive force.

#### B. Impact of the Anti-aliasing Filters

Sampling errors arise from the spectral components of the input analog signal at frequencies above  $f_S/2$  [18]. In digital current controllers with  $f_S = 2 \cdot f_{PWM}$  [8], [14], the analog signals that are brought to the analog-to-digital converter (ADC) inputs should be free from any spectral components above the Nyquist limit of  $f_{PWM}$ . Suppression of harmful frequencies is performed by anti-aliasing LPF. This filter can be a simple RC network or an active filter [15], [18]. Due to a limited attenuation of analog filters, suppression of harmful frequencies is only partial. In most cases, it is sufficient to reduce the harmful signals down to the level of 1 LSB of the ADC. Attenuation of RC filter at high frequencies is close to  $1/(\omega \cdot \tau_{\rm LPF})$ , where  $1/\tau_{\rm LPF} = 1/RC$  is the cutoff frequency. An increased  $\tau_{\rm LPF}$ helps the filtering, but it also introduces phase delay and impairs the control loop. With synchronous sampling of Fig. 1, RC filter delays the zero-crossing of the ripple and contributes to the sampling errors. Experimental evidence showing the impact of the time constant  $\tau_{\rm LPF} = RC$  on the rms value of the q-current is given in Table II. The error increases with  $\tau_{\rm LPF}$  and exceeds 4%. With  $\tau_{\rm LPF}$  as large as 80  $\mu$ s, the cutoff frequency drops below 2 kHz, attenuation at high frequencies is increased and the errors are lower. With the cutoff frequency  $1/\tau_{\rm LPF}$  reaching the desired closed-loop bandwidth, the phase delay of the filter brings in an unacceptable performance deterioration.

## C. Impact of Parasitic LC Oscillations

In both motor-connected and grid-connected inverters, there are parasitic *LC* elements, such as the series inductance and parallel capacitance of the cables, winding-to-winding and winding-to-ground capacitance, as well as series and parallel elements of electromagnetic interference (EMI) filters. These elements create *LC* circuits with resonant frequencies  $f_{LC}$ ,

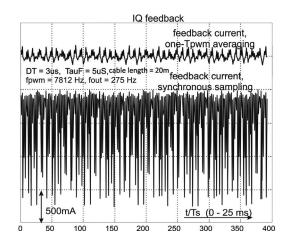

Fig. 3. Waveforms of steady-state q-axis current obtained with a 20-m-long shielded motor cable. The cable characteristic impedance is 62  $\Omega$ . The experimental setup of the Appendix runs with  $f_{\rm OUT} = 275$  Hz,  $T_{\rm PWM} = 128 \ \mu s$ ,  $t_{DT} = 3 \ \mu s$ , and with the anti-aliasing LPF of  $\tau_{\rm LPF} = 5 \ \mu s$ .

which exceed 1 MHz [19]. At the same time, the output voltages of IGBT inverters have the rate of change larger than 2500 V/ $\mu$ s [20]. The switching events give rise to *LC* oscillations whose amplitude decays away in less than 12  $\mu$ s [19]. Whenever the sampling instant in Fig. 1 approaches the preceding switching, the sample gets affected by the parasitic oscillations. For decay of 12  $\mu$ s and  $T_{\rm PWM} = 128 \ \mu$ s, erroneous sampling arises for the pulse width from 0% to 20%, as well as the pulse width from 80% to 100%.

Experimental waveforms of *q*-axis current errors obtained with a 20-m-long shielded motor cable are given in Fig. 3. The lower trace represents the error obtained with synchronous sampling. The upper trace is obtained with the same oversampling procedure used in Fig. 2.

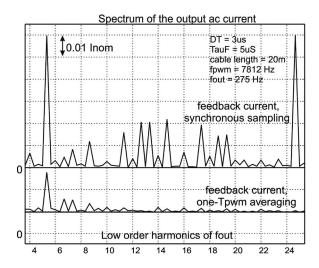

Harmonic content of the output ac current is given in Fig. 4, obtained in the same operating conditions as those of Fig. 3. The fifth harmonic reaches 6%, while a number of harmonics between 11th and 19th reach 2% of the rated current. In Table III, the change in the rms value error of the q-axis current is given as a function of the cable length. With a 10-m-long motor cable, the rms value of the error exceeds 4%.

Sampling errors comprise high-frequency components (see Fig. 4), which reduce permissible gain of current controller and impair the closed-loop bandwidth. In a similar manner, the sampling errors reduce the applicable values of the active resistance, which is often used to improve disturbance rejection of the controller [14]. At the same time, the presence of low-order harmonics contributes to distortions and an increase in THD of the output current, which is of particular importance in grid-connected power converters.

# D. Means for Achieving Error-Free Sampling

The errors caused by delayed zero-crossing of the switching ripple can be reduced but not eliminated by delaying the sampling instants [15]. Delay of the voltage pulses is affected by the lockout time, but it also depends on delays in gate drivers and on the switching waveforms of semiconductor power switches,

Fig. 4. Waveforms of steady-state q-axis current obtained with a 20-m-long shielded motor cable. The cable characteristic impedance is 62  $\Omega$ . The experimental setup of the Appendix runs with  $f_{OUT} = 275$  Hz,  $T_{PWM} = 128 \ \mu s$ ,  $t_{DT} = 3 \ \mu s$ , and with the anti-aliasing LPF of  $\tau_{LPF} = 5 \ \mu s$ .

where the latter change with current and operating temperature. Therefore, delay of the sample instants by  $t_{DT}/2$  can reduce, but it cannot eliminate the errors introduced by voltage-pulse delays. Delays introduced by the anti-aliasing LPF are predictable, and they do not change. Harmonic content of the switching ripple comprises several components, with the most emphasized residing next to  $f_{\rm PWM}$  and  $2f_{\rm PWM}$ . Individual harmonic components have different time delays. Therefore, the zero-crossing of the filtered switching ripple changes with the modulation index, thus making the LPF delay compensation only partial.

Sampling errors in Tables I and II are caused by  $t_{DT}$  and LPF delays. For lower values of  $t_{DT}$  and  $\tau_{LPF}$ , the errors remain close to 2%, the value which can be tolerated in some cases. The errors in Table III are obtained with shielded cable. Parasitic load capacitance brings in high-frequency oscillations and increases the errors up to 7%. Therefore, it is necessary to devise the feedback acquisition technique capable of an error-free operation in the presence of variable delays, LPF, and spurious oscillations. This need is more emphasized in cases with elevated winding capacitance, long cables, but also in high-performance drives where the bandwidth is high, closed-loop gains are large, and where the sampling errors cannot be tolerated.

Contemporary DSP controllers such as TMS320F28335 comprise a fast 12-bit, 16-channel ADC peripheral, which can be synchronized with the PWM pulse generator. It is possible to take one sample on each of 16 channels in a sequence much shorter than 4  $\mu$ s. The results can be collected and stored automatically by means of a dedicated on-chip direct memory access (DMA) unit. These tools can be used to acquire  $T_{ADC}$ -spaced samples of the output current and to calculate the feedback signal as an average value of the past  $N_{OV} = T_{PWM}/T_{ADC}$ , covering the time span of  $T_{PWM}$ . The process is illustrated in Fig. 5. The experimental setup of the Appendix runs with  $T_{PWM} = 128 \ \mu$ s,  $T_{ADC} = 4\mu s$ , and it takes  $N_{OV} = 32$  samples in each PWM period.

Fig. 5. Oversampling of the output current and derivation of the feedback signal  $i^{\text{FB}}$ . Execution of the control interrupts is denoted by EXE. In interrupt that executes after  $nT_{\text{S}}$ , the feedback signal  $i_{n}^{\text{FB}}$  is calculated as the average value within the interval  $[(n-2)T_{\text{S}} \dots nT_{\text{S}}]$ .

In control interrupt triggered at  $nT_{\rm S}$ , the feedback signal  $i_n^{\rm FB}$  is calculated by summing the 32 equidistant samples acquired between  $(n-2)T_{\rm S}$  and  $nT_{\rm S}$  and dividing the sum by 32

$$i_n^{\rm FB} = \frac{1}{32} \sum_{k=0}^{31} i \left( nT_S - kT_{\rm ADC} \right)$$

(1)

where  $i(nT_S - kT_{ADC})$  is the sample of the analog input that represents the output current, taken by DMA-ADC machine at instant  $t = nT_S - kT_{ADC}$ . To probe the effects of such a technique, it is of interest to represent the averaging formula by FIR filter, which runs with the sampling time of  $T_{ADC} = 4 \ \mu s$ . The transfer function of such a filter is

$$\frac{i^{\rm FB}(z)}{i(z)} = W_{\rm FIR}(z) = \frac{1}{32} \sum_{k=0}^{31} z^{-k}.$$

(2)

Calculated attenuation of the above filter at the switching frequency  $f_{\rm PWM} = 1/(32 \cdot T_{\rm ADC})$  is infinite. The same attenuation is achieved for the integer multiples  $n \cdot f_{\rm PWM}$ . Hence, the feedback  $i^{\rm FB}$  of (1) is unaffected by the switching ripple. It has to be noticed that spurious oscillations [19], caused by the switching transients, may affect one or two adjacent samples. In (1), these samples get divided by 32. Therefore, their impact is considerably smaller than in the case of conventional synchronous sampling, as shown by experimental evidence in Table III.

With oversampling technique, design of the anti-aliasing LPF is greatly simplified. The actual sampling process takes place at  $N_{\rm OV} = 32$  times larger frequency. Hence, the practical Nyquist frequency is  $N_{\rm OV}$  times larger. For the same alias-suppression results, the anti-aliasing LPF can be designed with a 32 times larger cutoff frequency. Namely, a passive *RC* filter has a 32 times lower  $\tau_{\rm LPF} = RC$ . Design choice of  $\tau_{\rm LPF} \ge 5 \mu s$  is driven by other disturbances, related neither to the motor nor to the inverter.

Experimental verification of the feedback acquisition with one  $T_{\rm PWM}$  averaging is summarized in Tables I–III and also in Figs. 2–4, where the resulting  $I_q$  errors are compared to errors obtained with conventional synchronous sampling. Proposed feedback acquisition introduces delay into the control loop. It adds to the delay in applying the voltage reference. The value  $u_n^*$ , calculated in the interrupt triggered at  $nT_S$ , reloads into the PWM registers at instant  $(n + 1)T_S$  and affects the average value of the output voltage within the interval  $[(n + 1)T_S \dots (n + 2)T_S]$ . In order to compensate delays and maintain the current loop performance, it is necessary to enhance the controller structure.

#### III. ENHANCED CURRENT CONTROLLER

This section addresses the structure, parameter setting, and closed-loop performance of state-of-the-art current controllers, considers the impact of the proposed feedback acquisition on the closed-loop bandwidth and the robustness of the controller, and eventually introduces enhancement of the controller structure and parameter setting, designed to help using the benefits of error-free sampling while maintaining the current control performances.

# A. State-of-the-Art Current Controllers

Most widely used are the PI current controllers in synchronous frame [5]–[11], [14]. The feedback acquisition is mostly based on synchronous sampling (see Fig. 1) with  $f_S = 2f_{\text{PWM}}$ , as explained in [3], [8], and [12].

Analysis and design of current controllers are simplified by introducing complex vectors [5], [6], [10], where the stator current in stationary frame is represented by  $i^s = i_{\alpha s} + ji_{\beta s}$ , while the current in the synchronous d-q frame is  $i^e = i_d + ji_q$ . Modeling should include the computation delays, as well as modulation delays and feedback acquisition delays [1], [12]. An accurate model of the current controller is given in [8]. It includes unambiguous model of all the delays and coordinate transforms, and it does not rely on Tustin approximation. Developments described further on rely on [8] and make use of the same nomenclature.

In Fig. 5, the voltage reference calculated in an interrupt gets applied in the successive sampling period. Hence, the reference  $u_{n-1}^*$ , calculated in interrupt  $(n-1)T_S$  gets applied in interval  $[nT_S \dots (n+1)T_S]$ . Assuming that the  $e_n^s$  stands for the average value of the electromotive force over the same interval, the difference equation expressing the change of the stator current is

$$i_{n+1}^{s} = i_{n}^{s} e^{-\beta} + \frac{1 - e^{-\beta}}{R} \left( u_{n-1}^{s} - e_{n}^{s} \right)$$

(3)

where  $\beta = RT_S/L$ , while R and L are the resistance and inductance of the windings. Complex vectors in stationary and synchronous frames are related by

$$i_{n+1}^{s} = i_{n+1}^{e} \cdot e^{j\theta_{n+1}}, \quad i_{n}^{s} = i_{n}^{e} \cdot e^{j\theta_{n}},$$

$$u_{n-1}^{s} = u_{n-1}^{e} \cdot e^{j\theta_{n-1}}$$

(4)

where  $\theta_n$  represents the position of the d-q frame at instant  $nT_S$ . Assuming that the speed  $\omega_e = d\theta/dt$  does not exhibit a meaningful change in  $T_S$ , the advance of the d-q frame is  $\theta_{n+1} = \theta_n + \omega_e T_S$ ,  $\theta_n = \theta_{n-1} + \omega_e T_S$ , while the average

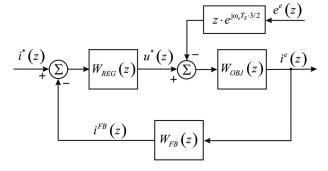

Fig. 6. Block diagram of generic current controller in synchronous d-q frame. With conventional synchronous sampling,  $W_{FB}(z) = 1$ .

value of the electromotive force becomes

$$e_n^e = \frac{1}{T} \int_{nT_S}^{(n+1)T_S} e^e(t) \cdot dt \approx e_n^s \cdot e^{-j(\theta_{n+1} + \theta_n)/2}.$$

(5)

The difference equation is obtained by introducing the results of (4) and (5) into (3), dividing the resulting expression by  $e^{j\theta n}$  and introducing  $(1 - e^{-\beta})/R \approx T_S/L$

$$i_{n+1}^{e} e^{j\omega_{e}T_{S}} = i_{n}^{e} e^{-\beta} + \frac{T_{S}}{L} \left( u_{n-1}^{e} \cdot e^{-j\omega_{e}T_{S}} - e_{n}^{e} \cdot e^{j\omega_{e}T_{S}/2} \right).$$

(6)

The transfer function of the plant is obtained by dividing the complex images  $i^e(z)$  and  $u^e(z)$ , obtained in conditions where the disturbance  $e^e(z)$  is equal to zero. From (6)

$$W_{\text{OBJ}}(z) = \left. \frac{i^{e}(z)}{u^{e}(z)} \right|_{e^{e}=0} = \frac{T_{S}}{L} \frac{1}{z \cdot e^{j\omega_{e}T_{S}} (z \cdot e^{j\omega_{e}T_{S}} - e^{-\beta})}.$$

(7)

In the presence of both  $u^{e}(z)$  and  $e^{e}(z)$ , the output current is obtained from (3), (6), and (7)

$$i^{e}(z) = W_{\rm OBJ}(z) \cdot u^{e}(z) - z \cdot e^{j\omega_{e}T_{S} \cdot 3/2} W_{\rm OBJ}(z) \cdot e^{e}(z).$$

(8)

The closed-loop current controller is given in Fig. 6. State-ofthe-art current controllers use conventional synchronous sampling with unity gain and no delays in the feedback path  $(W_{\rm FB} = 1)$ . In IMC-based design,  $W_{\rm REG}(z)$  comprises inverted dynamics of  $W_{\rm OBJ}(z)$ , and it is obtained by applying the method of [7] and [8] on  $W_{\rm OBJ}(z)$  of (7)

$$W_{\text{REGX}}(z) = \frac{\alpha z}{z-1} \cdot W_{\text{OBJ}}^{-1}$$

$$= \frac{\alpha L}{T_S} \frac{z^2 \cdot e^{j\omega_e T_S} \left(z \cdot e^{j\omega_e T_S} - e^{-\beta}\right)}{z-1}$$

where  $\alpha$  is the gain. Compared with *s*-domain implementation in [7], where  $k_p = kL$  and  $k_i = kR$ , the gain  $\alpha$  corresponds to  $kT_{\rm S}$ .

The function  $W_{\text{REGX}}(z)$  implies prediction, which cannot be implemented. Therefore, the practical controller becomes

$$W_{\text{REG}}(z) = \frac{\alpha L}{T_S} \frac{e^{j\omega_e T_S} \left(z \cdot e^{j\omega_e T_S} - e^{-\beta}\right)}{z - 1} \tag{9}$$

TABLE IV Closed-Loop Performance of State-of-the-Art Controllers

| Gain $\alpha$ | Settling time<br>(1%)   | $f_{\rm BW}\left(-45^\circ\right)$ | $f_{\rm BW}(-3{\rm dB})$ | VM    | Overshoot |

|---------------|-------------------------|------------------------------------|--------------------------|-------|-----------|

| 0.300         | 9 T <sub>S</sub>        | 0.0374 fs                          | 0.1034 fs                | 0.679 | 0.0120    |

| 0.287         | $9 T_{\rm S}$           | $0.0362 f_{\rm S}$                 | $0.0954 f_{\rm S}$       | 0.667 | 0.0053    |

| 0.277         | 9 <i>T</i> <sub>S</sub> | $0.0350 f_{\rm S}$                 | $0.0894 f_{ m S}$        | 0.655 | 0.0020    |

which leads to the open loop gain of

$$W_{\rm PP}(z) = W_{\rm REG}(z) W_{\rm OBJ}(z) = \frac{\alpha}{z(z-1)}$$

(10)

and to the closed-loop transfer function

$$W_{\rm SS}(z) = \frac{i^{e}(z)}{i^{*}(z)}\Big|_{e^{e}=0} = \frac{W_{\rm PP}(z)}{1+W_{\rm PP}(z)} = \frac{\alpha}{z^{2}-z+\alpha}.$$

(11)

The closed-loop performances obtained with  $W_{\rm SS}(z)$  of (11) are obtained analytically and given in Table IV. Considered are the step-response overshoot, the frequency  $f_{\rm BW}(-45^\circ)$  where the phase of  $W_{\rm SS}$  drops to  $-45^\circ$ , the frequency  $f_{\rm BW}(-3\,{\rm dB})$  where the amplitude of  $W_{\rm SS}$  drops to -3 dB and the settling time. The vector margin (VM) as calculated as an indicator of robustness against the changes in a system parameter. According to results in Table IV, the closed-loop bandwidth of  $f_{\rm BW}(-3\,{\rm dB}) = 0.1 \cdot f_S$  can be achieved with a very small overshoot and with the vector margin of VM = 0.67.

# B. Delays Introduced by the Feedback Averaging

Error-free feedback acquisition of (1) is based on feedback oversampling with a period of  $T_{ADC} = T_{PWM}/N_{OV}$  and then taking the average of  $N_{OV}$  samples, acquired within the past period  $T_{PWM}$ . The value  $i^{FB}$  at instant  $nT_S$  (see Fig. 5) represents the average of the current over the interval  $[(n-2)T_S \dots nT_S]$ . It can be expressed in terms of the current samples  $i_{n-2}$ ,  $i_{n-1}$ and  $i_n$  as  $i_n^{FB} = (i_n + 2i_{n-1} + i_{n-2})/4$ . The transfer function in the feedback path becomes

$$W_{\rm FB}(z) = \frac{i^{\rm FB}(z)}{i(z)} = \frac{z^2 + 2 \cdot z + 1}{z^2}.$$

(12)

Delays introduced by  $W_{\rm FB}$  into the feedback path affect the closed-loop transfer function  $W_{\rm SS}$ . Assuming that the system is controlled using the same controller  $W_{\rm REG}$  (9), the closed-loop transfer function  $W_{\rm SS}$  is obtained from the diagram in Fig. 6

$$W_{\rm SS}(z) = \frac{W_{\rm REG}(z) \cdot W_{\rm OBJ}(z)}{1 + W_{\rm REG}(z) \cdot W_{\rm OBJ}(z) \cdot W_{\rm FB}(z)}$$

$$= \frac{4\alpha z^2}{4z^4 - 4z^3 + \alpha z^2 + 2\alpha z + \alpha}.$$

(13)

Due to delays introduced by  $W_{\rm FB}$ , the gain  $\alpha = 0.3$  introduces an overshoot of 25% and reduces the vector margin down to 0.5 (see Table V). In order to maintain the overshoot and the vector margin at the previous levels, it is necessary to reduce the feedback gain. Table V presents the summary of analytical considerations. For the same VM and the same overshoot, it proves VUKOSAVIĆ et al.: AC CURRENT CONTROLLER WITH ERROR-FREE FEEDBACK ACQUISITION SYSTEM

| Gain $\alpha$ | Settling time (1%) | $f_{\rm BW} \left(-45^\circ\right)$ | $f_{\rm BW} \left(-3  {\rm dB}\right)$ | VM    | Overshoot |

|---------------|--------------------|-------------------------------------|----------------------------------------|-------|-----------|

| 0.300         | $9 T_{\rm S}$      | $0.042 f_{\rm S}$                   | 0.1110 fs                              | 0.507 | 0.251     |

| 0.182         | $9 T_{\rm S}$      | $0.0274 f_{\rm S}$                  | $0.0608 f_{\rm S}$                     | 0.695 | 0.0198    |

| 0.170         | $9 T_{\rm S}$      | $0.0258 f_{\rm S}$                  | $0.0545 f_{\rm S}$                     | 0.714 | 0.0077    |

| 0.164         | $9 T_{\rm S}$      | $0.0246 f_{\rm S}$                  | $0.0509 f_{\rm S}$                     | 0.724 | 0.0038    |

TABLE V

CLOSED-LOOP PERFORMANCE WITH PROPOSED AVERAGING

AND NO D-ACTION

necessary to reduce the gain down to 60%, with roughly proportional reduction of the closed-loop bandwidth  $f_{\rm BW}(-3 \, {\rm dB})$ . Hence, the feedback delay introduced by the proposed feedback averaging produces a considerable reduction of the closed-loop performances.

#### C. Enhanced Controller

Delays in feedback acquisition can be compensated by changing the transfer function of the current controller. Current control law  $W_{\text{REG}}$  in (9) is designed to cancel the undesired dynamics of the plant ( $W_{\text{OBJ}}$ ). Therefore, it comprises inverted dynamics of  $W_{\text{OBJ}}(z)$ . In order to maintain the proper cancelation of the plant dynamics, the control law should be changed by introducing a multiplicative factor

$$W_{\text{REG}}^{\text{NEW}}(z) = W_{\text{REG}}^{\text{OLD}}(z) \cdot W_{\text{MUL}}(z).$$

(14)

In order to improve the phase and compensate time delays, the factor  $W_{MUL}$  has to be of differential nature, with

$$W_{\rm MUL}(z) = 1 + d \frac{z - 1}{z}$$

(15)

where d is adjustable parameter, the current controller is enhanced with differential action, and it has the transfer function  $W_{\text{REGD}}$

$$W_{\text{REGD}}(z) = \frac{\alpha L}{T_S} \frac{z + d(z-1)}{z} \left( \frac{e^{j\omega_e T_S} \left( z \cdot e^{j\omega_e T_S} - e^{-\beta} \right)}{z-1} \right)$$

$$= \frac{\alpha L}{T_S} e^{j\omega_e T_S} \frac{\left[ (d+1) \, z - d \right] \left( z \cdot e^{j\omega_e T_S} - e^{-\beta} \right)}{z \, (z-1)}.$$

(16)

Considering the block diagram of the current controller in Fig. 6, the closed-loop transfer function obtained with the proposed feedback averaging and the enhanced current controller of (16) is eqn. (17), at the bottom of the page.

The closed-loop performance of  $W_{\rm SS}$  in (17) depends on two parameters,  $\alpha$  and d. It is necessary to obtain the pair of parameters ( $\alpha$ , d), which improves the performance features of Table V, and brings them to those of Table IV, obtained without the proposed feedback averaging. Two-dimensional ( $\alpha$ , d) plane is searched, using the following criteria.

TABLE VI PERFORMANCE WITH FEEDBACK AVERAGING AND  $W_{\rm REGD}$  Controller

| Gain $\alpha$ | Gain d | Settling<br>time (1%) | $f_{\rm BW} \left(-45^\circ\right)$ | $f_{\rm BW} \left(-3  {\rm dB}\right)$ | VM    | Overshoot |

|---------------|--------|-----------------------|-------------------------------------|----------------------------------------|-------|-----------|

| 0.2238        | 0.555  | $8 T_{\rm S}$         | 0.0366 f <sub>S</sub>               | $0.0895 f_{\rm S}$                     | 0.643 | 0.0047    |

| 0.2283        | 0.641  | $9 T_{\rm S}$         | $0.0378 f_{\rm S}$                  | $0.0963 f_{\rm S}$                     | 0.637 | 0.0000    |

| 0.2373        | 0.638  | $9 T_{ m S}$          | $0.0394 f_{\rm S}$                  | $0.1042f_{\rm S}$                      | 0.624 | 0.0100    |

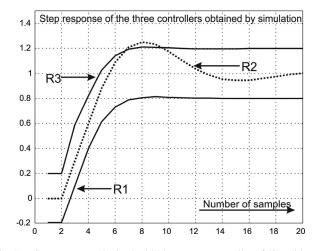

Fig. 7. Step response obtained with the current controller of [8], with conventional synchronous sampling and with  $f_{\rm BW} = 0.1 \cdot f_S$  is denoted by R1. Response obtained from (13), with feedback averaging but with no controller enhancement is denoted by R2. Response obtained with feedback averaging and with enhanced controller is denoted by R3. Response R1 is shifted vertically by 0.4 downward, to enable a better comparison.

- 1) Limit values: VM > 0.6, Overshoot < 1%.

- 2) Fixed targets: VM = 0.65, Overshoot = 0%.

- 3) Variable target:  $f_{BW}(-3 dB) = [0.08 \cdot f_S \dots 0.12 \cdot f_S].$

In Table VI, performance parameters are given for the three characteristic parameter sets. The values demonstrate that VM,  $f_{\rm BW}$ , settling time, and overshoot features obtained with the proposed feedback averaging and an enhanced controller correspond to performances of the state-of-the-art controllers, listed in Table IV. The values of  $\alpha$  and d in Table VI are relative, and they do not depend on the motor or the grid parameters.

Simulated step responses of the three current controllers are given in Fig. 7. The controller proposed in [8] is tuned for  $f_{\rm BW}(-3 \,\mathrm{dB}) = 0.1 \cdot f_S$ . Corresponding step response is denoted by R1. Using the same gain setting, the proposed averaging technique is introduced into the feedback path, while keeping the same controller of [8]. The relevant trace in Fig. 7 is R2. Eventually, the step response R3 is obtained with the feedback averaging and the enhanced controller, using the gain setting which results in  $f_{\rm BW}(-3 \,\mathrm{dB}) = 0.1 \cdot f_S$ . The traces in Fig. 7 show that the feedback averaging introduces delays and deteriorates the step response. They also prove that the extended controller  $W_{\rm REGD}$  of (16) restores the closed-loop performance,

$$W_{\rm SS}(z) = \frac{W_{\rm REGD}(z) \cdot W_{\rm OBJ}(z)}{1 + W_{\rm REGD}(z) \cdot W_{\rm OBJ}(z) \cdot W_{\rm FB}(z)} = \frac{4\alpha (1+d) z^3 - 4\alpha dz^2}{4z^5 - 4z^4 + \alpha (1+d) z^3 + \alpha (2+d) z^2 + \alpha (1-d) z - \alpha d}.$$

(17)

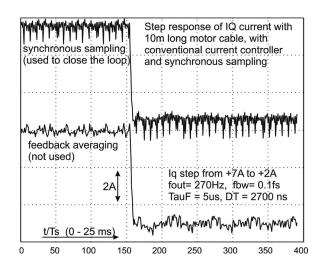

Fig. 8. Step response obtained with state-of-the-art controller, synchronous sampling,  $\alpha = 0.3$ , and with l = 10-m-long motor cable. The upper trace is obtained by synchronous sampling and used to close the loop. Elevated noise is due to the sampling errors being amplified by the loop gains. The lower trace is obtained by averaging (1)–(2), and it is not used to close the feedback.

providing the step response which is very close to the one obtained with state-of-the-art controller [8] and with conventional sampling.

#### IV. EXPERIMENTAL TESTS WITH ENHANCED CONTROLLER

Experimental study of the sampling errors is given in Section II, Tables I–III, and Figs. 2–4. The proposed feedback acquisition technique (1)–(2) removes the errors and introduces the transfer function  $W_{\rm FB}$  (12) into the feedback path. In order to maintain the closed-loop performance, the current controller has to be extended as shown in (16). The subsequent experimental tests are performed in order to explore the capability of the enhanced controller to maintain the closed-loop performance in the presence of feedback averaging (1)–(2).

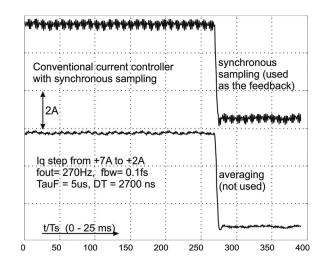

With conventional current controller and synchronous sampling, the step response obtained with a 10-m-long motor cable is shown in Fig. 8. In Figs. 8–11, the two traces are logged simultaneously, during the same run. The upper traces are obtained with conventional synchronous sampling, while the lower traces are obtained from (1) to (2), by the proposed feedback averaging. In Fig. 8, the upper trace is used as the feedback signal. Increased errors are due to interaction of the sampling errors and relatively high loop gains.

For the proper comparison of dynamic performance of the conventional and the proposed current controller, it is convenient to perform the tests in low-noise conditions. Therefore, the step response test of the conventional controller [8] is repeated with no motor cable and with reduced  $t_{DT}$  and  $\tau_{\rm LPF}$ . The results are given in Fig. 9, demonstrating the closed-loop bandwidth of  $f_{\rm BW} = 0.1 f_S$  with a very low overshoot.

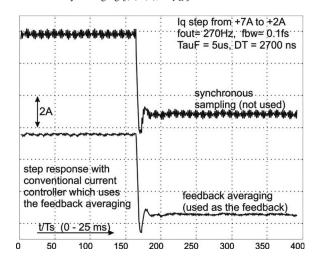

The sampling errors are reduced by introducing the described feedback averaging (1)–(2), modeled by  $W_{\rm FB}$  in (12). It provides a considerable reduction of the noise content in the feedback signals (see Figs. 2–4, Tables I–III). It also introduces delay into the loop (see Fig. 6). The step response obtained with a conven-

Fig. 9. Step response obtained with state-of-the-art controller, synchronous sampling and  $\alpha = 0.3$ . Lower sampling errors are obtained by reducing  $t_{\rm DT}$  and  $\tau_{\rm LPF}$  and using short leads instead of shielded motor cable. The upper trace is obtained by synchronous sampling and is used to close the loop. The lower trace is obtained by averaging [(1)–(2),  $W_{\rm FB}$ ]. It is not used as the feedback.

Fig. 10. Step response obtained with conventional current controller and with the feedback averaging of (1)–(2). The upper trace is obtained by synchronous sampling and it is not used as the feedback. The lower trace is obtained by averaging [(1)–(2),  $W_{\rm FB}$ ], and it is used as the feedback signal.

Fig. 11. Step response obtained with the feedback averaging and with enhanced current controller. The lower, averaged trace is used as the feedback signal, while the upper, synchronous-sampled trace is given for the reference.

Fig. 12. Comparison of the step response features of the conventional current controller which uses the synchronous sampling (upper trace) and the enhanced current controller with the feedback averaging (lower trace). Both traces are obtained in the same way, by the averaging proposed in (1)–(2). The waveforms are intentionally shifted to facilitate comparison.

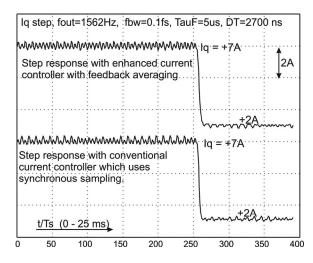

Fig. 13. Comparison of the step responses obtained with a high output frequency of 1562 Hz (that is,  $0.1 f_S$ ). For the purposes of comparison, both traces are obtained in the same way, by the averaging proposed in (1)–(2).

tional controller [8], which uses the feedback averaging (1)–(2), is given in Fig. 10. The role of the two shown signals, with regard to the use in the control, is now reversed when compared to the results in Figs. 8–9. Feedback acquisition delays produce a relatively large overshoot, which corresponds to simulation results given in Fig. 7.

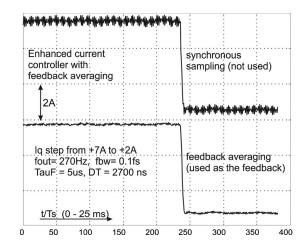

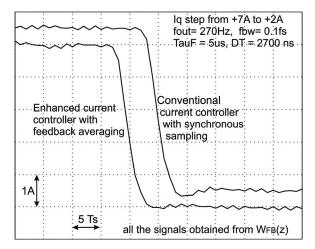

Enhanced controller  $W_{\text{REGD}}$  of (16) has a multiplicative factor of differential nature. The values of design parameter *d*, which can restore dynamic performances are listed in Table VI. The step response obtained with an enhanced current controller that uses the feedback averaging are given in Fig. 11. Corresponding gains  $\alpha$  and *d* are set to achieve  $f_{\text{BW}} = 0.1 f_S$ . The waveforms of Fig. 11 are very similar to those in Fig. 9, proving the capability of the enhanced controller to use the error-free feedback acquisition of (1)–(2) and yet to obtain the same level of the closed-loop performances as the state-of-theart controllers, based on synchronous sampling. In Fig. 12, the

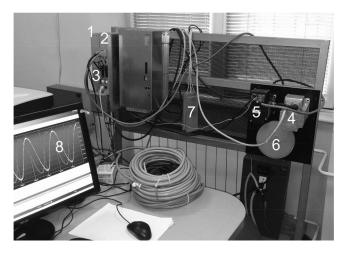

Fig. 14. Experimental setup with six-pole synchronous permanent-magnet motor. (1) Main power supply unit providing  $E_{\rm DC} = 520$  V. (2) Two-axis module comprising two 3-phase inverters and control circuits. (3) SD-card slot used for data logging. (4) The motor under the test. (5) Speed-controlled motor. (6) Inertia coupled by a toothed belt with the two motors. (7) Dynamic braking resistors. (8) PC-based GUI connected over the EtherCat link.

step responses obtained with the two controllers are zoomed in and aligned for the ease of comparison.

An important feature of the current controller is the capability to maintain the response quality even with very large output frequencies. The current controller of [8] shows an excellent performance even with  $f_{OUT} = 0.083 f_S$ . In order to verify the proposed controller, it is compared to the former in Fig. 13, where the two step responses are compared at the output frequency of  $f_{OUT} = 0.1 f_S$ . The experiment is carried out by using three inductances as the load. The basic features of the two responses are similar, proving the possibility to obtain an error-free feedback acquisition, while maintaining at the same time a superior dynamic performance.

# V. CONCLUSION

In this paper, we consider the errors encountered in the feedback path of state-of-the-art digital ac current controllers. Most recent solutions use synchronous sampling, wherein a single sample of the current is taken at the center of the voltage pulses. Experimental investigation reported in the paper includes the impact of the lockout time and the effects of delays introduced by anti-aliasing filters. We also considered the sampling errors introduced by parasitic oscillations. These oscillations are created in an interaction of fast switching transients and parasitic LC elements of the motor cables and/or the winding capacitance. The sampling errors from 2% up to 7% introduce considerable disturbance and they limit the feedback gains and performances of the current controller.

In order to suppress the errors in the feedback path, we developed a feedback acquisition technique. In each half of the PWM cycle, an average value of the feedback is calculated within the past PWM cycle. The process is aided by automated DMAdriven ADC sequences of contemporary DSP controllers. The method removes all the sampling errors caused by the lock-out time, and anti-aliasing filter delays, and it features an infinite attenuation of the switching ripple. It also reduces the errors introduced by parasitic *LC* oscillations. In cases where the motor cables increase the errors by 5% with conventional synchronous sampling, the errors are increased by only 0.2% with the proposed feedback averaging.

The feedback averaging introduces delays, overshoots and deteriorates the closed-loop response. In order to maintain dynamic performances, the current controller is enhanced by proposing a series compensator and the parameter setting that are focused on maintaining the same dynamic performances and robustness as the state-of-the-art solutions. Proposed control solutions are verified by simulations and experimental runs performed on DSP-controlled setup with synchronous permanent magnet motor and IGBT inverter.

#### APPENDIX

The experimental setup is shown in Fig. 14. Rotor-fluxoriented control is used at all times.

| Stack length              | L = 128  mm                                       |

|---------------------------|---------------------------------------------------|

| Number of poles           | 2p = 6                                            |

| Rated torque              | $T_{n  \mathrm{o}  \mathrm{m}} = 6  \mathrm{Nm}$  |

| Rated current             | $I_{\rm nom} = 7.3$ Arms                          |

| Torque constant           | $k_t = 0.821 \text{ N·m/A}_{\text{rms}}$          |

| Back-EMF constant         | $k_e = 0.687 \mathrm{V}_{\mathrm{peak}}$ /(rad/s) |

| Stator resistance         | $R_S = 0.47 \ \Omega$                             |

| Stator inductance         | $L_S = (L_d + L_q)/2 = 3.4 \text{ mH}$            |

| PWM inverter              |                                                   |

| DC-bus voltage            | $E_{\rm DC}=520~{ m V}~{ m dc}$                   |

| PWM frequency             | $f_{\rm PWM} = 1/T_{\rm PWM} = 7.812 \text{ kHz}$ |

| Rated lockout time        | $t_{DT} = 3 \ \mu s$                              |

| Peak current              | $I_{\rm max} = 45$ A                              |

| Digital control platform  |                                                   |

| DSP controller            | TMS320F28335                                      |

| ADC resolution            | $N_{ADC} = 12 - \text{bit}$                       |

| Anti-aliasing LPF         | $\tau_{\rm LPF} \ge 5 \ \mu s$                    |

| Oversampling period       | $T_{A D C} = 4 \ \mu s$                           |

| Oversampling handle       | embedded DMA machine                              |

| No. of samples per period | $N_{\rm OV} = T_{\rm PWM} / T_{\rm ADC} = 32$     |

| PWM method                | Symmetrical PWM                                   |

#### REFERENCES

- D. G. Holmes, B. P. McGrath, and S. G. Parker, "Current regulation strategies for vector-controlled induction motor drives," *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3680–3689, Oct. 2012.

- [2] E. Levi, "FOC: Field oriented control," in *The Industrial Electronics Handbook, (Power Electronics and Motor Drives)*, 2nd ed. Boca Raton, FL, USA: CRC Press, 2011.

- [3] J.-W. Choi and S.-K. Sul, "New current control concept—Minimum time current control in the three-phase PWM converter," *IEEE Trans. Power Electron.*, vol. 12, no. 1, pp. 124–131, Jan. 1997.

- [4] J.-W. Choi and S.-K. Sui, "Fast current controller in three-phase AC/DC boost converter using d-q axis crosscoupling," *IEEE Trans. Power Electron.*, vol. 13, no. 1, pp. 179–185, Jan. 1998.

- [5] F. Briz, M. Degner, and R. Lorenz, "Analysis and design of current regulators using complex vectors," *IEEE Trans. Ind. Appl.*, vol. 36, no. 3, pp. 817–825, May/Jun. 2000.

- [6] F. Briz, M. Degner, and R. Lorenz, "Dynamic analysis of current regulators for AC motors using complex vectors," *IEEE Trans. Ind. Appl.*, vol. 35, no. 6, pp. 1424–1432, Nov./Dec. 1999.

- [7] L. Harnefors and H. P. Nee, "Model-based current control of AC machines using the internal model control method," *IEEE Trans. Ind. Appl.*, vol. 34, no. 1, pp. 133–141, Jan./Feb. 1998.

- [8] H. Kim, M. Degner, J. Guerrero, F. Briz, and R. Lorenz, "Discrete-time current regulator design for AC machine drives," *IEEE Trans. Ind. Appl.*, vol. 46, no. 4, pp. 1425–1435, Jul./Aug. 2010.

- [9] B.-H. Bae and S.-K. Sul, "A compensation method for time delay of full digital synchronous frame current regulator of PWM AC drives," *IEEE Trans. Ind. Appl.*, vol. 39, no. 3, pp. 802–810, May/Jun. 2003.

- [10] J. Holtz, J. Quan, J. Pontt, J. Rodriguez, P. Newman, and H. Miranda, "Design of fast and robust current regulators for high-power drives based on complex state variables," *IEEE Trans. Ind. Appl.*, vol. 40, no. 5, pp. 1388–1397, Sep./Oct. 2004.

- [11] J.-S. Yim, S.-K. Sul, B.-H. Bae, N. Patel, and S. Hiti, "Modified current control schemes for high-performance permanent-magnet AC drives with low sampling to operating frequency ratio," *IEEE Trans. Ind. Appl.*, vol. 45, no. 2, pp. 763–771, Mar./Apr. 2009.

- [12] D. G. Holmes, T. A. Lipo, B. McGrath, and W. Kong, "Optimized design of stationary frame three phase AC current regulators," *IEEE Trans. Power Electron.*, vol. 24, no. 11, pp. 2417–2426, Nov. 2009.

- [13] H.-T. Moon, H.-S. Kim, and M.-J. Youn, "A discrete-time predictive current control for PMSM," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 464–472, Jan. 2003.

- [14] A. G. Yepes, A. Vidal, J. Malvar, O. Lopez, and J. D. Gandoy, "Tuning method aimed at optimized settling time and overshoot for synchronous proportional-integral current control in electric machines," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 3041–3054, Jun. 2014.

- [15] S. H. Song, J. W. Choi, and S. K. Sul, "Current measurements in digitally controlled ac drives," *IEEE Ind. Appl. Mag.*, vol. 6, no. 4, pp. 51–62, Jul./Aug. 2000.

- [16] C. E. Shannon, "Communication in the presence of noise," *Proc. IEEE*, vol. 86, no. 2, pp. 447–457, Feb. 1998.

- [17] E. Monmasson, Ed., Power Electronic Converters: PWM Strategies and Current Control. Hoboken, NJ, USA: Wiley, 2011.

- [18] K. Ogata, *Modern Control Engineering*. Englewood Cliffs, NJ, USA: Prentice-Hall, 2009.

- [19] A. Said and A. H. Kamal, "A modeling technique to analyze the impact of inverter supply voltage and cable length on industrial motordrives," *IEEE Trans. Power Electron.*, vol. 23, no. 2, pp. 753–762, Mar. 2008.

- [20] DS2000 Data Manual, MOOG Italiana S.r.l., Casella, Italy, 2005.

- [21] DM2020 Data Manual, MOOG Italiana S.r.l., Casella, Italy, 2011.

**Slobodan N. Vukosavić** (M'93–SM'12) was born in Sarajevo, Serbia, in 1962. He received the B.S., M.S., and Ph.D. degrees from the University of Belgrade, Belgrade, Serbia, in 1985, 1987, and 1989, respectively, all in electrical engineering.

He was with Nikola Tesla Institute, Belgrade, Serbia, until 1988, when he joined the ESCD Laboratory, Emerson Electric, St. Louis, MO, USA. Since 1991, he has been a consultant with Vickers Electric Company, Milan, Italy, and MOOG Electric, USA, since 1994. He is currently a Professor with the University

of Belgrade. His current research interests include digital control, power conversion in renewable energy sources, and power quality. He has authored or co-authored over 70 papers, 3 textbooks, and 7 monographs, and has completed over 40 large research and development and industrial projects. VUKOSAVIĆ et al.: AC CURRENT CONTROLLER WITH ERROR-FREE FEEDBACK ACQUISITION SYSTEM

**Ljiljana S. Perić** received the B.S. degree in electrical engineering from the Department of Electrical Engineering, University of Belgrade, Belgrade, Serbia, in 1989.

She joined the El industry in Belgrade. Since 1996, she has been with FSU-El, Belgrade, involved in designing and manufacturing of signal and power electronics equipment for the railway safety and control. She is currently the owner and R/D Manager of Ariom Ltd., Belgrade, providing design and consultancy services in power electronics and digital control. She

has authored or co-authored eight papers and completed 12 industrial R&D projects.

**Emil Levi** (S'89–M'92–SM'99–F'09) received the M.Sc. and Ph.D. degrees in electrical engineering from the University of Belgrade, Belgrade, Serbia, in 1986 and 1990, respectively.

From 1982 to 1992, he was with the Department of Electrical Engineering, University of Novi Sad, Novi Sad, Yugoslavia. He joined Liverpool John Moores University, Liverpool, U.K., in May 1992, and since September 2000, he has been a Professor of Electric Machines and Drives.

Dr. Levi was the Co-Editor-in-Chief of the IEEE

TRANSACTIONS ON INDUSTRIAL ELECTRONICS from 2009 until 2013 and is an Editor of the IEEE TRANSACTIONS ON ENERGY CONVERSION. He is the Editor-in-Chief of *IET Electric Power Applications*. He is the recipient of the Cyril Veinott Award of the IEEE Power and Energy Society for 2009. In 2014, he received the Outstanding Achievement Award from the European Power Electronics Association.