# An assessment of RTN-induced threshold voltage jitter

Jian Fu Zhang\*, Azrif Manut, Rui Gao, Mehzabeen Mehedi, Zhigang Ji, Weidong Zhang, and John Marsland

> Department of Electronics and Electrical Engineering, Liverpool John Moores University, Byrom Street, Liverpool L3 3AF, UK \* Email: j.f.zhang@ljmu.ac.uk

# Abstract

Power consumption is a key issue especially for the edge devices/units in an IoT system. Lowering operation voltage is an effective way to reduce power. As the overdrive voltage, Vg-Vth, becomes smaller, the device is more vulnerable to threshold voltage jitters. One source for the jitter is Random Telegraph Noises (RTN), which cause a fluctuation in both drain current,  $\Delta Id$ , and threshold voltage,  $\Delta V$ th. Early works on RTN were focused on measuring  $\Delta Id$  and then evaluate  $\Delta Vth$  from  $\Delta Id/gm$ , where gm is transconductance. The accuracy of  $\Delta$ Vth obtained in this way is not known. The objective of this work is to assess its accuracy by comparing it with the  $\Delta$ Vth directly measured from pulse Id-Vg. It will be shown that the correlation between these two is poor, so that  $\Delta V$ th must not be evaluated from  $\Delta Id/gm$ . This is caused by the device-specific localized current distribution near the threshold.

# 1. Introduction

The instabilities of modern MOSFETs have a number of sources: bias temperature instabilities (BTI) [1-7], hot carrier ageing (HCA) [8-10], and random telegraph noise [11-17]. To increase the instabilities and make them measurable, it is a common practice to use voltage-acceleration [1-10]. This works well for both BTI and HCA and the threshold voltage shift,  $\Delta$ Vth, has been reliably measured at pre-specified time by the measure-stress-measure (MSM) technique [1-10].

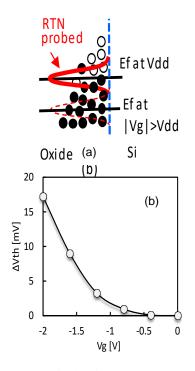

The MSM technique, however, is inapplicable for the RTN-induced jitter in Vth because of two reasons. First, RTN is dominated by traps near the Fermi-level at the dielectric/substrate interface Ef, as shown in Fig. 1a. Although Fig. 1b shows that there are more traps at high |Vg|, Vg-acceleration shifts Ef, so that RTN would be dominated by a different group of traps under Vg-acceleration. Second, the charging-discharging of traps responsible for RTN is highly dynamic in nature. At a pre-specified time, they can be neutral and would be missed if the MSM technique is used.

Because of these difficulties, early works [12,13] focus on measuring the fluctuation in drain current,  $\Delta Id$ , under a fixed Vg. This on-the-fly (OTF)  $\Delta Id$  is then converted to  $\Delta V$ th by dividing the transconductance, gm. The accuracy of this  $\Delta V$ th-OTF is not clear, as it was not compared with the real  $\Delta V$ th measured at Vg=Vth. The objective of this work is to assess the accuracy of  $\Delta V$ th-OTF and analyse the source of discrepancies between the  $\Delta V$ th-OTF and the real  $\Delta V$ th.

## 2. Devices and experiments

The devices were fabricated by a 28 nm CMOS process with channel length and width of 27 nm and 90 nm, respectively. The high-k dielectric stack has an equivalent oxide thickness of 1.2 nm and metal gate. To minimize the trap discharge, pulse Id-Vg (p-IV) was taken and the measurement time is 3  $\mu$ s. Vth was evaluated by using the maximum gm (Max-gm) method. The  $\Delta$ Vth-OTF was evaluated from the  $\Delta$ Id/gm at |Vg|= 1 V. The temperature is 125 °C.

Fig. 1. (a) RTN is dominated by traps near to Ef at the interface. Vg-acceleration shifts Ef and changes the traps probed by RTN. (b) More traps under higher |Vg| result in higher  $\Delta V$ th.

#### 3. Results and discussions

We start with a large device of  $1 \times 3 \mu m$ , where the device-to-device variation is insignificant. The two p-IVs before and after charging are given in Fig. 2a and the  $\Delta$ Vth evaluated from their differences at constant Id is plotted in Fig. 2b. The  $\Delta$ Vth-OTF and the  $\Delta$ Vth-Max-gm are shown by the two dashed lines. The  $\Delta$ Vth-OTF agrees well with the  $\Delta$ Vth when Vg is close to -1 V in the region 'A', while the  $\Delta$ Vth-Max-gm agrees with the  $\Delta$ Vth when Vg is close to the Vth of -0.45 V in the region 'B'.

Fig. 2. (a) The pulse IVs before and after charging of a large device  $(1 \times 3 \mu m)$ . (b)  $\Delta V$ th evaluated from constant Id under different Vg. The top dashed line is  $\Delta V$ th-OTF evaluated from  $\Delta Id/gm$  at Vdd=-1 V. The bottom dashed line is  $\Delta V$ th extracted from the max-gm.

$\Delta$ Vth-OTF is twice of  $\Delta$ Vth-Max-gm in Fig. 2b. As a result,  $\Delta$ Vth-OTF should not be used as a substitute for the real  $\Delta$ Vth. For SRAM, MOSFETs operate close to Vth near the trip-point and the  $\Delta$ Vth affects its noise margin [14,16]. For digital circuits, MOSFETs go through Vth during the switching and an increase of |Vth| causes delay. As a result, it is important to analyse the sources of the discrepancies between  $\Delta$ Vth-OTF and  $\Delta$ Vth-Max-gm. One source is the mobility degradation, which was neglected in evaluating  $\Delta$ Vth-OTF. In the following, we will use nano-scale devices to show that the current distribution also contributes to the discrepancies.

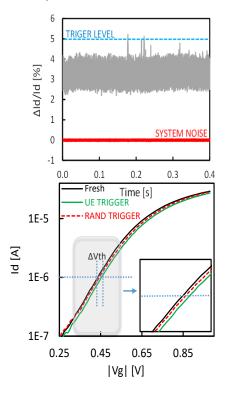

Unlike large devices, RTN causes a substantial fluctuation in Id, as shown in Fig. 3a. As mentioned earlier, if the p-IV was taken at pre-specified time, some traps are neutral and will be missed and one example is given in Fig. 3b. To ensure capturing the trapped charges, the trigger level of the oscilloscope must be adjusted so that it only triggers when the traps are charged, as shown in Fig. 3a. The inset of Fig. 3b illustrates that this method improves the measurement accuracy substantially.

Fig. 3. (a) The p-IV trigger level is set to capture the trapped charges. (b) A comparison between the p-IV(trigger-when-charged) (green line) with the p-IV(trigger-at-pre-specified-time) (dashed red line).

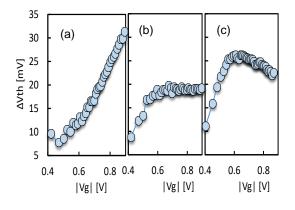

Figs. 4a-c show the results from three different devices. The device-to-device variation (DDV) is substantial. In Fig. 4a, the  $\Delta$ Vth-OTF at Vg= -1 V is ~4 times of the  $\Delta$ Vth at Vg=Vth=-0.45 V, so that the discrepancy is much larger than that of large devices in Fig. 2b. Fig. 4b shows that  $\Delta$ Vth saturates as |Vg| increases, in contrast with the monotonic increase in Fig. 2b. Moreover, Fig. 4c shows that  $\Delta$ Vth turns around: it increases initially and then decreases for higher |Vg|. This turn-around behaviour cannot be explained by charge-induced mobility degradation and other mechanisms must be involved.

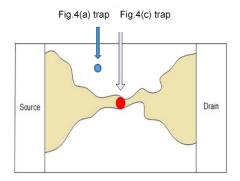

It has been reported that the current path near to Vth is localized, but becomes more evenly distributed as

|Vg-Vth| increases. The impact of a charged trap on Vth depends on the current density beneath it: the higher the current density, the larger the impact [17,18]. As illustrated in Fig. 5, the trap for Fig. 4a is away from the localized current path at Vth. As |Vg-Vth| increases, a more evenly distributed current increases the relative local current density, so that the  $\Delta V$ th increases in Fig. 4a. For Fig. 4c, the trap can be above the localized current path at Vth. As |Vg-Vth| increases, the initial rise is caused by increased mobility degradation and the subsequent decrease is caused by the relative reduction of current density under this trap, as the distribution spreads. The result of large device in Fig. 2b is the average results of small devices. Under Vth, localization of current path leads to many traps being away from it, so that the impact on  $\Delta V$ th is low. As |Vg-Vth increases, the effect of these traps increases, contributing the higher  $\Delta V$ th for higher |Vg-Vth|.

Fig. 4. The dependence of  $\Delta V$ th on sensing Vg for three nano-scale devices. (a)  $\Delta V$ th increases with |Vg|. (b)  $\Delta V$ th saturates. (c)  $\Delta V$ th turns around.

Fig. 5. The localized current path at Vg=Vth. The trap in Fig. 4a is away from the path, while the trap in Fig. 4c is above it.

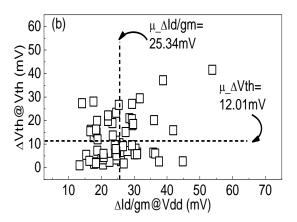

The correlation between the  $\Delta$ Vth-Max-gm and  $\Delta$ Id/Id-OTF is given in Fig. 6. The poor correlation between them confirms that  $\Delta$ Id/Id-OTF should not be

used to evaluate the  $\Delta V$ th.

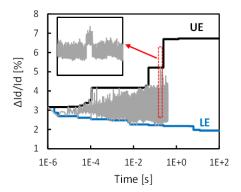

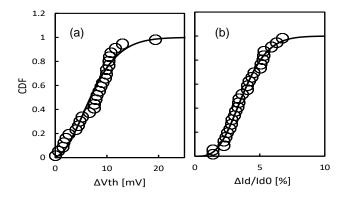

Fig. 7 shows that the  $\Delta$ Id/Id against measurement time. Longer time allows slower traps to respond, leading to higher up-envelope (UE). The DDV of  $\Delta$ Id/Id and  $\Delta$ Vth are given in Figs. 8a&b, respectively and both of them are substantial. Figs. 9a&b show that the statistical distribution follows the defect-centric model well [19].

Fig. 6. The poor correlation  $\Delta Id/gm$  and the  $\Delta V$ th-Max-gm. [17]

Fig. 7. Larger time window captures slower traps, leading to higher up-envelope (UE).

### 4. Conclusions

$\Delta$ Vth-OTF measured under Vdd is compared with the real  $\Delta$ Vth extracted by maximum-gm method. On average the former is twice of the latter. This discrepancy is caused not only by the increased mobility degradation for higher |Vg-Vth|, but also caused by a more evenly distributed current. The RTN-induced device-to-device variations follow the defect-centric model for both  $\Delta$ Id/Id and  $\Delta$ Vth. There is a poor correlation between  $\Delta$ Id/Id-OTF and  $\Delta$ Vth.

#### Acknowledgments

The authors would like to thank A. Asenov of Glasgow University, D. Vigar of CSR, and B. Kaczer of IMEC for

useful discussions. The test samples were supplied by D. Vigar. This work is supported by EPSRC of UK under the grant no. EP/L010607/1.

Fig. 8. The device-to-device variations of (a)  $\Delta$ Id/Id-OTF and (b)  $\Delta$ Vth-Max-gm.

Fig. 9. The statistical distribution follows Defect-centric model (Lines) (a)  $\Delta$ Vth-Max-gm and (b)  $\Delta$ Id/Id-OTF.

#### References

- J. F. Zhang, Z. Ji, and W. Zhang, Microelectronics Reliability, 80, p.109 (2018).

- [2] Z. Q. Teo, D. S. Ang, and K. S. See, iedm, p.737 (2009).

- [3] T. Grasser M. Waltl, Y. Wimmer, W. Goes, R. Kosik, G. Rzepa, H. Reisinger, G. Pobegen, A. El-Sayed, A.

Shluger, and B. Kaczer, iedm, p.535 (2015).

- [4] P. Ren R. Wang, Z. Ji, P. Hao, X. Jiang, S. Guo, M. Luo, M. Duan, J. F. Zhang, J. Wang, J. Liu, W. Bu, J. Wu, W. Wong, S. Yu, H. Wu, S. W. Lee, N. Xu, and R. Huang, iedm, p.816 (2014).

- [5] Z. Ji, S. F. W. M. Hatta, J. F. Zhang, J. G. Ma, W. Zhang, N. Soin, B. Kaczer, S. De Gendt, and G. Groeseneken, iedm, p.413 (2013).

- [6] R. Gao, A. B. Manut, Z. Ji, J. Ma, M. Duan, J. F. Zhang, J. Franco, S. W. M. Hatta, W. Zhang, B. Kaczer, D. Vigar, D. Linten, and G. Groeseneken, IEEE Trans. Elec, Dev., 64, p.1467 (2017).

- [7] J. F. Zhang, M. H. Chang, Z. Ji, L. Lin, I. Ferain, G. Groeseneken, L. Pantisano, S. De Gendt, and M. M. Heyns, IEEE Electron Device Letters, 29, p.1360 (2008).

- [8] M. Duan, J. F. Zhang, A. Manut, Z. Ji, W. Zhang, A. Asenov, L. Gerrer, D. Reid, H. Razaidi, D. Vigar, V. Chandra, R. Aitken, B. Kaczer, and G. Groeseneken iedm, p.547, 2015.

- [9] M. Duan, J. F. Zhang, Z. Ji, W. Zhang, D. Vigar, A. Asenov, L. Gerrer, V. Chandra, R. Aitken, and B. Kaczer, IEEE Trans. Elec, Dev., 63, p. 3642 (2016).

- [10] M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, and A. Asenov, IEEE Trans. Elec, Dev., 64, p.2478 (2017).

- [11] R. Wang, S. Guo, Z. Zhang, Q. Wang, D. Wu, J. Wang, R. Huang, iedm, p.388, (2018).

- [12] H. Miki, M. Yamaoka, N. Tega, Z. Ren, M. Kobayashi, C. P. D'Emic, Y. Zhu, D. J. Frank, M. A. Guillorn, D.-G. Park, W. Haensch\*, and K. Torii, VLSI Tech. Symp, p.148 (2011).

- [13] K. Ota, M. Saitoh, C. Tanaka, D. Matsushita, and T. Numata, VLSI Tech. Symp., p.54 (2014).

- [14] M. Duan, J. F. Zhang, Z. Ji, J. G. Ma, W. Zhang, B. Kaczer, T. Schram, R. Ritzenthaler, G. Groeseneken, and A. Asenov, iedm, p. 774 (2013).

- [15] M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, T. Schram, R. Ritzenthaler, G. Groeseneken, and A. Asenov, IEEE Trans. Electron Dev., 60, p.2505 (2013).

- [16] M. Duan, J. F. Zhang, Z. Ji, W. D. Zhang, B. Kaczer, T. Schram, R. Ritzenthaler, G. Groeseneken, and A. Asenov, IEEE Trans. Elec. Dev., 61, p.3081 (2014).

- [17] A. Manut, R. Gao, J. F. Zhang, Z. Ji , M. Mehedi, W. D. Zhang, D. Vigar, A. Asenov, and B. Kaczer, IEEE Trans. Elec. Dev., 66, p.1482 (2019).

- [18] B. Kaczer, J. Franco, M. Toledano-Luque, Ph. J. Roussel, M. F. Bukhori, A. Asenov, B. Schwarz, M. Bina, T. Grasser, G. Groeseneken, irps, p.5A.2.1, (2012).

- [19] L. M. Procel, F. Crupi, J. Franco, L. Trojman, and B. Kaczer, IEEE Electron Device Lett., 35, p. 1167 (2014).