# DEFECTS AND LIFETIME PREDICTION OF GERMANIUM MOSFETS

JIGANG MA

A thesis submitted in partial fulfilment of the requirements of Liverpool John Moores University for the degree of Doctor of Philosophy

September 2014

To my family

### Acknowledgements

First and foremost, I would like to thank my supervisor, Professor Jian Zhang, for his continuous support, guidance and encouragement throughout my research project. I owe my professional development and confidence to Jian for his critical thinking and strong heart as well as fighting together with me through the dark night. It always encourages me to stand up and face the difficulties when I recall the words "where there is a will, there will be a way!"

I would also thank Professor Weidong Zhang, who instructed me by his words and deed. He offered me a lot of great insights that strengthen the fruitful discussion and make the work more efficient. He also helped me in better organizing the thesis.

I also owe a lot of gratitude to Dr. Zhigang Ji for his restless efforts and hardworking with me. He sets an example of hardworking, with proficient programming skills and agile thinking.

And I would also like to thank Dr. Benbakhti Brahim, who helped me a lot for the simulation work. His patient explanation inspires me to move forward step by step.

I learned a lot from the former and present members of LJMU microelectronics reliability and characterization group: Dr. Meng Duan, Dr. Baojun Tang, Dr. Lin Lin, Dr. Sharifah Fatmadiana Wan Muhamad Hatt, Dr. Xuefeng Zheng, Colin Robinson, Zheng Chai, Rui Gao and Azriff Manut, who did solid work in developing techniques for characterizing the defects in MOSFETs. And I have special thanks for my MSc. supervisor, Professor Xiaohua Ma. Thanks for all the help and harmonious relationship.

My research and living would not be possible without the funding from the EPSRC and School of Engineering. I am also grateful to our project partner, Professor Steve Hall in the University of Liverpool, Professor John Robertson in the University of Cambridge and the colleagues in the Interuniversity Microelectronics Research Centre (IMEC). It was an honour for me to present in the research seminars held in either Liverpool or Cambridge, which will be a treasure in my whole life.

I had great days in office 509B and great time with friends made along the way: Chee Shen Lim, Hang Seng Che, Kumaran Rajarathinam, Yusheng Liu, Ahmed Abd Elhadi and Ab Rahim A'Zraa Afhzan, Sonny-Jay Woodhouse, Charlie Bragg and Di Zhang, who made my days humorous and colourful in multi-cultures. I owe sincere thanks to my roommates for the long-standing friendship and I have special thanks to my friends, Bo Wang, Huilong Zhang and Shanyue Guan, for their caring, listening and understanding.

Last, but not least, I would like to express my deepest love to my parents for their unconditional support and dedication. Finally, I wish my grandparents could share the joy deep in my heart and the blessing for their happiness in the paradise.

### Abstract

To continue improving device speed, much effort has been made to replace Si by high mobility semiconductors. Ge is considered as a strong candidate for pMOSFETs due to the high hole mobility. Two approaches have been demonstrated: high-k/Si-cap/Ge and high-k/GeO<sub>2</sub>/Ge. Negative Bias Temperature Instability (NBTI) is still one of the main reliability issues, limiting the device lifetime. In this project, it is found that the conventional lifetime prediction method developed for Si is inapplicable to Ge devices and defect properties in Ge and Si MOSFETs are different.

The threshold voltage degradation in Ge can be nearly 100% recovered under a much lower temperature than that in Si devices. The defect losses observed in Si devices were absent in Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>. The generation of interface states is insignificant and the positive charges in GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> on Ge dominate the NBTI. These positive charges do not follow the same model as those in SiON/Si and an energy-alternating model has been proposed: there are a spread of energy levels of neutral hole traps below Ev and they lift up after charging, and return below Ev after neutralization.

The energy distribution of positive charges in the Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub>/Ge gate stack was studied by the Discharge-based Multi-pulse (DMP) Technique. The different stress-time dependence of defects below Ev and around Ec indicates that they originate from different defects. Quantization effect, Fermi level pinning, and discharge voltage step were considered. The defect differences in terms of the energy level were investigated by using the DMP technique and the energy alternating model is verified by the defect energy distribution.

Based on the understanding of different defect behavior, a new NBTI lifetime prediction method was developed for Ge MOSFETs. Energy alternating defects were separated from as-grown hole traps (AHT), which enables to restore the power law for NBTI kinetics with a constant power exponent. The newly developed Ge method was applicable for NBTI lifetime prediction of the state-of-the-art Si-cap/Ge and GeO<sub>2</sub>/Ge MOSFETs. When compared with SiON/Si, the optimized Si-cap/Ge shows superior reliability, while GeO<sub>2</sub>/Ge is inferior and needs further optimization. Preliminary characterization was also carried out to investigate the impacts of energy levels and characteristic times of different defects on the frequency and duty factor dependence of AC NBTI degradation.

## Contents

| A  | AcknowledgementsI |                                                            |  |  |

|----|-------------------|------------------------------------------------------------|--|--|

| A  | AbstractIII       |                                                            |  |  |

| C  | onten             | S                                                          |  |  |

| Li | ist of A          | Abbreviations                                              |  |  |

| Li | ist of S          | Symbols                                                    |  |  |

|    |                   |                                                            |  |  |

| 1  | Intr              | oduction of the project1                                   |  |  |

|    | 1.1               | Research concerns and rationale 1                          |  |  |

|    | 1.2               | Objectives of the project                                  |  |  |

|    | 1.3               | Novelty and originality of the research                    |  |  |

|    | 1.4               | Organization of the thesis                                 |  |  |

|    |                   |                                                            |  |  |

| 2  | A re              | eview of Germanium MOSFETs and challenges in advanced CMOS |  |  |

|    | tech              | nology                                                     |  |  |

|    | 2.1               | Historical overview                                        |  |  |

|    | 2.2               | The properties of Germanium                                |  |  |

|    | 2.3               | Ge surface passivation and defects                         |  |  |

|    | 2.3               | .1 High-k/GeO <sub>2</sub> /Ge structure                   |  |  |

|    | 2.3               | .2 High-k/SiO <sub>2</sub> /Si-cap/Ge structure            |  |  |

| 2.4  | Re    | liability issues in Ge MOSFETs                    | 17 |

|------|-------|---------------------------------------------------|----|

| 2.   | .4.1  | Positive charges (PCs) in oxide                   | 17 |

| 2    | .4.2  | Negative bias temperature instability (NBTI)      | 18 |

| 2    | .4.3  | Positive bias temperature instability (PBTI)      | 20 |

| 2    | .4.4  | Hot carrier (HC) degradation                      | 21 |

| 2.5  | NE    | 3TI models                                        | 22 |

| 2    | .5.1  | Reaction-Diffusion Model                          | 23 |

| 2    | .5.2  | Hole Trapping Model                               | 24 |

| 2    | .5.3  | Two Stage Model                                   | 26 |

| 2    | .5.4  | As-grown-Generation (A-G) Model                   | 27 |

| 2.6  | Su    | mmary                                             | 29 |

|      |       |                                                   |    |

| 3 Ex | perin | nental Facilities and Characterization Techniques | 30 |

| 3.1  | Int   | roduction                                         | 30 |

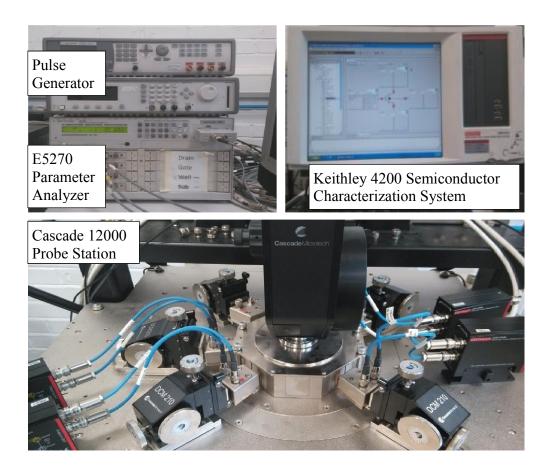

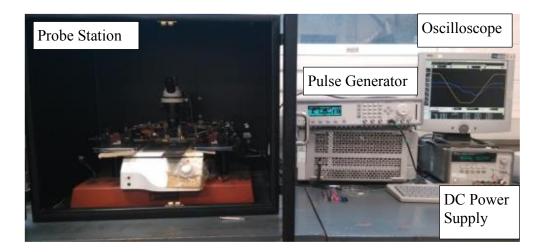

| 3.2  | Sy    | stem and Instrumentation                          | 30 |

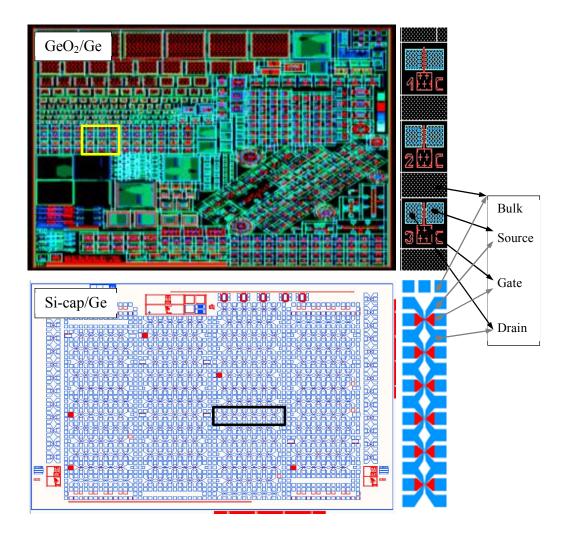

| 3.3  | La    | yout of Ge samples                                | 33 |

| 3.4  | Co    | nventional Characterization Techniques            | 34 |

| 3    | .4.1  | Conventional Id-Vg (DC I-V) Technique             | 34 |

| 3.   | .4.2  | Charge Pumping (CP) Technique                     | 36 |

| 3.   | .4.3  | Conventional Capacitance Voltage (C-V) Technique  | 39 |

| 3.5 I                                                                                                    | imitation of conventional Techniques for Ge MOSFETs                                                                                                                                                                                                                                  | 43                                     |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 3.6 S                                                                                                    | tress-and-Sense Methodology                                                                                                                                                                                                                                                          | 45                                     |

| 3.6.1                                                                                                    | Typical Methodology                                                                                                                                                                                                                                                                  | 45                                     |

| 3.6.2                                                                                                    | Integration of multiple types of measurements                                                                                                                                                                                                                                        | 46                                     |

| 3.7 A                                                                                                    | dvanced Characterization Techniques                                                                                                                                                                                                                                                  | 47                                     |

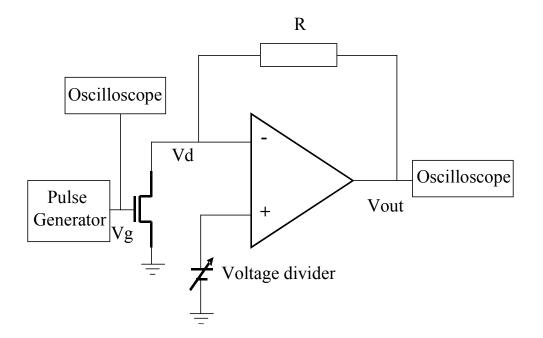

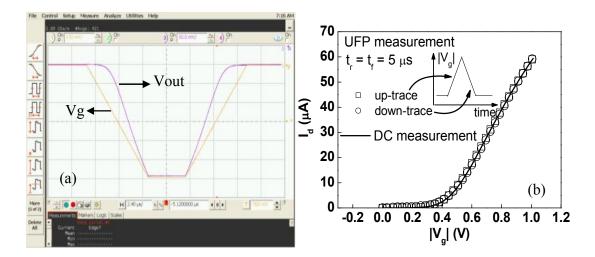

| 3.7.1                                                                                                    | Pulsed Id-Vg (Pulsed I-V) Technique                                                                                                                                                                                                                                                  | 47                                     |

| 3.7.2                                                                                                    | Ultra-Fast Pulsed (UFP) Technique                                                                                                                                                                                                                                                    | 49                                     |

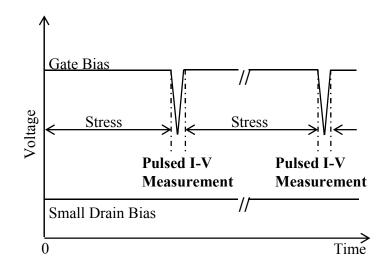

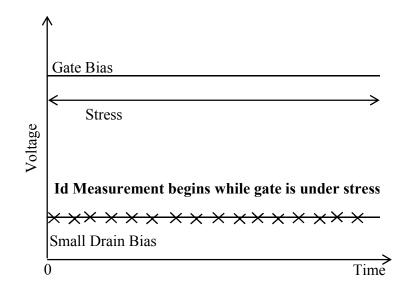

| 3.7.3                                                                                                    | Ultra-Fast On-The-Fly (OTF) Technique                                                                                                                                                                                                                                                | 50                                     |

| 3.7.4                                                                                                    | Discharge-based Multi-Pulse (DMP) Technique                                                                                                                                                                                                                                          | 51                                     |

| 20 0                                                                                                     |                                                                                                                                                                                                                                                                                      | 53                                     |

| 3.8 S                                                                                                    | ummary                                                                                                                                                                                                                                                                               |                                        |

| 3.8 3                                                                                                    | ummary                                                                                                                                                                                                                                                                               |                                        |

|                                                                                                          | NBTI Characterization and Defects Properties in Ge MOSFETs .                                                                                                                                                                                                                         |                                        |

| 4 Initial                                                                                                |                                                                                                                                                                                                                                                                                      | 54                                     |

| <b>4 Initial</b><br>4.1 I                                                                                | NBTI Characterization and Defects Properties in Ge MOSFETs .                                                                                                                                                                                                                         | <b> 54</b><br>54                       |

| <b>4 Initial</b><br>4.1 I                                                                                | NBTI Characterization and Defects Properties in Ge MOSFETs.                                                                                                                                                                                                                          | <b>54</b><br>54<br>55                  |

| <b>4 Initial</b><br>4.1 I<br>4.2 I                                                                       | <b>NBTI Characterization and Defects Properties in Ge MOSFETs .</b><br>ntroduction                                                                                                                                                                                                   | 54<br>54<br>55<br>55                   |

| <ul> <li>4 Initial</li> <li>4.1 I</li> <li>4.2 I</li> <li>4.2.1</li> <li>4.2.2</li> </ul>                | NBTI Characterization and Defects Properties in Ge MOSFETs.<br>ntroduction<br>Devices and Measurement Procedure<br>Device Process and Test Procedure                                                                                                                                 | 54<br>54<br>55<br>55                   |

| <ul> <li>4 Initial</li> <li>4.1 I</li> <li>4.2 I</li> <li>4.2.1</li> <li>4.2.2</li> </ul>                | NBTI Characterization and Defects Properties in Ge MOSFETs .<br>ntroduction<br>Devices and Measurement Procedure<br>Device Process and Test Procedure<br>Determination of Electric Field and Measurement Time (tm)                                                                   | 54<br>55<br>55<br>57<br>59             |

| <ul> <li>4 Initial</li> <li>4.1 I</li> <li>4.2 I</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.3 I</li> </ul> | NBTI Characterization and Defects Properties in Ge MOSFETs .<br>ntroduction<br>Devices and Measurement Procedure<br>Device Process and Test Procedure<br>Determination of Electric Field and Measurement Time (tm)<br>npact of Stress Electric Field on NBTI of GeO <sub>2</sub> /Ge | 54<br>54<br>55<br>55<br>57<br>59<br>59 |

| 4.4.1                                                                                                       | Effect of Stress Temperature                                                                                                                                                                                                         | 62                                           |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 4.4.2                                                                                                       | Effect of Anneal                                                                                                                                                                                                                     | 65                                           |

| 4.5 Co                                                                                                      | ontribution of Interface States Generation                                                                                                                                                                                           | 67                                           |

| 4.5.1                                                                                                       | Charge Pumping Measurement                                                                                                                                                                                                           | 68                                           |

| 4.5.2                                                                                                       | Estimation of Interface States Generation                                                                                                                                                                                            | 69                                           |

| 4.5.2                                                                                                       | Confirmation by Id-Vg Measurement                                                                                                                                                                                                    | 71                                           |

| 4.6 Pc                                                                                                      | sitive charges in dielectric: energy switching model                                                                                                                                                                                 | 71                                           |

| 4.6.1                                                                                                       | Properties of Positive charges (PC)                                                                                                                                                                                                  | 72                                           |

| 4.6.2                                                                                                       | Energy Alternating Model                                                                                                                                                                                                             | 75                                           |

|                                                                                                             |                                                                                                                                                                                                                                      | -                                            |

| 4.7 Su                                                                                                      | immary                                                                                                                                                                                                                               | 78                                           |

| 4.7 Sı                                                                                                      | immary                                                                                                                                                                                                                               | 78                                           |

|                                                                                                             | Immary<br>Trap Energy Distribution by Discharge-based Multi-pulse (                                                                                                                                                                  |                                              |

| 5 Hole 7                                                                                                    |                                                                                                                                                                                                                                      | (DMP)                                        |

| 5 Hole T<br>Technie                                                                                         | Trap Energy Distribution by Discharge-based Multi-pulse (                                                                                                                                                                            | DMP)<br>80                                   |

| 5 Hole T<br>Technic<br>5.1 In                                                                               | Frap Energy Distribution by Discharge-based Multi-pulse (                                                                                                                                                                            | ( <b>DMP)</b><br>80<br>80                    |

| 5 Hole T<br>Technic<br>5.1 In                                                                               | Frap Energy Distribution by Discharge-based Multi-pulse (<br>que                                                                                                                                                                     | ( <b>DMP)</b><br>80<br>80<br>81              |

| 5 Hole T<br>Technic<br>5.1 In<br>5.2 Pr                                                                     | Trap Energy Distribution by Discharge-based Multi-pulse (         que         troduction         inciple of Discharge-based-Pulse (DMP) Technique                                                                                    | ( <b>DMP)</b><br>80<br>80<br>81<br>81        |

| <ul> <li>5 Hole T</li> <li>Technic</li> <li>5.1 In</li> <li>5.2 Pr</li> <li>5.2.1</li> <li>5.2.2</li> </ul> | Trap Energy Distribution by Discharge-based Multi-pulse (         que         troduction         inciple of Discharge-based-Pulse (DMP) Technique         DMP Technique for Probing Hole Traps                                       | ( <b>DMP</b> )<br>80<br>81<br>81<br>81       |

| <ul> <li>5 Hole T</li> <li>Technic</li> <li>5.1 In</li> <li>5.2 Pr</li> <li>5.2.1</li> <li>5.2.2</li> </ul> | Trap Energy Distribution by Discharge-based Multi-pulse (         que         troduction         inciple of Discharge-based-Pulse (DMP) Technique         DMP Technique for Probing Hole Traps         Charge Polarity of Hole Traps | ( <b>DMP</b> )<br>80<br>81<br>81<br>82<br>84 |

| 5.4    | Energy distribution of Hole Traps in GeO <sub>2</sub> /Ge Gate Stack |

|--------|----------------------------------------------------------------------|

| 5.4.   | 1 Energy distribution of Hole Traps                                  |

| 5.4.   | 2 Contribution of Interface States                                   |

| 5.4.   | 3 Effects of Stress Time                                             |

| 5.5    | Quantization and Fermi Level Pinning Effects                         |

| 5.5.   | 1 Quantization Effect                                                |

| 5.5.   | 2 Fermi Level Pinning Effect                                         |

| 5.5.   | 3 Discharge Voltage Step                                             |

| 5.6    | Understanding of Defect Differences and Energy Alternating           |

| 5.6.   | 1 Defect Differences                                                 |

| 5.6.   | 2 Energy Alternating Defects (EAD) Model                             |

| 5.6.   | 3 Confirmation of Energy Alternating Defects 101                     |

| 5.6.   | 4 Charging/Discharging via Tunneling104                              |

| 5.7    | Summary                                                              |

|        |                                                                      |

| 6 Inve | stigation of NBTI lifetime prediction and AC kinetics in Germanium   |

| рМС    | DSFETs 107                                                           |

| 6.1    | Introduction                                                         |

| 6.2    | Devices and experiments                                              |

| 6.3    | As-grown hole traps (AHT) and EAD separation 111                     |

| 6.4 Re   | estore power law and enable lifetime prediction in Ge 114                                     |

|----------|-----------------------------------------------------------------------------------------------|

| 6.5 Li   | fetime prediction in Si-cap/Ge and device optimization116                                     |

| 6.5.1    | Energy Profile of AHTs in Si-cap/Ge 116                                                       |

| 6.5.2    | Application of Ge method in Si-cap/Ge118                                                      |

| 6.5.3    | Lifetime prediction of Si-cap/Ge and process optimization 119                                 |

| 6.6 In   | itial investigation of characteristic time of defects in GeO <sub>2</sub> /Ge devices and its |

| impact o | n NBTI under AC stress conditions                                                             |

| 6.6.1    | Measurement procedure                                                                         |

| 6.6.2    | Impact of stress bias and temperature on AC NBTI behaviors in $GeO_2/Ge$ .                    |

|          |                                                                                               |

| 6.6.3    | Charging/Discharging Characteristic time of AHTs126                                           |

| 6.7 D    | efects properties and initial understanding of AC behavior in Si-cap/Ge                       |

| devices  |                                                                                               |

| 6.7.1    | Frequency and Duty Factor Characteristics                                                     |

| 6.7.2    | Defects Properties in Si-cap/Ge devices                                                       |

| 6.7.3    | Impact of Charging/Discharging Characteristic time on AC behavior 132                         |

| 6.8 Sı   | ımmary 133                                                                                    |

| 7 Sum | mary | v and Future work135                                                   |

|-------|------|------------------------------------------------------------------------|

| 7.1   | Su   | mmary 135                                                              |

| 7.    | 1.1  | Initial NBTI characterization and defects properties in Ge MOSFETs 136 |

| 7.1.2       | Energy Distribution of Hole Traps in Ge MOEFETs 137                        |

|-------------|----------------------------------------------------------------------------|

| 7.1.3       | Investigation of defects behavior and enabling NBTI lifetime prediction in |

| Ge pM       | OSFETs138                                                                  |

| 7.2 Fu      | ture work                                                                  |

| References  |                                                                            |

| List of Pub | lications                                                                  |

| Abbreviation                   | Signification                                     |

|--------------------------------|---------------------------------------------------|

| GeO <sub>2</sub>               | Germanium dioxide                                 |

| High-k                         | High dielectric constant/permittivity             |

| SiON                           | Silicon Oxide Nitride                             |

| HfO <sub>2</sub>               | Hafnium dioxide                                   |

| Al <sub>2</sub> O <sub>3</sub> | Aluminum oxide                                    |

| NBTI                           | Negative Bias Temperature Instability             |

| PBTI                           | Positive Bias Temperature Instability             |

| TDDB                           | Time Dependent Dielectric Breakdown               |

| НС                             | Hot Carrier                                       |

| PCs                            | Positive Charges                                  |

| EOT                            | Equivalent Oxide Thickness                        |

| СР                             | Charge Pumping                                    |

| TC                             | Transfer Curve                                    |

| MOSFET                         | Metal Oxide Semiconductor Field Effect Transistor |

| TaN                            | Tantalum Nitride                                  |

| TiN                            | Titanium Nitride                                  |

| DMP                            | Discharge-based Multi-Pulse                       |

| CNL                            | Charge Neutrality Level                           |

| FLP                            | Fermi Level Pinning                               |

## List of Abbreviations

| CCS  | Capture Cross Section       |

|------|-----------------------------|

| AHT  | As-grown Hole Traps         |

| CPC  | Cyclic Positive Charge      |

| ANPC | Anti-Neutralized Hole Traps |

## List of Symbols

| Symbol                          | Description                                    | Unit                              |

|---------------------------------|------------------------------------------------|-----------------------------------|

| Nc                              | Effective density of states in conduction band | cm <sup>-3</sup>                  |

| Nv                              | Effective density of states in valence band    | cm <sup>-3</sup>                  |

| σi                              | Capture cross section                          | cm <sup>2</sup>                   |

| C <sub>ox</sub>                 | Oxide capacitance                              | F                                 |

| $C_{ m lf}$                     | Low-frequency substrate capacitance            | F                                 |

| Cs                              | Semiconductor capacitance                      | F                                 |

| f                               | Frequency                                      | Hz                                |

| $E_{f}$                         | Fermi level                                    | eV                                |

| Eox                             | Oxide electric field                           | MV/cm                             |

| Ev                              | Valence band                                   | eV                                |

| Ec                              | Conduction band                                | eV                                |

| g <sub>m</sub> , G <sub>m</sub> | Transconductance                               | S                                 |

| I <sub>d</sub>                  | Drain current                                  | А                                 |

| Ig                              | Gate current                                   | А                                 |

| Is                              | Source current                                 | А                                 |

| Іср                             | Charge pumping current                         | А                                 |

| L                               | Gate channel length                            | μm                                |

| W                               | Gate channel width                             | μm                                |

| D <sub>it</sub>                 | Interface trap density                         | eV <sup>-1</sup> cm <sup>-2</sup> |

| N <sub>it</sub>        | Interface trap density                | cm <sup>-2</sup> |

|------------------------|---------------------------------------|------------------|

| q                      | One electron charge                   | С                |

| R                      | Feedback resistance                   | Ω                |

| G                      | Conductance                           | S                |

| $\Phi_{ m S}$          | Surface potential                     |                  |

| V <sub>d</sub>         | Drain voltage                         | V                |

| V <sub>out</sub>       | Output voltage                        | V                |

| Т                      | Temperature                           | °C               |

| n                      | Power exponent                        |                  |

| m                      | Time-to-failure exponent              |                  |

| γ                      | Voltage acceleration exponent         |                  |

| t <sub>m</sub>         | Measurement time                      | sec              |

| ts                     | Stress time                           | sec              |

| V <sub>discharge</sub> | Gate voltage applied during discharge | V                |

| $V_{fb}$               | Flat band voltage                     | V                |

| $V_{g}$                | Voltage applied on the gate           | V                |

| V <sub>ov</sub>        | Overdrive voltage                     | V                |

| V <sub>th</sub>        | Threshold voltage                     | V                |

| $V_{\text{th0}}$       | Fresh threshold voltage               | V                |

| $\Delta V_{th}$        | Threshold voltage shift               | V                |

| $\mathbf{V}_{gst}$     | Stress voltage applied on the gate    | V                |

| $V_{g\_rec}$           | Recovery voltage applied on the gate  | V                |

## **I** Introduction of the project

#### **1.1 Research concerns and rationale**

The downscaling of Si MOSFETs is approaching its end since the device is running out of atoms and its leakage and variability are becoming intolerable [1-6]. To continue improving device speed, much effort has been made to replace Si by high mobility semiconductors [1-4]. Ge is a strong candidate, especially for pMOSFETs because its intrinsic hole mobility is about 4 times of that for Si. Promising results have already been demonstrated for Ge pMOSFETs through two approaches: high-k/Si-cap/Ge [1, 2, 4] and high-k/GeO<sub>2</sub>/Ge [2, 3, 7-9]. Interface states can be as low as that for SiO<sub>2</sub>/Si [7, 8, 10] and the potential for fabricating Ge nMOSFETs has been demonstrated [7, 11, 12]. The process for fabricating Ge MOSFETs is becoming sufficiently mature and reproducible to warrant research into their reliability [13-15]. Good TDDB data were obtained [14], but electron trapping is high [16], similar to that in the early stage of developing high-k/SiON stack for Si [17-20]. For Si-based CMOS technologies, the negative bias temperature instability (NBTI) is the most severe reliability issue, since it results in a lifetime of pMOSFETs shorter than that of nMOSFETs [21, 22]. With Sicapped Ge MOSFETs, it has been reported that NBTI can be lower than its Si counterpart [2, 14, 15, 23]. For the Ge pMOSFETs without a Si-cap layer, however, there is little information available on the NBTI and the properties of defects responsible

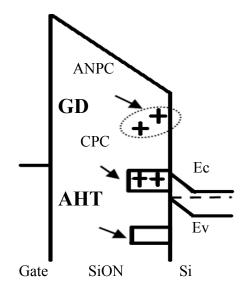

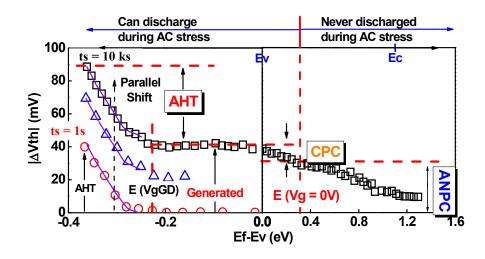

for it. The works for NBTI in Si devices report that there are three types of positive charges: AHT (As-grown Hole Trap), ANPC (Anti-Neutralization Positive Charge), and CPC (Cyclic Positive Charge) [17-20]. For the purpose of comparison, the initial NBTI

in Si MOSFETs.

Efforts were made to extract the energy distribution of PCs [24, 25], but they used the slow quasi-DC measurement, hence did not capture the defects that discharged rapidly. Moreover, they only provide distribution within the bandgap. As a result, two types of PCs, AHT and ANPC, were not covered by these early works [24, 25]. A discharge-based multiple pulse (DMP) technique has been developed recently to evaluate the different types PCs in Si device [26]. Attempts have also been made in high mobility channel devices, however, only energy distribution of the interface traps [27] and PBTI induced border traps [28] were characterized. There is little information on the PCs induced by NBTI in Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub>/Ge pMOSFETs. To assist in the understanding and further minimization, it is desirable to know their energy distribution, which also provides the PC density at a given surface potential needed for simulating the NBTI impact on devices and circuits in the future.

characterization is carried out on Ge MOSFETs as referred to the framework of defects

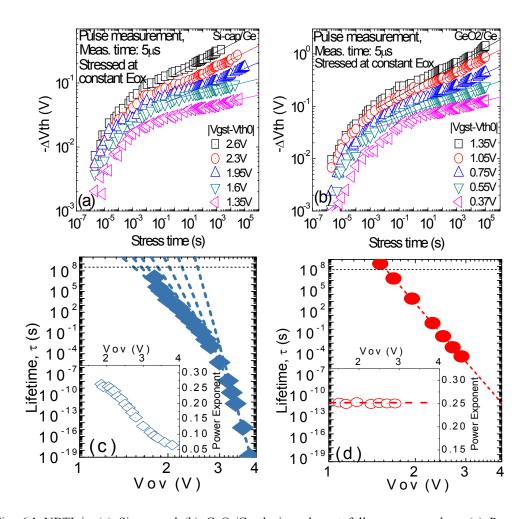

It has been found out that traditional lifetime prediction method with DC measurement cannot be applied to Ge with Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub> gate stack, due to the non-constant power exponent under different stress conditions [29]. The reason was unknown at that time. It was reported that Si-cap/Ge device has superior reliability, but NBTI degradation in Si-

cap Ge devices by DC measurement cannot be described by power law [30]. Its lifetime,  $\tau$ , cannot be predicted by power law extrapolation, either [30, 31]. This holds for both Si-cap and GeO<sub>2</sub> based gate stacks in Ge devices, albeit NBTI for GeO<sub>2</sub>/Ge is higher [32]. Reproducible results can be achieved for the state-of-art Germanium process, but little is known about the defects. When measured by the fast pulse technique, the existing NBTI prediction method is inapplicable for both Si-cap/Ge and Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub>/Ge, preventing reliable lifetime prediction. It is essential to develop a new lifetime prediction method for Ge devices, to assist in further process and device optimization.

### **1.2** Objectives of the project

To understand the properties of defects responsible for NBTI in Ge MOSFETs, the initial characterization compares the NBTI of Ge and Si devices, including the impact of stress electric field and stress temperature, the effects of annealing and measurement temperature and defect losses. Contribution of interface states generation will be estimated by using charge pumping technique. An energy alternating model will be proposed to explain the differences.

The second objective is to study the energy distribution of positive charges in the  $Al_2O_3/GeO_2/Ge$  gate stack. Discharge-based Multi-pulse (DMP) Technique will be adapted to characterize the impact of stress time on the energy distribution. Quantization effect, Fermi level pinning effect and discharge voltage step will be further evaluated for

the DMP application on Ge devices. The energy alternating model will be verified by the defect energy distribution.

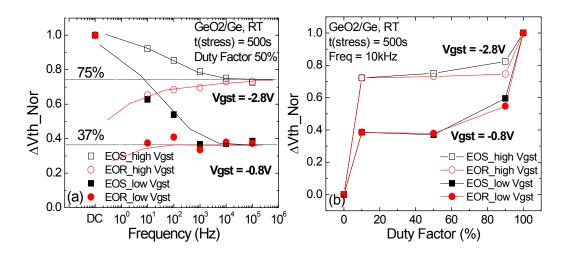

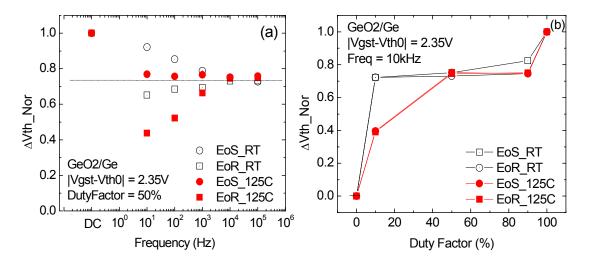

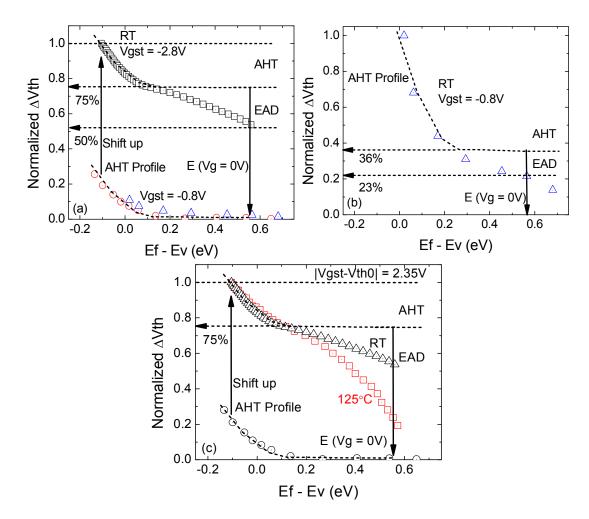

Finally, with the knowledge of trap energy level, the behavior of different defects during DC and AC NBTI stress in Ge device will be investigated, which enables us to develop a new NBTI lifetime prediction method for Ge MOSFETs. Energy alternating defects will be separated from as-grown hole traps (AHT) to restore power law for NBTI kinetics with constant power exponents. The NBTI lifetime of the state-of-the-art Si-cap/Ge will be predicted by the newly developed Ge method with power law extrapolation. Three CMOS technology systems, consisting of SiO<sub>2</sub>/Si, GeO<sub>2</sub>/Ge and Si-cap/Ge, will be further evaluated, which shows process and device optimization needed. Impacts of energy levels and characteristic times of different defects on the frequency and duty factor dependence of AC NBTI degradation will be examined.

### **1.3** Novelty and originality of the research

- 1) For the first time, a detailed and systematic NBTI characterization was carried out and compared with Si device, focusing on the defect properties in Ge MOSFETs.

- The energy distribution of hole traps in Ge MOSFETs was extracted by adapting the Discharge-based Multi-pulse (DMP) Technique.

- An energy alternating defect model is proposed and verified from both slow and fast measurements for Ge NBTI.

- 4) A new NBTI lifetime prediction method is developed for Ge devices, based on the understanding of differences from the generated defects in Si.

- 5) This method is applied to Si-cap/Ge devices and NBTI Lifetime in SiO<sub>2</sub>/Si, GeO<sub>2</sub>/Ge and Si-cap/Ge is compared to show the process improvement achieved and further device optimization needed.

- 6) For the first time, the impact of energy levels and characteristic times of defects on the AC NBTI in Ge MOSFETs is investigated.

#### **1.4 Organization of the thesis**

The thesis is organized as follows:

Chapter 2 gives a review of CMOS technology and challenges in advanced Germanium MOSFETs. The fundamental properties of Germanium are compared with Si and III-V devices. Ge surface passivation and defects are discussed in two main Ge structures: high-k/GeO<sub>2</sub>/Ge and high-k/SiO<sub>2</sub>/Si-cap/Ge. Reliability issues are introduced in Ge MOSFETs, such as Positive charges (PCs) in oxide, Negative bias temperature instability (NBTI), Positive bias temperature instability (PBTI) and Hot carrier (HC) degradation. NBTI models, including Reaction-Diffusion Model, Hole Trapping Model, Two Stage Model, As-grown Generation (A-G) Model are discussed individually in this chapter.

Chapter 3 introduces the experimental system and techniques for characterizing Ge pMOSFETs. Conventional techniques consist of the DC Id-Vg Technique, Charge Pumping (CP) Technique, Capacitance Voltage (C-V) Technique and Conductance Technique. Limitations of conventional techniques application for Ge MOSFET are reviewed. The advantages of the advanced techniques in characterizing Ge devices are discussed, including the Pulse Id-Vg (Pulsed I-V) Technique, Ultra-Fast Pulsed (UFP) Technique, Ultra-Fast On-The-Fly (OTF) Technique and Discharge-based Multi-Pulse (DMP) Technique.

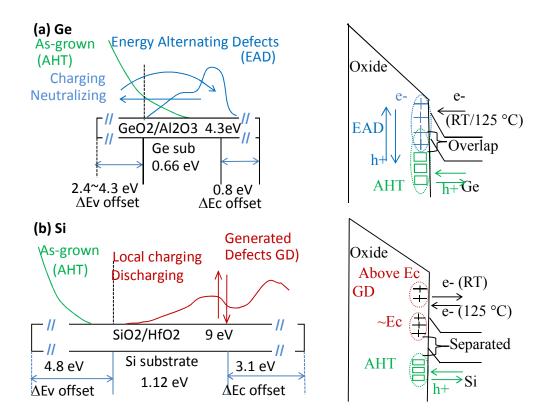

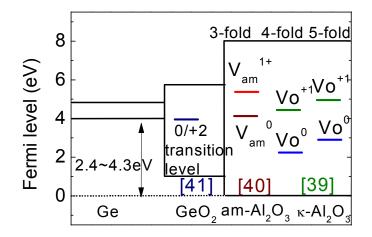

Chapter 4 presents the initial characterization of NBTI for Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and its comparison with Si samples. Similar to Si samples, NBTI is activated both electrically and thermally for Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>. Similarities and differences are discussed, including the impact of stress electric field and stress temperature, the effects of anneal and measurement temperature and defect losses. Contributions of interface states generation are estimated by using charge pumping technique and confirmed further by Id-Vg measurement. An energy alternating model is proposed to explain the defect differences between Ge and Si devices.

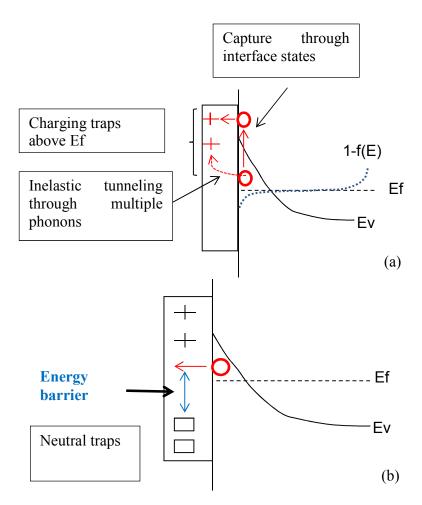

Chapter 5 studies the energy distribution of PCs in the Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub>/Ge gate stack characterized by Discharge-based Multi-pulse (DMP) Technique. Principle of DMP techniques is described and the charge polarity of hole traps is explained. Disturbance from the trapping/detrapping during the measurement is discussed. Energy distribution of PCs in the Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub>/Ge gate stack is characterized. The contribution of interface

states and effects of stress time were further discussed. Quantization effect, Fermi level pinning effect and discharge voltage step are further evaluated for the DMP application on Ge devices. Energy alternating defects are verified though their energy distribution.

Chapter 6 further demonstrates that the defects behave differently in Ge and Si devices. Energy alternating defects exist in Ge devices, which were separated from as-grown hole traps (AHT) to restore power law NBTI kinetics with constant power exponents. The developed Ge method was applicable in Si-cap/Ge devices. NBTI Lifetime is predicted with power low extrapolation for three CMOS technologies to show improvement achieved and the further process/device optimization needed. Si-cap/Ge shows superior reliability while GeO<sub>2</sub>/Ge needs further optimization. Also, the impact of defects on the AC NBTI in Ge MOSFETs is evaluated.

Chapter 7 summarizes the thesis and draws conclusions. The topics and direction for future works are discussed.

## 2 A review of Germanium MOSFETs and challenges in advanced CMOS technology

#### 2.1 Historical overview

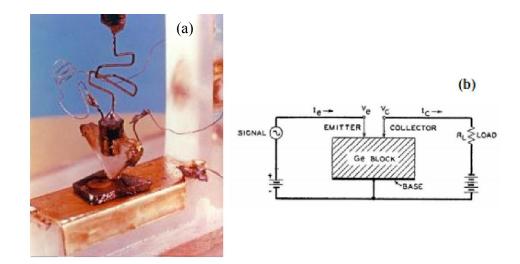

Germanium was the semiconductor material used to develop the first transistor by J. Bardeen and W.H. Brattain at Bell Laboratories in 1947 [33], as shown in Fig. 2.1. This invention created a large number of novel solid state electron device applications thereafter, dominating the markets in 1950s to 1970s. From early 1970s, silicon started to replace germanium after high quality silicon wafer were made available, and also because SiO<sub>2</sub> provided a highly stable and naturally high quality interface with silicon substrate in MOSFET structures.

Fig. 2.1 (a) The first point contact Ge amplifier [34] and (b) schematic of semiconductor triode [33]

In 1959, the first integrated circuit was invented by Jack Kilby at Texas Instruments [35] and Robert Noyce at Fairchild Semiconductor [36], which allowed the integration of multiple devices in one chip. The mass production is then enabled after the development of processes for complementary metal–oxide–semiconductor (CMOS) integration technology by Frank Wanlass in 1963 [37]. Since then, ultra large scale integration (ULSI) chips with high speed, high density integration and low power consumption have been achieved by shrinking the feature sizes of transistors over the past fifty years.

The downscaling trend was first described by Moore's Law in 1965 [38], which is the observation that the number of transistors in the integrated circuit doubles in about every two years. This exponential improvement has been the driving force to enhance the performance and reduce the cost, which provides the incentive for semiconductor industry to keep pursuing the down-scaling. In order to further scale down beyond the 45 nm technology nodes following the Moore's law, SiO<sub>2</sub>, which had already reached its minimum physical thickness of 1~2 nm for preventing excessively large leakage current, was no longer viable and had been combined with the high-k dielectric at 45nm technology node by Intel in 2007 [39]. For technology beyond the 20 nm node, there are a number of physical limitations to be overcome for achieving higher performance on the Si CMOS. This has become increasingly difficult so that equivalent scaling cycle has slowed down to three years rather than two. Using novel device structures and materials is becoming more and more important for further boosting the performance.

In order to gain adequate drive current for highly scaled MOSFETs, channel materials

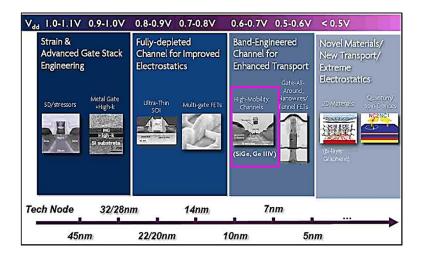

with high charge carrier mobility, such as III-V or germanium, are needed. Implementation of non-classical CMOS channel materials is planned to replace Si from 2021 to 2028 according to the International Technology Roadmap for Semiconductor (ITRS) [40]. This has motivated extensive revisits of germanium as an alternative semiconductor material to be integrated with the silicon CMOS platform for building transistors with enhanced performance [40, 41]. Fig. 2.2 shows logic device roadmap in IMEC, highlighting the research underway down to 5nm node. Power was a concern in high performance logic devices and efforts have been made to lower the power supply  $V_{dd}$ . For the 7nm node, it is believed that the channel will need to be replaced by high mobility material, Ge for pMOSFETs and InGaAs for nMOSFETs [42].

Fig. 2.2 Logic device Roadmap in IMEC 2014 [42]. It highlights the research future down to 5 nm node.

#### 2.2 The properties of Germanium

Germanium has fundamental advantages over Si, as shown by the physical properties listed in Table 2.1 [43]. The mobility, band gap and dielectric constant are also

compared between group IV and III-V semiconductors in Table 2.2. It shows that the electron and hole mobility of Ge is higher than that of Si by a factor of about two and four, respectively. Electron mobility in III-V is more than six times higher than that in Si. It is considered that the III-V nMOSFETs and Ge pMOSFETs are the best combination in terms of achieving the highest mobility. However, practical challenges still remain for the process integration of III-V material with the Si CMOS platform [44]. Germanium, on the other hand, has the advantage of better compatibility with Si. It has been reported that SiGe devices are able to offer superior performance and better reliability than Si for logic circuit applications [15, 45, 46].

| Properties                                            | Ge                    | Si <sub>0.5</sub> Ge <sub>0.5</sub> | Si                    | Units             |

|-------------------------------------------------------|-----------------------|-------------------------------------|-----------------------|-------------------|

| Atoms                                                 | $4.42 \times 10^{22}$ | $4.61 \times 10^{22}$               | 5.0×10 <sup>22</sup>  | /cm <sup>3</sup>  |

| Atomic weight                                         | 72.60                 | 50.345                              | 28.09                 |                   |

| Breakdown field                                       | ~10 <sup>5</sup>      | 2×10 <sup>5</sup>                   | ~3×10 <sup>5</sup>    | V/cm              |

| Crystal structure                                     | Diamond               | Diamond                             | Diamond               |                   |

| Density                                               | 5.3267                | 3.827                               | 2.328                 | g/cm <sup>3</sup> |

| Effective density of states<br>in conduction band, Nc | 1.04×10 <sup>19</sup> |                                     | 2.8×10 <sup>19</sup>  | /cm <sup>3</sup>  |

| Effective density of states<br>in valence band, Nv    | 6.0×10 <sup>18</sup>  |                                     | 1.04×10 <sup>19</sup> | /cm <sup>3</sup>  |

Table 2.1 The physical properties of Ge, SiGe and Ge [43]

|                                   | m* <sub>l</sub> =1.64   |                       | m*1=0.98               |    |

|-----------------------------------|-------------------------|-----------------------|------------------------|----|

| Effective mass, m*/m <sub>0</sub> | m* <sub>t</sub> =0.082  |                       | m* <sub>t</sub> =0.19  |    |

| Electrons                         | m* <sub>lh</sub> =0.044 |                       | m* <sub>lh</sub> =0.16 |    |

| Holes                             | m* <sub>hh</sub> =0.28  |                       | m* <sub>hh</sub> =0.49 |    |

| Electron affinity                 | 4.0                     |                       | 4.05                   |    |

| Intrinsic carrier                 | 2.4×10 <sup>13</sup>    | 1.2×10 <sup>13</sup>  | 1.45×10 <sup>10</sup>  |    |

| concentration                     |                         |                       |                        |    |

| Intrinsic Debye length            | 0.68                    | 12.34                 | 24                     | μm |

| Lattice constant                  | 5.6575                  | 5.5373                | 5.4310                 | А  |

| Minority carrier lifetime         | 1×10 <sup>-3</sup>      | 1.75×10 <sup>-3</sup> | 2.5×10 <sup>-3</sup>   | S  |

Table 2.2 Comparison of group IV and III-V semiconductors

|                                         | Si   | Ge   | GaAs | InAs  | InSb  |

|-----------------------------------------|------|------|------|-------|-------|

| Electron mobility (cm <sup>2</sup> /Vs) | 1600 | 3900 | 9200 | 40000 | 77000 |

| Hole mobility (cm <sup>2</sup> /Vs)     | 430  | 1900 | 400  | 500   | 850   |

| Band gap (eV)                           | 1.12 | 0.66 | 1.42 | 0.36  | 0.17  |

| Dielectric constant                     | 11.8 | 16   | 12.4 | 14.8  | 17.7  |

### 2.3 Ge surface passivation and defects

The water soluble nature of Ge oxides is one of the major challenges for Ge CMOS process. Although there were early efforts to investigate Ge MOSFETs by utilizing different MOS gate dielectric and junction formation technologies [47-59], significant

- 12 -

progress has only been achieved recently, among which two main approaches have been applied to overcome this problem [60-62]. One is the high-k/GeO<sub>2</sub>/Ge structure [60, 61] and the other one is the high-k/SiO<sub>2</sub>/Si/Ge structure with a Si capping layer on top of the Ge substrate [62].

#### 2.3.1 High-k/GeO<sub>2</sub>/Ge structure

Poor quality of the dielectric/Ge interface and strong Fermi level pinning (FLP) have been the major challenges for achieving high performance for Ge CMOSFETs [63]. It was found by the density functional theory simulation [64] and experiments [63] that the charge neutrality level (CNL) is located at ~0.1eV above the Ge valence band edge. It is very different from Si, in which the CNL is considered to be located at the midgap. Experiments also showed that CNL is responsible for the degraded Pt/HfO<sub>2</sub>/Ge nMOSFETs performance at operational conditions, due to the negative charges built up with the Fermi level locating above the CNL [63].

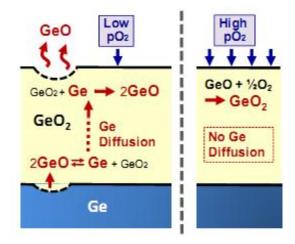

Fig. 2.3 Mechanism of Ge diffusion into GeO<sub>2</sub> and GeO desorption from GeO<sub>2</sub>/Ge stack [65].

Fig. 2.3 shows that Ge can diffuse into GeO<sub>2</sub> through GeO desorption (2GeO  $\leq >$  GeO<sub>2</sub> + Ge) under low-pressure O<sub>2</sub> (Low pO<sub>2</sub>) ambient and GeO can evaporate away, which deteriorates the GeO<sub>2</sub>/Ge interface and the GeO<sub>2</sub> dielectric. High-pressure O<sub>2</sub> (High PO<sub>2</sub>) ambient effectively suppressed the GeO generation by GeO +  $\frac{1}{2}$  O<sub>2</sub> => GeO<sub>2</sub>, which could help stop the Ge diffusion [65].

Adding a HfO<sub>2</sub> layer on top of GeO<sub>2</sub>, has not been effective in preventing this problem [66]. Latest studies showed that Al<sub>2</sub>O<sub>3</sub> can effectively suppress Ge diffusion [61]. High performance Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub>/Ge pMOSFETs was reported by employing novel plasma post oxidation method, with both low density of interface states (Dit)  $<10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> and thin equivalent oxide thickness (EOT) around 1nm [67]. Ultra-thin EOT ~0.7nm was achieved by using HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/GeO<sub>2</sub>/Ge gate stacks, in which Al<sub>2</sub>O<sub>3</sub> can prevent HfO<sub>2</sub>-GeO<sub>2</sub> from intermixing [68]. EOT of 0.5 nm with HfON/GeO<sub>2</sub> gate stack has been reported [69]. HfGeO<sub>4</sub> and La<sub>2</sub>GeO<sub>5</sub> are well bonded at interface as suggested by First principle (FP) calculation [70]. Experimental results confirmed their effective prevention of the Ge diffusion and improvement of interfacial properties [71, 72].

There have been early investigations on the defects in GeO<sub>2</sub>/Ge gate stack [65, 73]. Water-related GeO<sub>2</sub>/Ge was considered as free of any dangling bonds (DBs), including the GeOx transition region [73]. The energy position of interfacial defects at GeO<sub>2</sub>/Ge interface can be either near the conduction band minimum (CBM) or valence band maximum (VBM) [74], verified by using different states of dangling bonds (DBs) with the first-principle study. Oxygen vacancies near GeO<sub>2</sub>/Ge interface are the possible

origin of various interfacial states [65]. The fast trapping through interface states is possibly responsible for poor mobility in Ge nMOSFETs [75]. Slow trapping through GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> border traps and parasitic S/D series resistance can also cause degradation in Ge nMOSFETs [76].

Recent study shows promising results for GeO<sub>2</sub>/Ge pMOSFETs [2, 3, 7-9]. It has been reported that the interface states can be as low as that for SiO<sub>2</sub>/Si [7, 8, 10]. This approach also offers the potential for fabricating Ge nMOSFETs [7, 11, 12]. The record hole mobility for this structure can be as high as 596 cm<sup>2</sup>/Vs, achieved simultaneously with sub-nm EOT and low Dit of  $10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> [68].

#### 2.3.2 High-k/SiO<sub>2</sub>/Si-cap/Ge structure

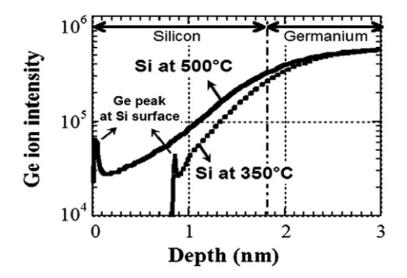

Many attempts have been made with different high-k materials including HfO<sub>2</sub> [77], ZrO<sub>2</sub> [78], LaAlO<sub>3</sub> [79] to find a suitable dielectric for Ge. Efforts have been made also to engineer the Ge interface [80-86]. However, the direct deposition of high-k layer on Ge does not produce the required interfacial characteristics due to large lattice mismatch. The insertion of a Si/SiO<sub>2</sub> layer between Ge and high-k gate stacks can improve the interface quality significantly [23]. Progresses have been made for Ge surface passivation with the growth of a Si-capping layer deposited at 500 °C [4]. A maximum  $I_{ON}$  of 350 µA/µm was achieved with 8 mono layer Si-cap and Vth control is optimal for thin passivation layer. However tradeoff is needed between these two, i.e. Ion & Vth. Epitaxial growth of silicon at lower temperature (350 °C) for gate dielectric was proposed as a solution to reduce the Equivalent Oxide Thickness (EOT) [86, 87], as low-temperature (350 °C) Si deposition shows lower Ge peak at Si surface in the SIMS signal in Fig. 2.4 [88], leading to a lower Dit than high temperature processes. In addition, EOT can be scaled down to 0.8 nm when combined with a reduced  $HfO_2$  layer [89].

The optimized Si capping thickness is found around 6 monolayers [84, 90]. The maximum critical thickness for plastic relaxation of the Si cap grown on Ge has been determined to be 12 MLs [91]. For thicker layer, relaxation defects were determined, whatever the Si growth process used. Thinner Si caps are considered as free of the relaxation defects [92].

Fig. 2.4 SIMS signal of Ge ion at different temperature [88]. Ge peak at Si surface is lowered at 350 °C deposition.

Possible physical origin of mobility enhancement was examined on Si-cap/Ge [93]. At low effective field (Eeff), the density of coulomb scattering is reduced due to the

separation of mobile charges from SiO<sub>2</sub>/Si interface, and at high Eeff, the reduction of surface roughness is due to the channel region moving from SiO<sub>2</sub>/Si to Si/Ge at high Eeff. The inserting of thin Si-cap layer plays an important role [93].

Promising results have been reported for Ge with Si-capping layer on top [4]. A record performance of Ion/Ioff:  $478\mu A/\mu m$  and  $37nA/\mu m$  is obtained at Vdd=-1 V with 1 nm EOT on a 65 nm Ge pMOSFET [4].

#### 2.4 Reliability issues in Ge MOSFETs

The quality of Ge MOSFETs has become good enough for their reliability study. As demonstrated in the state-of-the-art Ge-based pMOSFETs, interface states and oxide traps are the main causes of the Vth instability. Negative bias temperature instability (NBTI), positive bias temperature instability (PBTI) and Hot Carrier (HC) degradation are reviewed below.

#### 2.4.1 Positive charges (PCs) in oxide

Extensive works have been done on positive oxide charges in Si dioxide [94-97]. Various names have been used to describe the traps in the oxide, at the  $SiO_2/Si$  or Gate/SiO<sub>2</sub> interface, as summarized in Fig. 2.5 [98]. To explain the complex dependence of PCs on biases, time, and temperature, it has been proposed that there are three different types of PCs: AHT (As-grown Hole Trap), ANPC (Anti-Neutralization

Positive Charge), CPC (Cyclic Positive Charge) [94, 99, 100]. AHT has energy levels below the top edge of silicon valence band, i.e. Ev, making them easy to neutralize, but hard to charge. In contrast, ANPC has energy level above the bottom edge of silicon conduction band, i.e. Ec, making them hard to neutralize, but easy to charge. CPC is energetically located within the bandgap and can be repeatedly charged and discharged by alternating gate bias polarity.

|                       | Surface<br>traps/states            |                   | Interface<br>traps/states | Gate             |

|-----------------------|------------------------------------|-------------------|---------------------------|------------------|

|                       | Mobile ionic charge                |                   |                           |                  |

|                       | Neutral electron traps             |                   |                           |                  |

| Oxide traps           | Hole traps                         | Bulk traps e      | lectron traps             |                  |

|                       | E' defects/centers neutral centers |                   |                           |                  |

|                       | Fixed oxide charg                  | ge switchin       | g oxide traps             | SiO <sub>2</sub> |

| Border traps          | Anomalous positi                   | ve charge         | slow traps                |                  |

|                       | Slow states                        | Near-interfac     | e oxide traps             |                  |

| Surface               | Fast P <sub>t</sub>                | , defects/centers | Interface                 |                  |

| Traps/states          | states da                          | ngling Si bonds   | traps/states              |                  |

| Recombination centers | s Bulk S                           | Si defects D      | Oopant atoms              | Si               |

Fig. 2.5 Summary of various names for different types of traps at interface or in the bulk of SiO<sub>2</sub>/Si [98].

#### 2.4.2 Negative bias temperature instability (NBTI)

Negative bias temperature instability has been discovered in the early days of MOSFET development by Miura and Matukura in 1966 [101], as shown in Fig. 2.6. It has the highest impact in p-channel MOSFETs, which leads to severe degradation after stress.

The stress conditions for NBTI with thick gate dielectric stacks typically lie below the oxide electric field of 6 MV/cm under temperature from 100 to 300 °C, but can exceed 10 MV/cm in deeply scaled modern CMOS technology with thin gate stacks. One of the

increasing absolute Vth value due to NBTI.

most important parameters for MOSFET, threshold voltage (Vth), is degraded with an

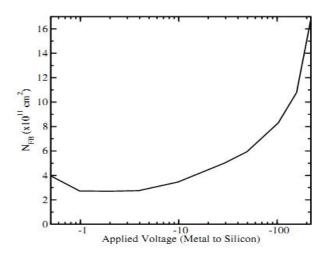

Fig. 2.6 The first report of NBTI effect by Miura and Matukura in 1966 [101]. It shows saturated value of the accumulated electron density at flat-band conditions  $N_{FB}$  for different stress voltages.

NBTI has become one of the biggest reliability threats to modern CMOS technologies [102, 103], as the equivalent oxide thickness keeps scaling down, and the oxide electric field becomes higher [64]. It is commonly observed that pMOSEFTs suffer NBTI during the "high" state logic in an inverter, which leads to higher Vth, lower driving current, and longer delay, potentially causing failure of logic circuits [103].

State-of-the-art Ge-based pMOSFETs also suffers NBTI [30]. It has been observed that NBTI of Si-capped Ge pMOSFETs is smaller than their Si counterparts [15, 23]. This

improvement corresponds to the increasing tunneling barrier for holes formed in the Ge channel [40, 41]. Lowering the temperature of epitaxial Si using  $Si_3H_8$  as a precursor is detrimental for Vth stability and hole mobility for thick Si film, but seems beneficial for achieving thinner EOT, lower interface states density, better Vth control and higher mobility for ultra-thin Si-cap layer [4]. Despite the fact that the initial interface state density of Si-cap/Ge was about 2 orders of magnitude higher than the typical values obtained on the Si/SiO<sub>2</sub> interface, the degradation due to NBTI stress remains within acceptable limits.

#### **2.4.3** Positive bias temperature instability (PBTI)

For conventional SiON gate stack, NBTI has larger impact on pMOSFETs, and PBTI can be dominant in nMOSFETs, especially with high-k gate stacks. After stressed at positive bias, a large amount of electrons can be injected into and trapped in the dielectric, leading to Vth shift, which is a severe constraint for reliability of Hf-based CMOS application [104].

Unlike the NBTI, very few PBTI works have been performed on pMOSFETs. However, it has been demonstrated that at the circuit level, PBTI affects both the n- and p-MOSFET in a digital inverter [105]. In analog circuits, the PBTI can also be a regular stress condition for pMOSFETs when the circuit is at the power-down-mode [106].

An important parameter of traps is the capture cross section (CCS), which can be used for modeling leakage, breakdown and device variability. In the first order model, it is assumed that the traps may have multiple-capture cross sections. The areal density of the trapped electrons, N, is described by,

$$N = \sum_{i=1}^{M} N_i \cdot \left[ 1 - exp\left(\frac{-\sigma_i \cdot Jt}{q}\right) \right]$$

(2.1)

where M is the number of measurable electron capture cross sections, and N<sub>i</sub> is the saturation density of traps with a capture cross section of  $\sigma_i$ .

A substantial electron trapping has been reported when the Si-cap/Ge device is stressed under a positive gate bias with two capture cross sections by measuring the transient gate current [16]. The larger one can reach  $\sim 10^{-12}$  cm<sup>2</sup> and reduces for higher Vgs, a signature of columbic attractive trap. This large trap was absent in Si samples with the HfO<sub>2</sub>/SiO<sub>2</sub> gate stack. The small one is  $\sim 10^{-14}$  cm<sup>2</sup> and acceptor-like, similar to that found in SiO<sub>2</sub> [107] and HfO<sub>2</sub> [20, 108, 109] in Si MOSFETs.

### 2.4.4 Hot carrier (HC) degradation

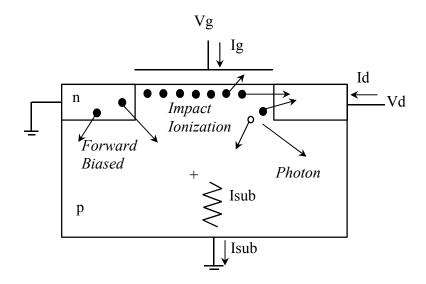

Hot carriers are the electrons or holes that gain high kinetic energy accelerated by high electric field. They are of great concern as these energetic particles can be injected into the oxide, forming oxide charges. These defects can cause threshold voltage shifts and gate leakage current. Hot carrier injection is significant when drain voltage (Vds) is equal to or even larger than gate voltage (Vgs), which will lead to impact ionization near drain region. These hot carriers degrade device performance, as shown in Fig. 2.7.

Fig. 2.7 Effect of hot electron near the drain of MOSFETs. The impact ionization leads to hot electronhole pairs.

HC degradation was confirmed to be highly detrimental for Si-cap/Ge devices, affecting their reliability [110]. A two orders of magnitude higher impact ionization rate is observed in Ge devices, when compared with their Si counterparts. By increasing the Si-passivation thickness, it is possible to improve the device performance in terms of mobility and subthreshold slope [66]. HC degradation can be significantly reduced and meet the required lifetime projections [111]. These results are promising for ensuring sufficient reliability performance of the Ge pMOSFET.

### 2.5 NBTI models

Various NBTI models have been proposed for Si MOSFETs, although little information

is available for Ge MOSFETs. A review is given below on the Reaction–Diffusion (R– D) model, Hole Trapping Model, Two Stage Model, and As-grown-Generation (A-G) Model.

### 2.5.1 Reaction-Diffusion Model

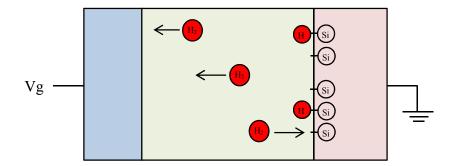

The reaction-diffusion(R-D) model was first proposed by Jeppson and Svensson in 1977 [112] to describe the NBTI phenomenon. Two processes are included to model the device degradation, as illustrated in Fig. 2.8.

Fig. 2.8 Schematic presentation of the reaction-diffusion (R-D) model proposed by Jeppson and Svensson [112].

One process is the electrochemical reaction at the  $Si/SiO_2$  interface, which breaks the Si-H bond to form the dangling  $Si^{\bullet}$  bond, an electrically active interface state and active hydrogen species  $H^{\bullet}$ ,

$$\mathrm{Si} - \mathrm{H} = \mathrm{Si}^{\bullet} + \mathrm{H}^{\bullet}. \tag{2.2}$$

The other process is the transport or diffusion of the hydrogen related species from the interface into the oxide bulk or poly-Si gate,

$$H^{\bullet}$$

(interface)  $\rightarrow$   $H^{*}(Bulk)$  (2.3)

In the standard R-D formulation, the diffusion kinetics is assumed as,

$$\frac{\partial N_{it}}{\partial t} = K_F (N_0 - N_{it}) - K_R N_{it} (N_{H^*})^{1/a}$$

(2.4)

where x =0 is the location at the interface of Si/SiO<sub>2</sub> and x > 0 is in the oxide, N<sub>it</sub> is the number of interface states generated at any given time during stress, N<sub>0</sub> is the initial Si-H bonds and N<sub>H</sub><sup>•</sup> is the H<sup>•</sup> concentration at the interface. The forward dissociation rate ( $K_F$ ) and the re-passivation rate ( $K_R$ ) are controlled by temperature and oxide electric field. a is the order of reaction. If a =1, neutral atomic H<sub>0</sub> is assumed to be the species during diffusion process, a =2 for the molecular hydrogen diffusion, H<sub>2</sub>. For each generated interface state, the number of hydrogen released should be equal to that diffused into oxide, thus

$$N_{it}(t) = \int_0^\infty N_{H^*}(x,t) dx$$

(2.5)

The recent R-D model is applied only to the interface state generation but oxide charges are also generated in the dielectric [113].

### 2.5.2 Hole Trapping Model

The hole trapping model is based on the fact that there are trapped charges in the oxide, contributing to the NBTI [113]. The R-D model had been modified recently to include hole trapping in order to simulate the recovery kinetics and dynamic stress [114, 115].

hole trapping are shown in Fig. 2.9 [95].

Poly  $qV_g$   $qV_g$  $qV_g$

Fig. 2.9 Description of three possible mechanisms for Hole trapping [95]. Traps are positively charged when occupied by a hole and are neutral when empty.

Hole traps are positively charged when occupied by a hole and are neutral when empty. In thermal equilibrium, hole traps with energy below the Fermi level Ef are neutral and become charged when it is above Ef, contributing to the Vth instability. When the device is working in inversion, the energy level of the oxide trap at a distance x from  $SiO_2/Si$  interface is given as,

$$E = E_t + q \cdot E_{ox} \cdot x, \tag{2.6}$$

where  $E_t$  is the energy level of the traps and  $E_{ox}$  is the oxide electric field. Thermal equilibrium is achieved by two types of charge exchange mechanism. Trap below Si

valence band (Ev) is able to be charged and discharged through elastic hole tunneling at the same energy level (path 1). Hole traps at x' above Ev get activated by two different mechanisms. First, path 2 and 3 form a two-step process, as the channel hole could interact with interface states (2), which exchange charge with oxide traps at Et'' by direct tunneling (3). Secondly, a channel hole could tunnel elastically to the excited energy level Et' at x' (4) and then relax to the ground state Et'' by multi-phonon assisted processes (5).

Distribution of the time constant has to be considered for different processes and the total time constant associated with the hole trapping is given by

$$\frac{1}{\tau} = \frac{1}{\tau_1} + \frac{1}{\tau_{23}} + \frac{1}{\tau_{45}}$$

(2.7)

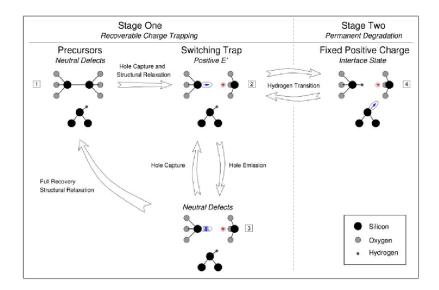

### 2.5.3 Two Stage Model

The two stage model [117] is based on the multiphonon-field-assisted tunneling (MPFAT) [118, 119] and Harry-Diamond-Laboratories (HDL) model [120], which is initially developed for the emission of particles from deep traps and switching oxide traps, respectively.

In the first stage, holes can be trapped into oxygen vacancies near interface by the MPFAT mechanism. The defect transforms into a positively charged E' center after the hole capture. In this configuration, hole can be charged and discharged repeatedly. But only in neutral state 3, the E' center can be fully recovered. In the second stage, the

increased hole concentration enhances the creation of slowly recoverable defects, probably Pb-centers in SiO<sub>2</sub>. It is assumed that the transition of hydrogen is much slower than the hole capture or emission process.

Fig. 2.10 The two stages for the trapping dynamics [117]. Stage one, the recoverable charge trapping and stage two, the permanent degradation.

### 2.5.4 As-grown-Generation (A-G) Model

Although extensive studies have been carried out on NBTI models [96, 117], an agreement has not been reached. It was reported that the R-D model contradicted with the experimental data for the recovery kinetics, suggesting a non-diffusion-limited process [96]. On the other hand, the two stage model has too many adjustable fitting parameters [97]. Stress acceleration is widely used to assess device lifetime in the semiconductor industry. A model must have prediction ability.

Three different types of positive charges in the dielectric have been discussed in Section 2.4.1: anti-neutralization positive charges (ANPC), cyclic positive charges (CPC), and as-grown hole trapping (AHT), as shown in Fig. 2.11. AHT is as-grown defects, while CPC and ANPC are generally considered as defects generated in Si MOSFETs. For the thin oxide MOSFETs, power law empirical model was proposed [121] and supported by early works with slow DC measurement [121-123], which was dominated by generation of defects.

$$\Delta V_{th} = C * |V_{ov}|^{\gamma} t^n , \qquad (2.8)$$

And the charging of AHT generally follows the first order reaction model [124],

$$\Delta N_{ot} = N \left[ 1 - exp(-\sigma Q_{inj}) \right] , \qquad (2.9)$$

where  $\Delta Not$  is trap charge density, Qinj is hole injection level and  $\sigma$  is the capture cross section.

As-grown Generation (A-G) Model [125] was proposed to explain data with fast Pulse measurement by combining these two and has been evaluated based on the understanding of different positive charges by researchers at LJMU

$$\Delta V_{\rm th} = A t^{\rm n} + B [1 - \exp(-t/t^*)]$$

(2.10)

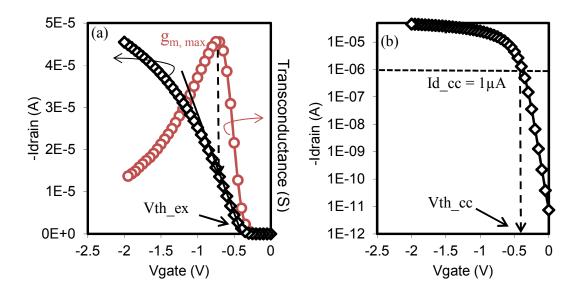

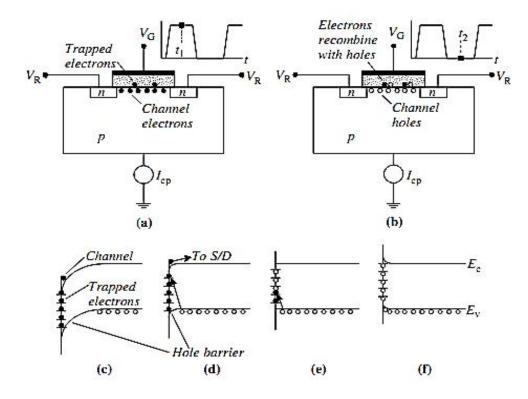

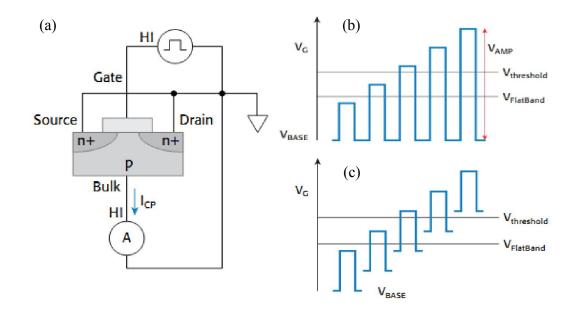

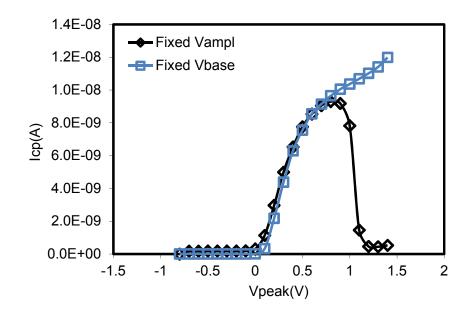

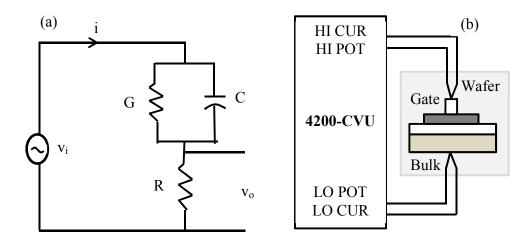

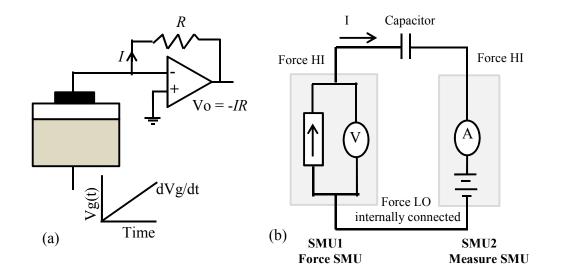

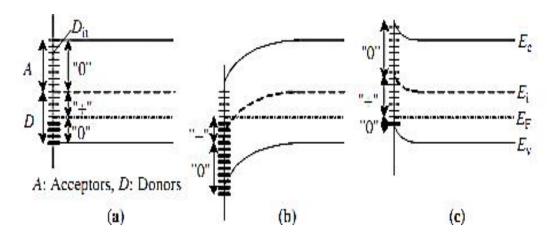

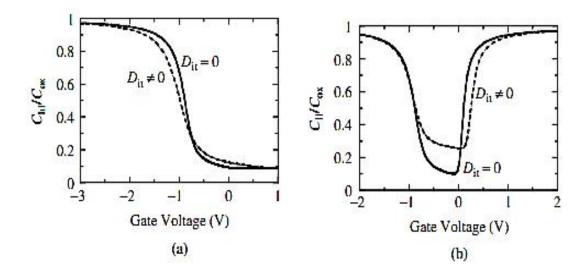

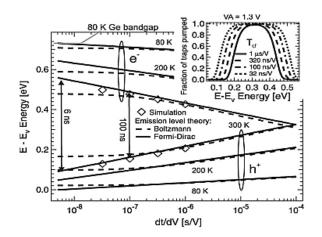

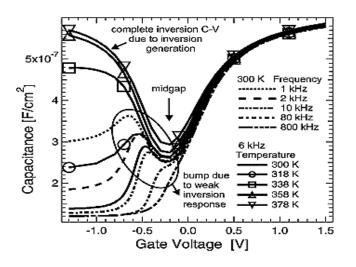

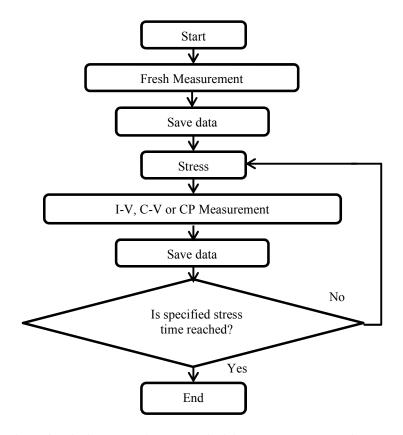

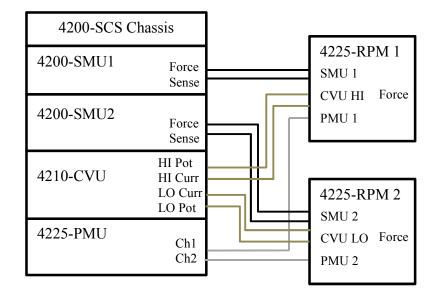

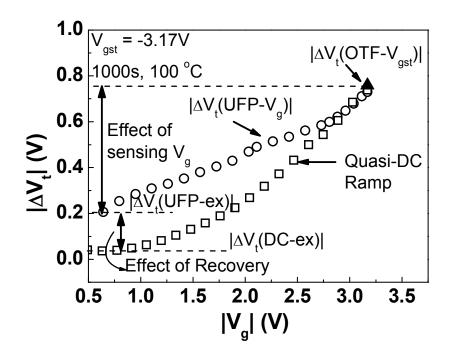

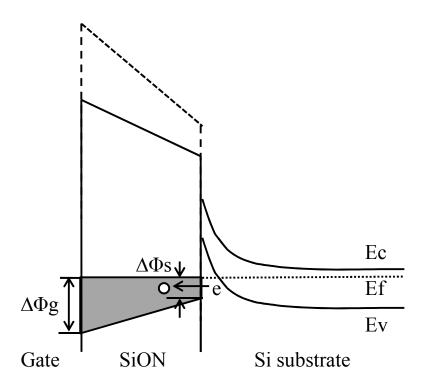

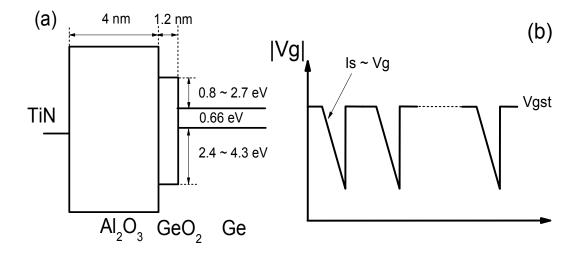

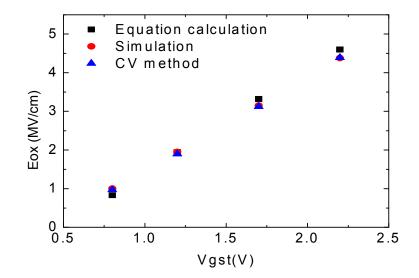

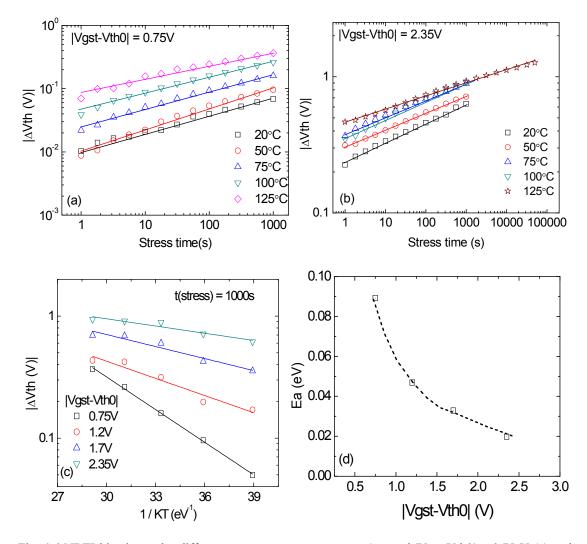

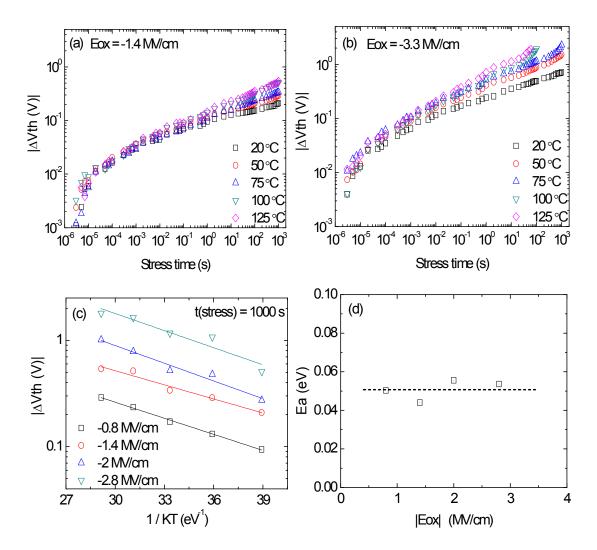

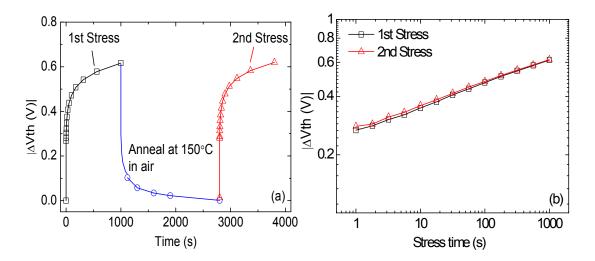

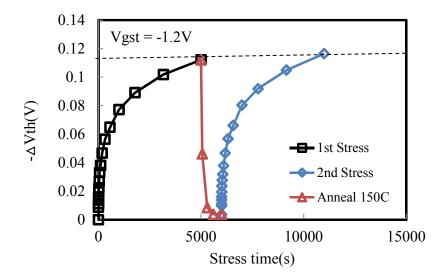

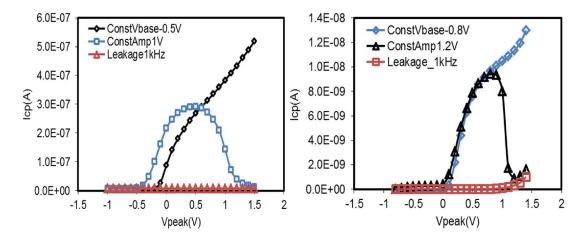

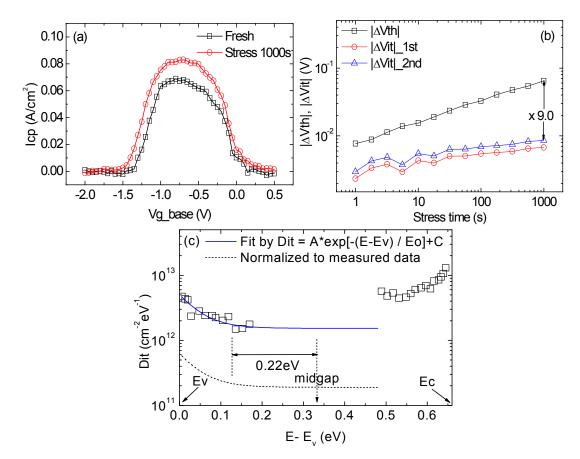

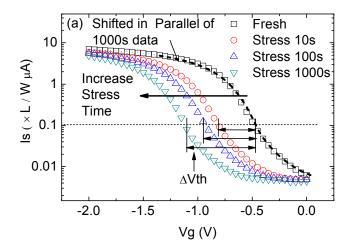

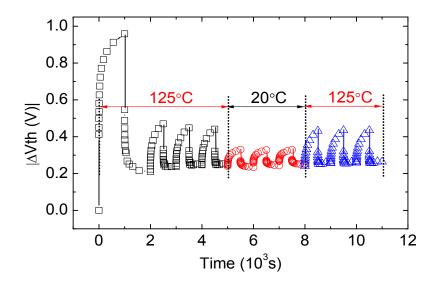

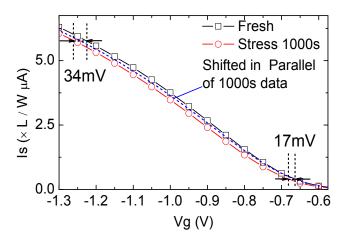

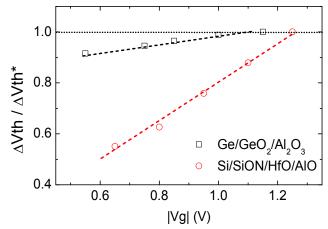

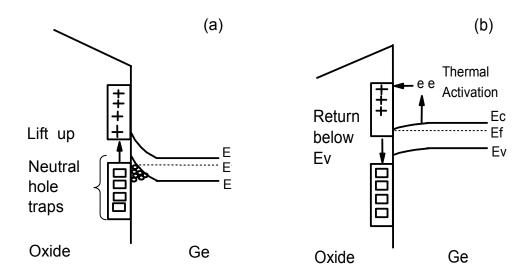

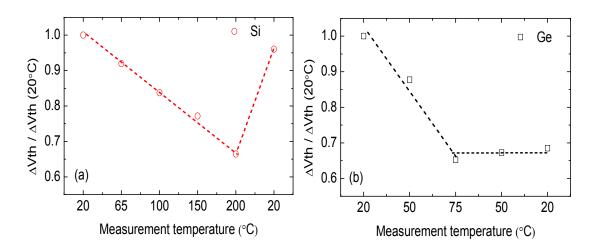

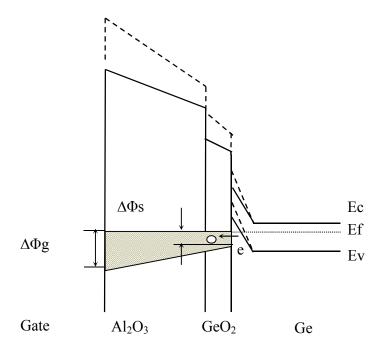

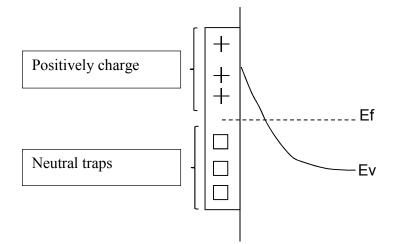

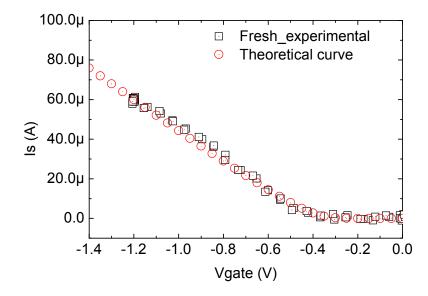

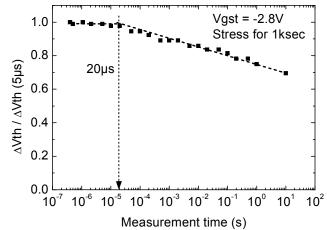

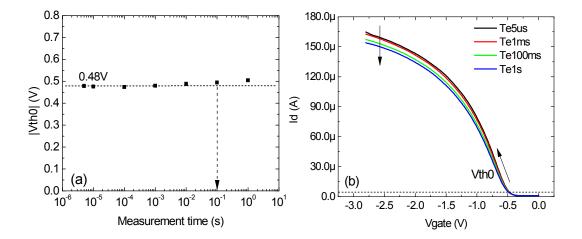

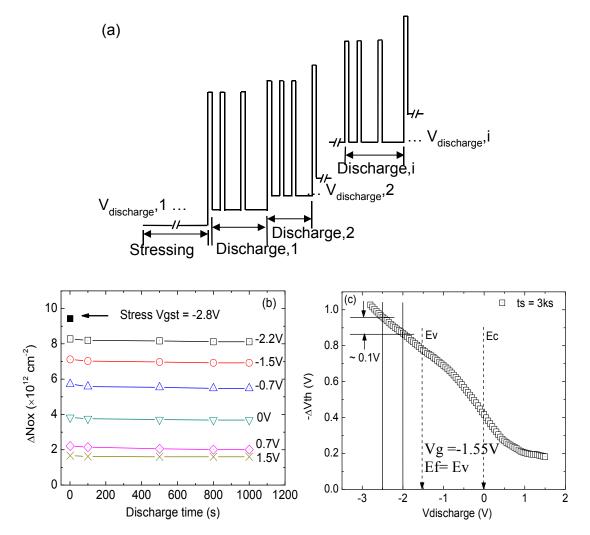

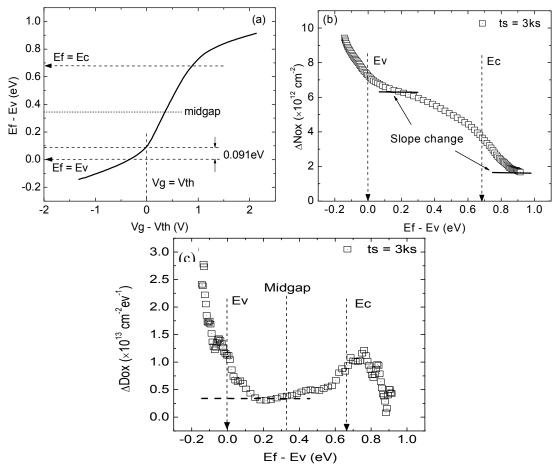

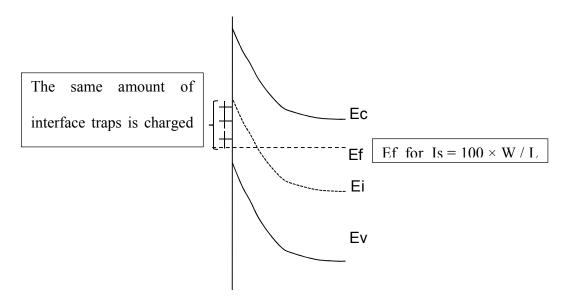

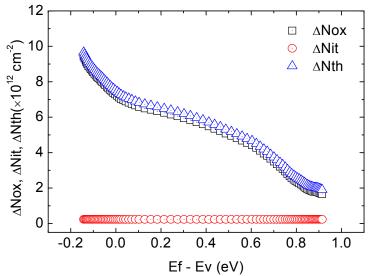

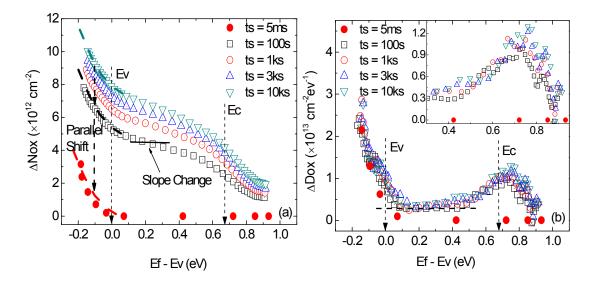

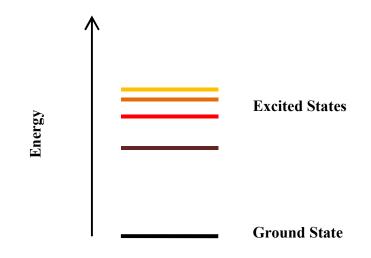

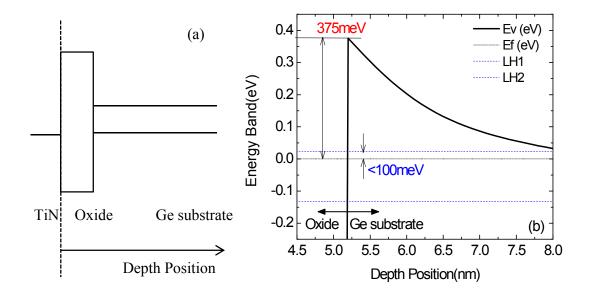

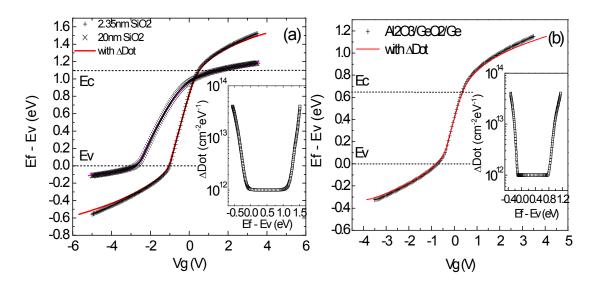

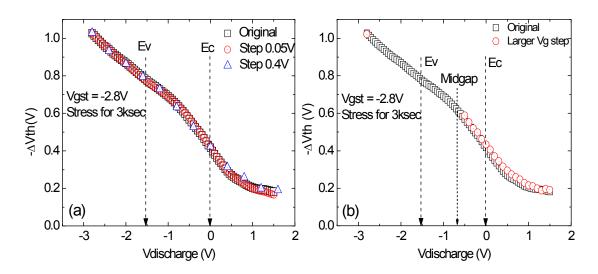

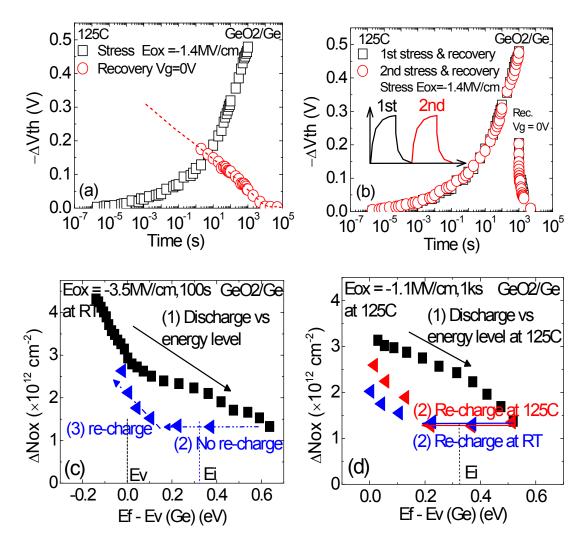

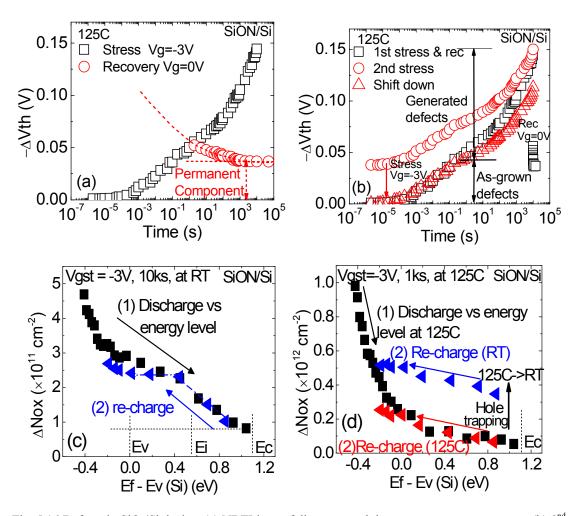

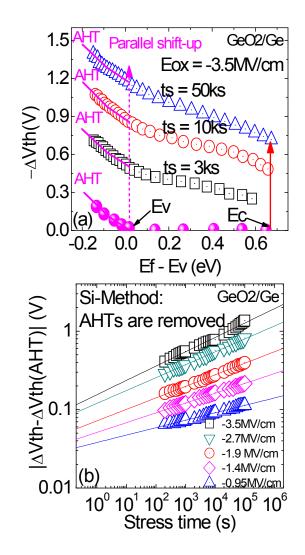

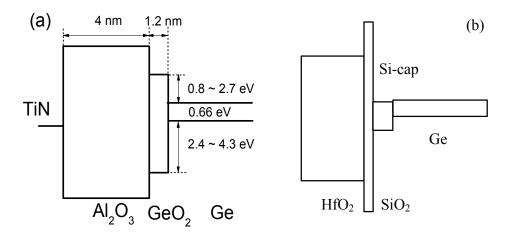

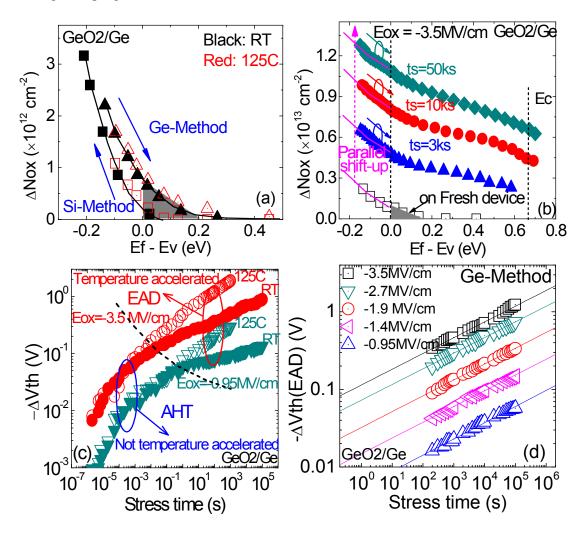

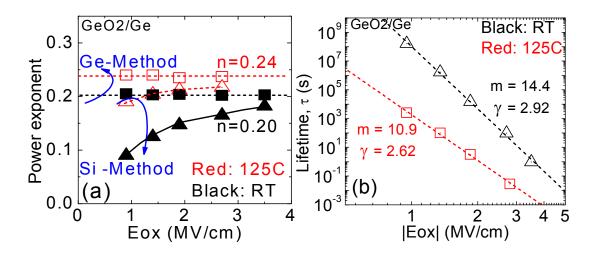

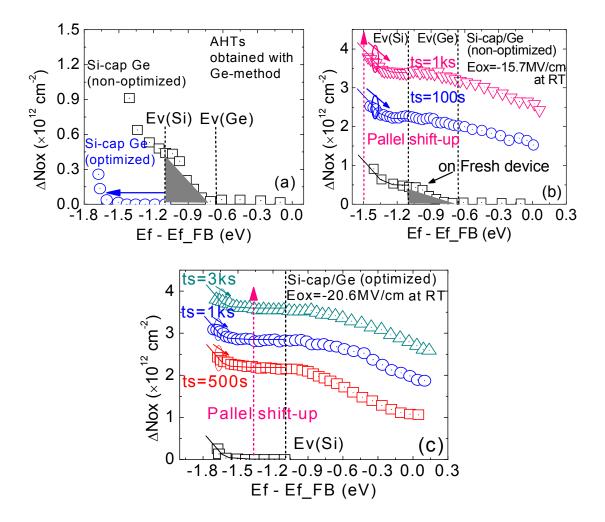

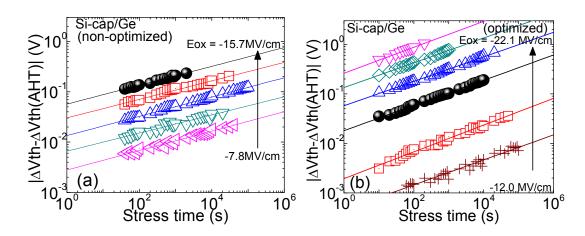

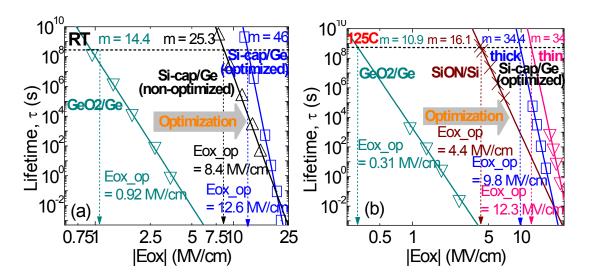

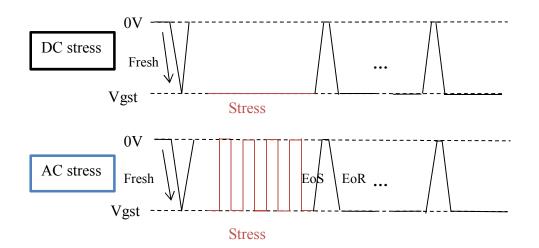

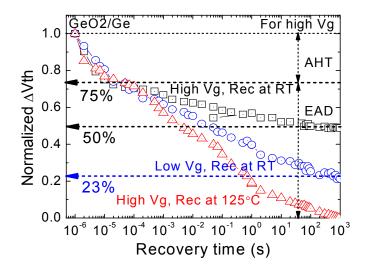

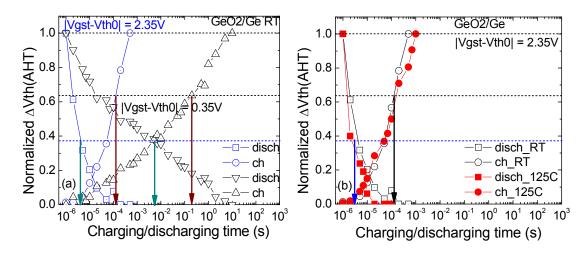

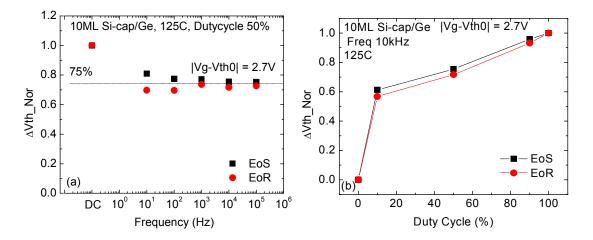

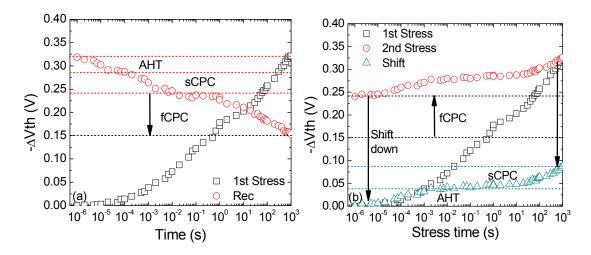

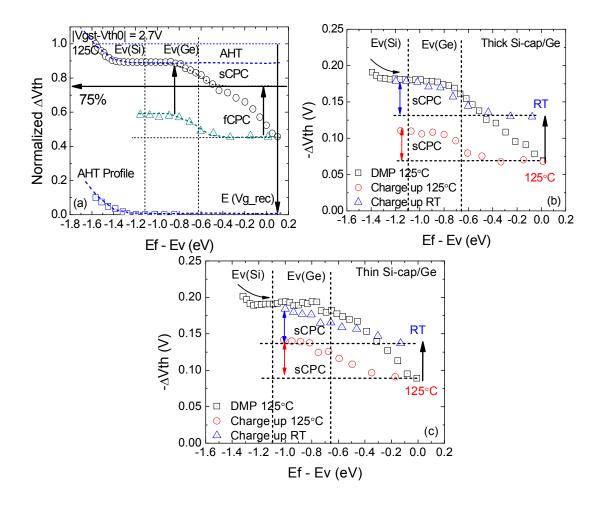

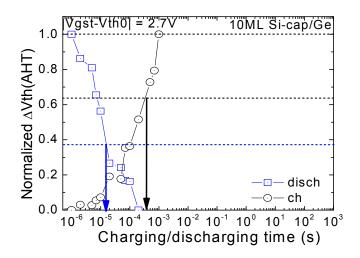

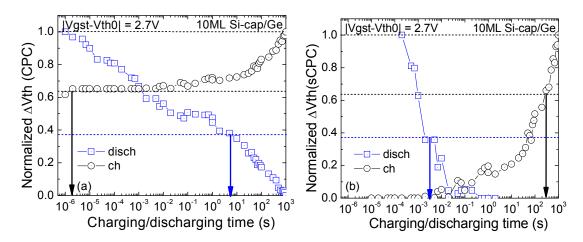

where 'A', 'n', 'c', and t\* are constants and were obtained by fitting test data with a least square technique, for a given stress temperature and bias.