# ELECTRON TRAPPING IN GATE DIELECTRICS AND NBTI OF MOSFETs

# **MO HUAI CHANG**

A thesis submitted in partial fulfillment of the requirements of Liverpool John Moores University for the degree of Doctor of Philosophy

# November 2006

# Acknowledgements

I would like to thank Prof. J. F. Zhang for his continuous guidance, advice, encouragement and fruitful discussions throughout the project. Without his investment of time and efforts, this project would never reach the fruition.

I also deeply appreciate Dr. C. Z. Zhao for his advice and support throughout the project. Many thanks are given to other members in our research group, Dr. W. D. Zhang, Mr. M. Zahid and Mr. Y. G. Wang for their extreme helpfulness.

Finally, I would like to express my deeply gratitude to my family, especially my parents for their understanding, support and encouragement during all these years.

## **Summary**

The transistors in integrated circuits have increased in speed and reduced in cost and power consumption because of reduced transistor size in successive technology generations. However, it is not possible to reduce the voltage to the same scaling factors so the electric fields have increased. At elevated field, carriers can be easily injected into the oxide and lead to a gradual degradation of the oxide. Generated defects can trap some of the injected carriers and change the electrical behavior of the MOSFET. Eventually a sudden breakdown occurs as the generation sums up to a critical amount.

Generation of acceptor-like electron traps in gate oxide is an important source for the instability of MOS transistors. Agreements have not been reached on the dominant damaging species. When injected electrons were orders of magnitude higher than injected holes, it was proposed that hydrogen release and its subsequent transportation through the oxide dominated the generation. It was also reported that holes were more efficient in creating electron traps than electrons. However, the physical process for the hole-induced generation is not clear. The release and subsequent transportation of hydrogenous species for hole-induced electron trap generation is investigated in Chapter 3. Effects of hydrogenous species released near the two interfaces and in the bulk of oxides are examined. It is found that the release and subsequent transportation of hydrogenous species are not important for the hole-induced generation. Results support that holes can interact directly with the oxide to generate electron traps without going through hydrogen as intermediate species.

Furthermore, the capture cross sections of generated acceptor-like electron trap are not unambiguously determined and there are confusions on how many capture cross sections genuinely existing. The dependence of trap density for a given capture cross section on stress level is not clear, either. To fill to knowledge gap, the electron trapping kinetics is investigated in Chapter 4. There are a number of obstacles for

- iii -

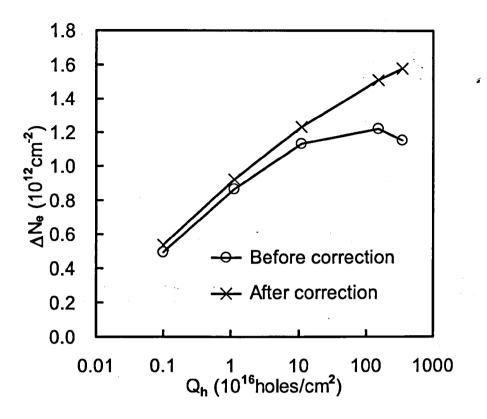

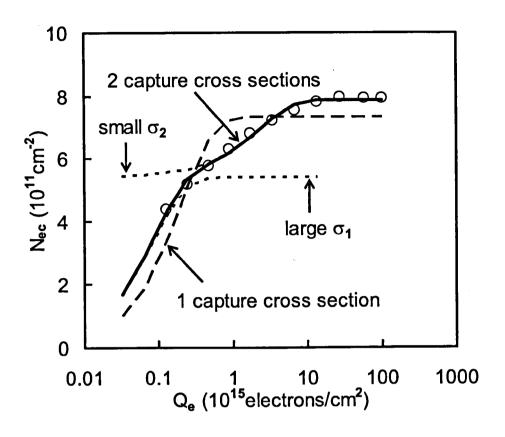

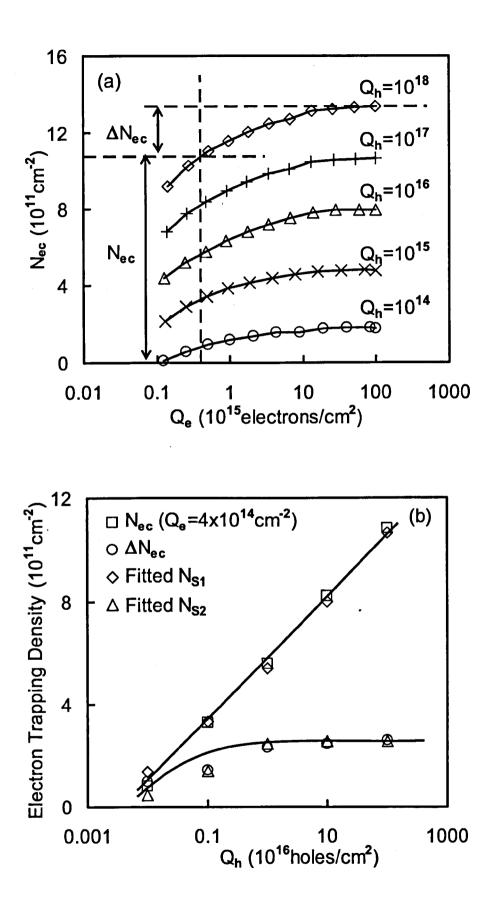

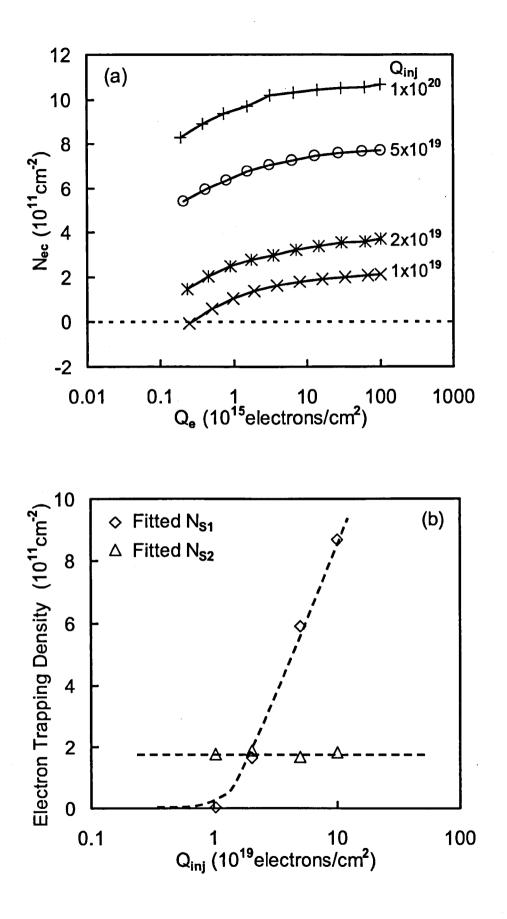

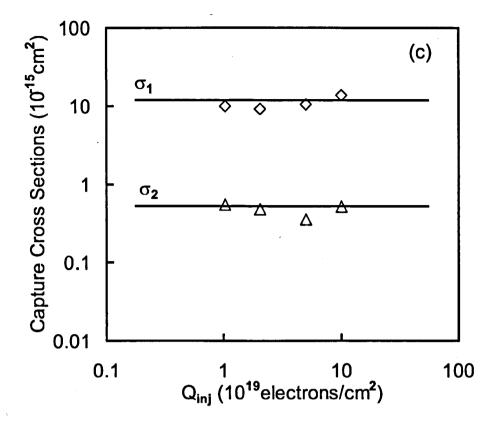

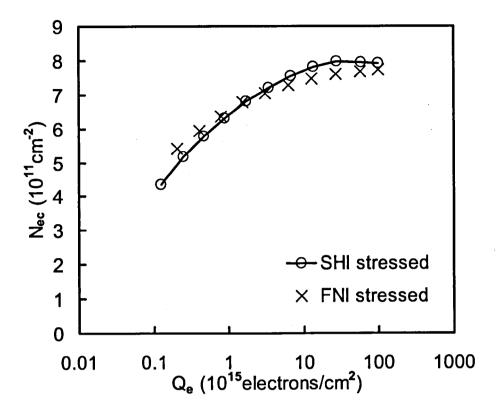

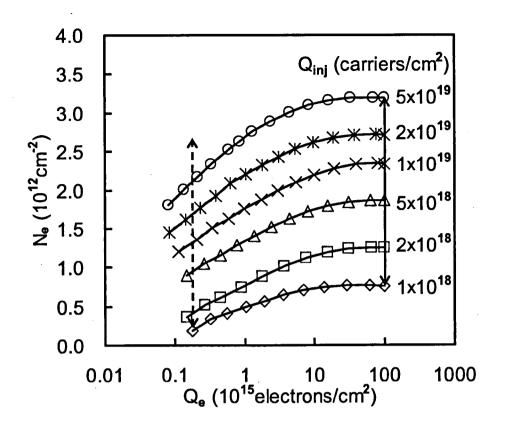

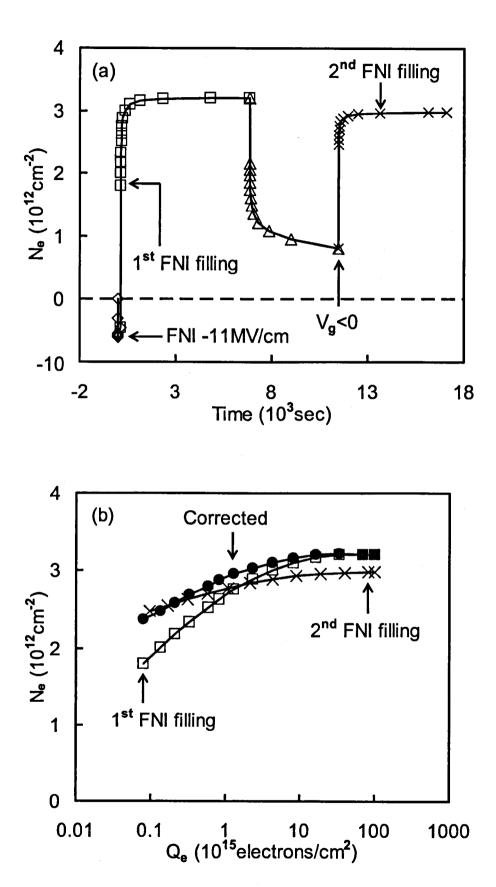

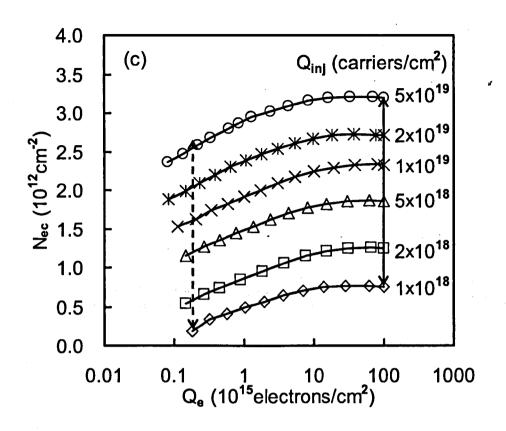

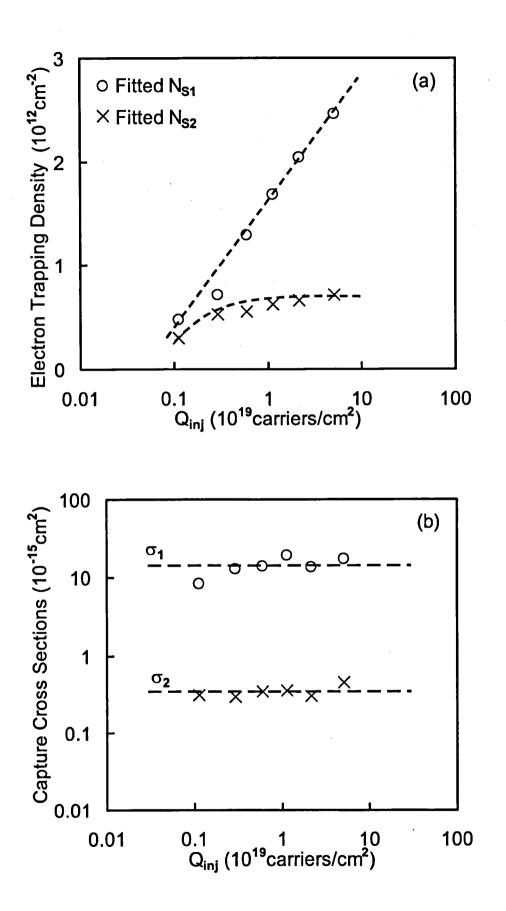

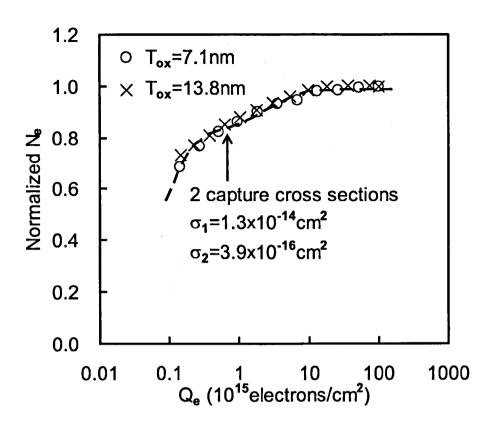

such an investigation, including the simultaneous occurrence of trapping and trap generation, stability of trapping, and effects of positive charges. Through careful selection of experimental conditions and testing samples, we have been able to overcome them. In particular, recent work at this university in this area has allowed us to develop a new method for correcting the effect of positive charges. After removing all uncertainties, a capture cross section as large as  $10^{-13} \sim 10^{-14}$  cm<sup>2</sup> is found for the generated acceptor-like trap. It is shown that electron trapping follows the first order model and there is also a smaller capture cross section in the region of  $10^{-15} \sim 10^{-16}$  cm<sup>2</sup>. For the first time, it is shown that the density of the larger trap increases with stress, but the density of the smaller trap clearly saturates.

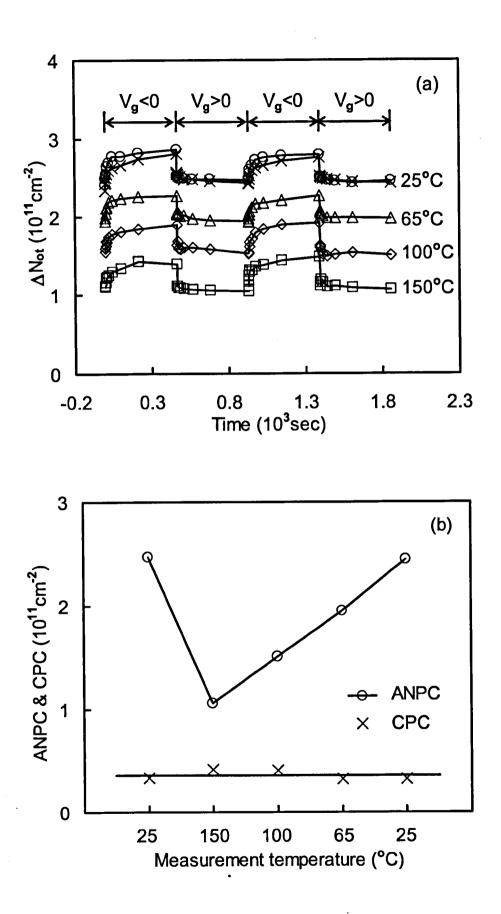

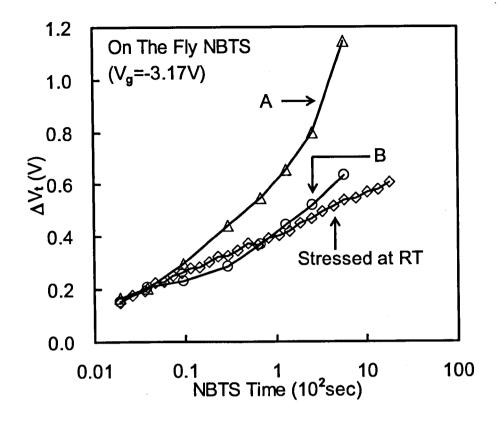

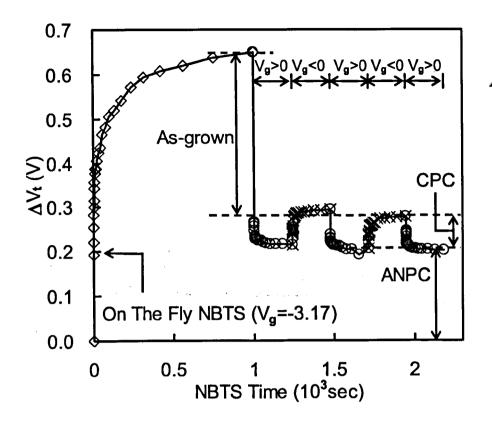

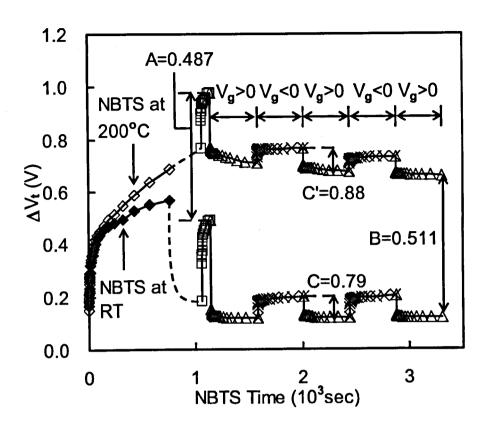

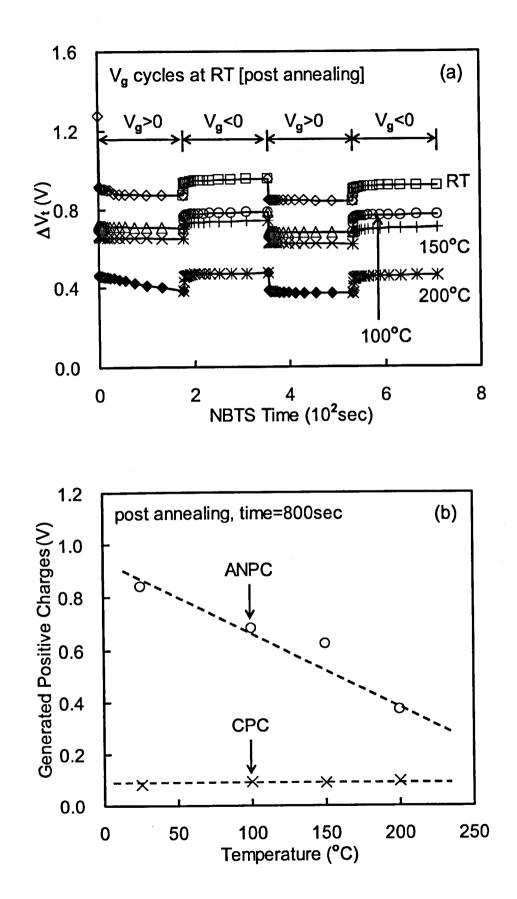

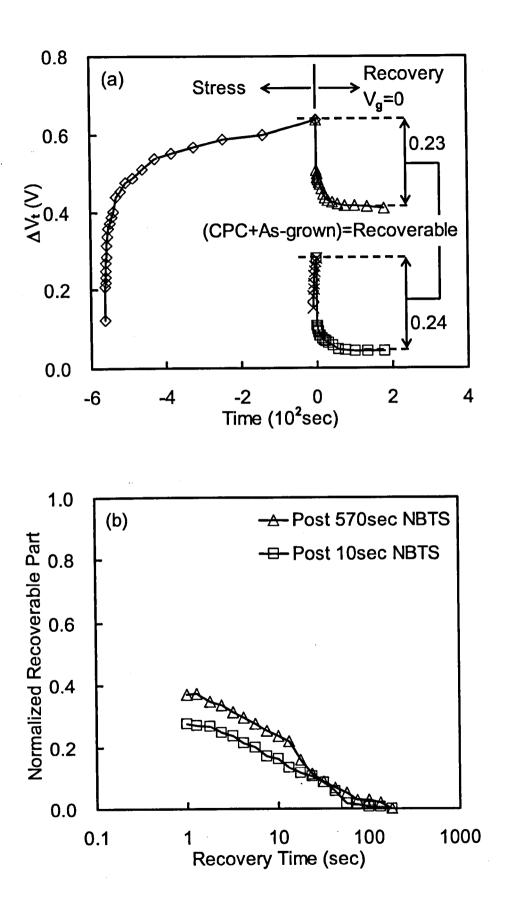

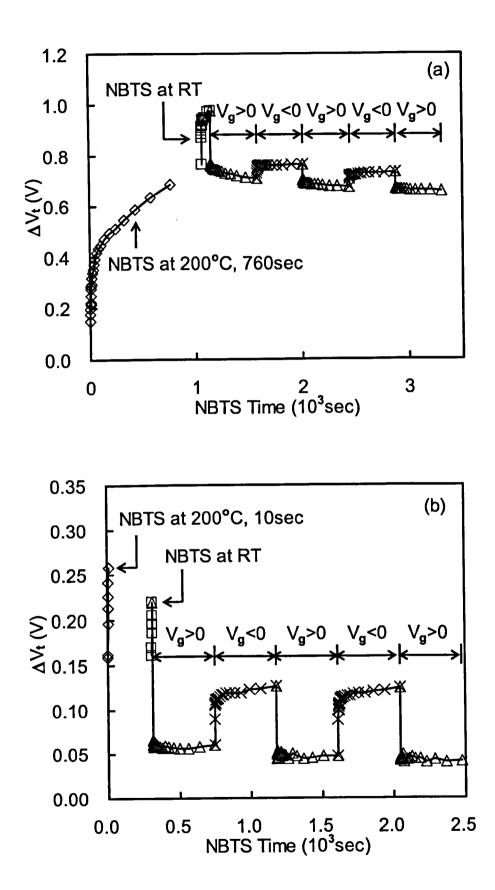

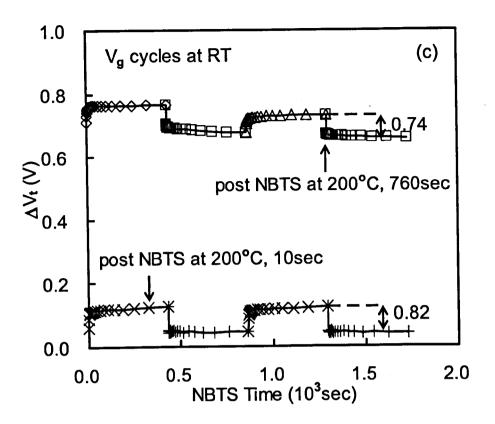

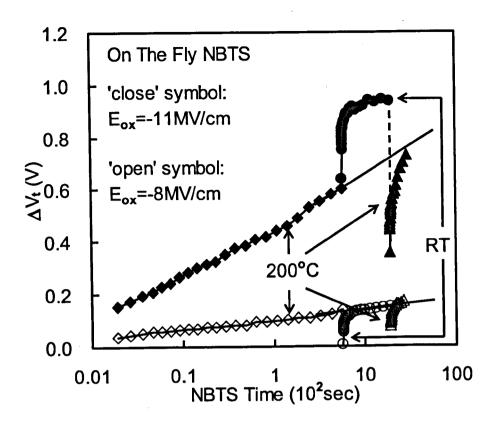

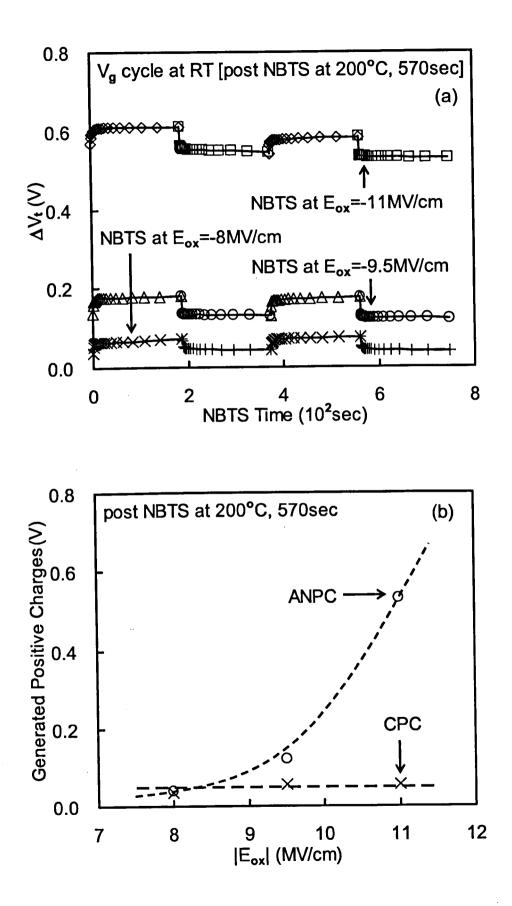

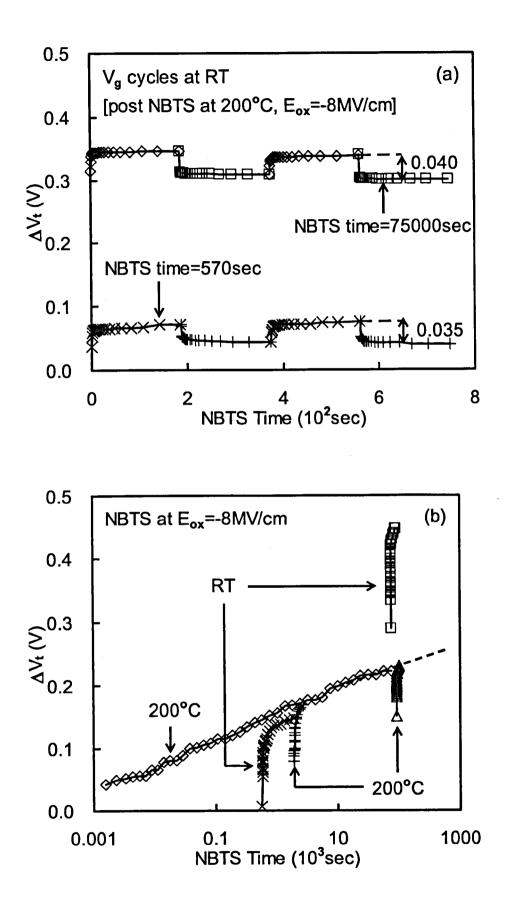

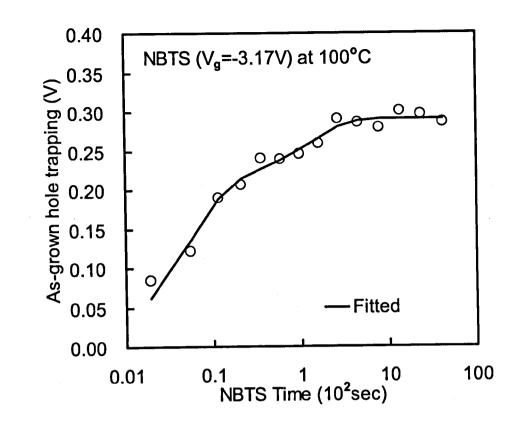

As the nitrogen concentration in silicon oxynitrides (SiON) increases, the negative bias temperature instability (NBTI) becomes a limiting factor for device lifetime. Despite recent efforts, there are confusion and issues remaining unsolved. One of them is how important positive charge formation in SiON is for NBTI and whether all positive charges are the same type. Positive charges formed in SiON during negative bias temperature stresses (NBTS) is investigated in Chapter 5. It is shown that NBTS can induce three different types of positive charges: as-grown hole trapping, anti-neutralization positive charges (ANPC) and cyclic positive charges. Efforts have been made to search for the features of NBTI, which cannot be explained without involving positive charges. It is unambiguously identified that the impact of measurement temperature on NBTI originates from only one types of defect: ANPC. By using 'On-The-Fly' measurement technique, the positive charge density observed in a 2.7 nm SiON can reach the up half of  $10^{12}$  cm<sup>-2</sup>, which is comparable with the positive charges reported for relatively thick  $SiO_2$  (> 5 nm). The relative importance of positive charge formation depends on measurement interruption time. The shorter the interruption, the more important positive charges become for NBTI.

Table of contents

| 4. Tra | pping ]                                                    | Kinetics of Electron Traps Generated in Silicon Dioxides         | 104   |

|--------|------------------------------------------------------------|------------------------------------------------------------------|-------|

| 4.1.   | Introd                                                     | uction                                                           | 104   |

| 4.2.   | Trapp                                                      | ing kinetics of electron traps generated under SHI               | * 106 |

|        | 4.2.1.                                                     | Effects of positive charges                                      | 107   |

|        |                                                            | 4.2.1.1. Low stress level                                        | 107   |

|        |                                                            | 4.2.1.2. High stress level                                       | 108   |

|        |                                                            | 4.2.1.3. Support for the correction method                       | 109   |

|        | 4.2.2.                                                     | Trapping kinetics and trap properties                            | 110   |

|        |                                                            | 4.2.2.1. The first order model                                   | 110   |

|        |                                                            | 4.2.2.2. Support for the presence of two capture cross sections  | 111   |

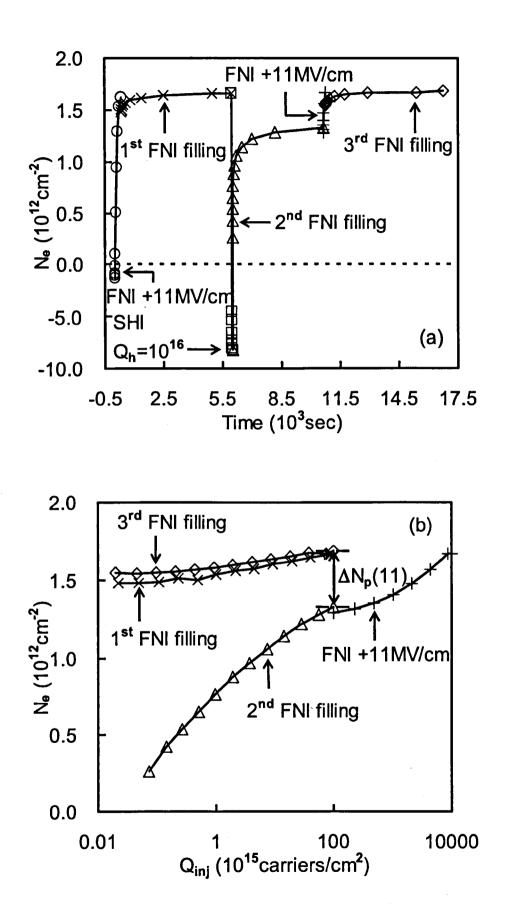

| 4.3.   | Trapp                                                      | ing kinetics of electron traps generated under FNI               | 113   |

|        | 4.3.1.                                                     | Difficulties                                                     | 113   |

|        |                                                            | 4.3.1.1. Positive charges formed during FNI                      | 113   |

|        |                                                            | 4.3.1.2. Separation of trap creation from filling                | 115   |

|        | 4.3.2.                                                     | Trapping kinetics                                                | 115   |

| 4.4.   | Trapp                                                      | ing kinetics of electron traps generated on thick oxides         | 116   |

|        | 4.4.1.                                                     | Trapping kinetics                                                | 116   |

|        | 4.4.2.                                                     | A comparison of traps generated in oxides of different thickness | es    |

|        |                                                            |                                                                  | 117   |

| 4.5.   | Concl                                                      | usion                                                            | 118   |

| Refe   | rences                                                     | ,                                                                | 119   |

|        |                                                            |                                                                  |       |

| 5. Neg | ative E                                                    | ias Temperature Instability                                      | 149   |

| 5.1.   | Introd                                                     | uction                                                           | 149   |

| 5.2.   | Investigation of NBTI using traditional measurement method |                                                                  |       |

|        | 5.2.1.                                                     | Typical NBTI generation                                          | 151   |

|        | 5.2.2.                                                     | Types of positive charges                                        | 151   |

|        | 5.2.3.                                                     | Effects of experiment parameters on generated positive charges   | 153   |

|        |                                                            | 5.2.3.1. Stress time                                             | 153   |

|        |                                                            | 5.2.3.2. Thermal stability                                       | 154   |

5.2.3.3. Stress temperature

-----

- vi -

154

| 2. Experimental Facilities and Techniques |                                               |                                                               | 30         |

|-------------------------------------------|-----------------------------------------------|---------------------------------------------------------------|------------|

| 2.1.                                      | Introd                                        | uction                                                        | 30         |

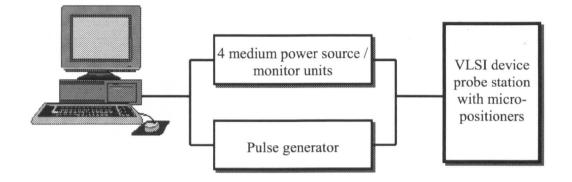

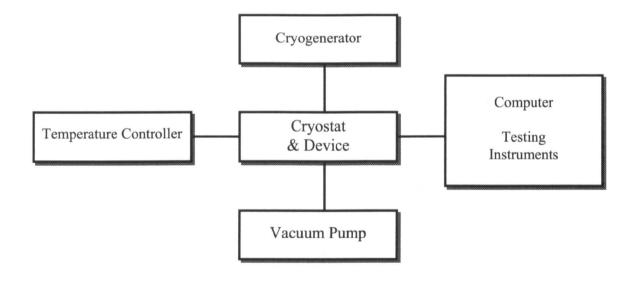

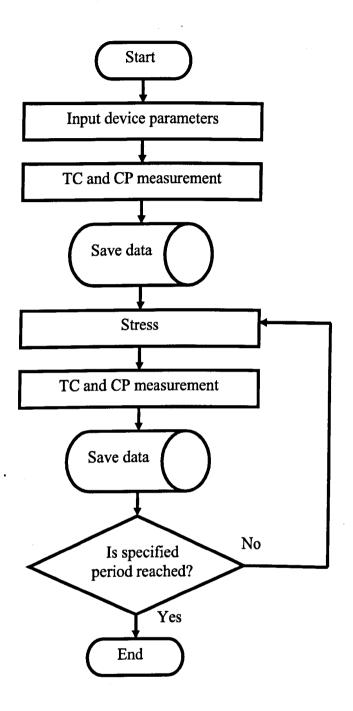

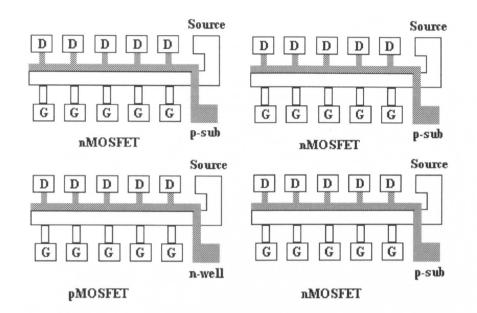

| 2.2.                                      | Syster                                        | n and equipment                                               | 30         |

| 2.3.                                      | Samp                                          | les used in experiments                                       | 32         |

| 2.4.                                      | Techniques for characterizing the degradation |                                                               | 32         |

|                                           | 2.4.1.                                        | Measurement of interface states                               | 33         |

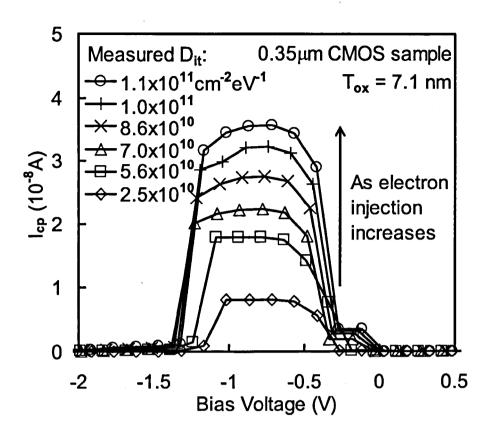

|                                           |                                               | 2.4.1.1. Basic principle of the charge pumping technique      | 33         |

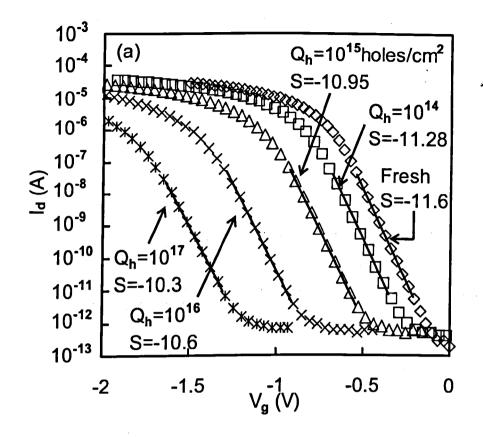

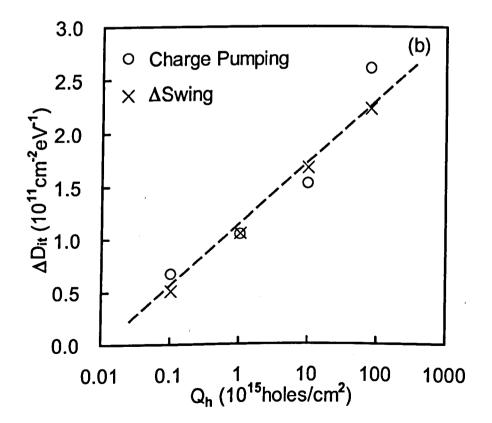

|                                           |                                               | 2.4.1.2. Extraction of interface state density from subthresh | hold swing |

|                                           |                                               |                                                               | 36         |

|                                           | 2.4.2.                                        | Measurements of oxide charges                                 | 37         |

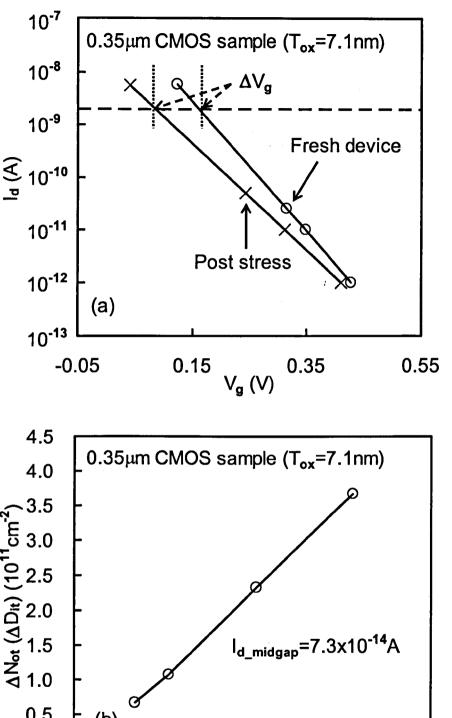

|                                           |                                               | 2.4.2.1. $I_d$ - $V_g$ shift in the subthreshold region       | 37         |

|                                           |                                               | 2.4.2.2. $I_d$ -V <sub>g</sub> shift in the midgap region     | 39         |

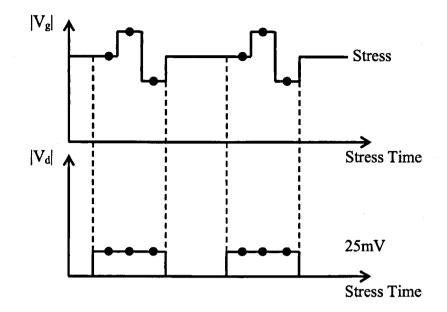

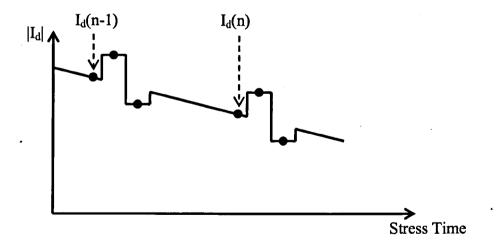

|                                           | 2.4.3.                                        | On-The-Fly measurement technique                              | 40         |

| 2.5.                                      | Techn                                         | iques for stressing the devices                               | 42         |

|                                           | 2.5.1.                                        | High field injection technique                                | 42         |

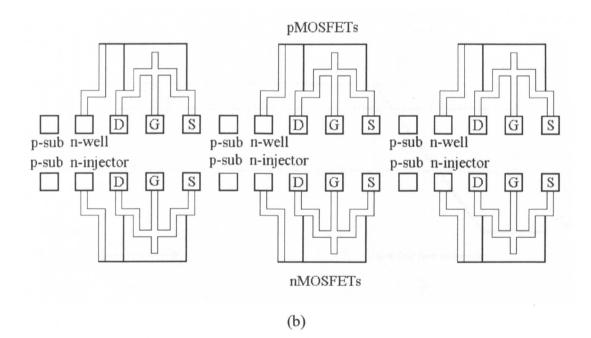

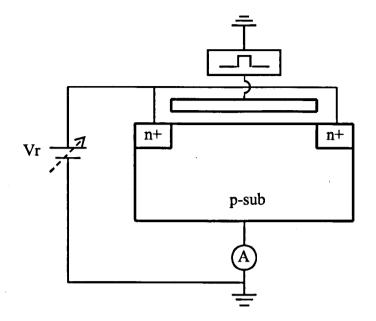

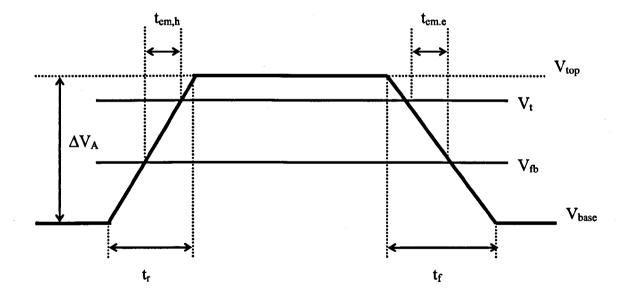

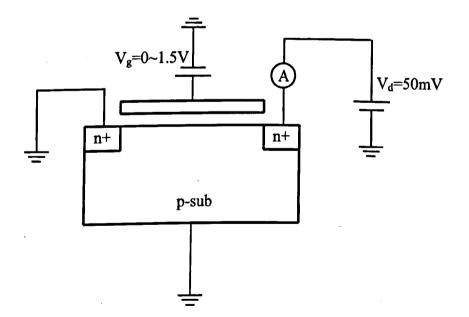

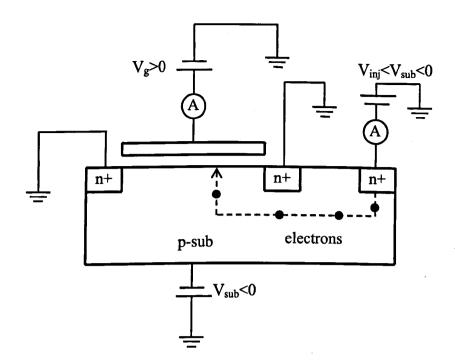

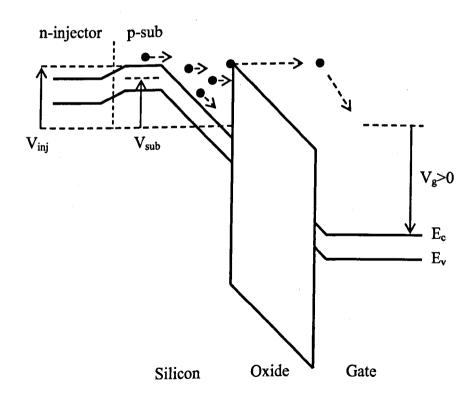

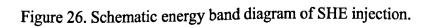

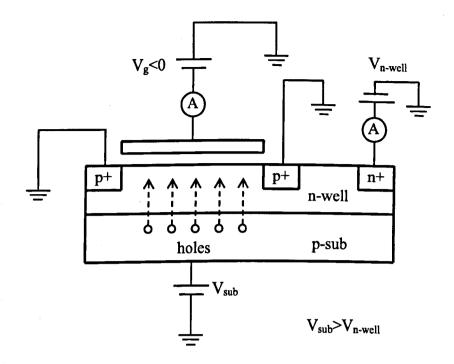

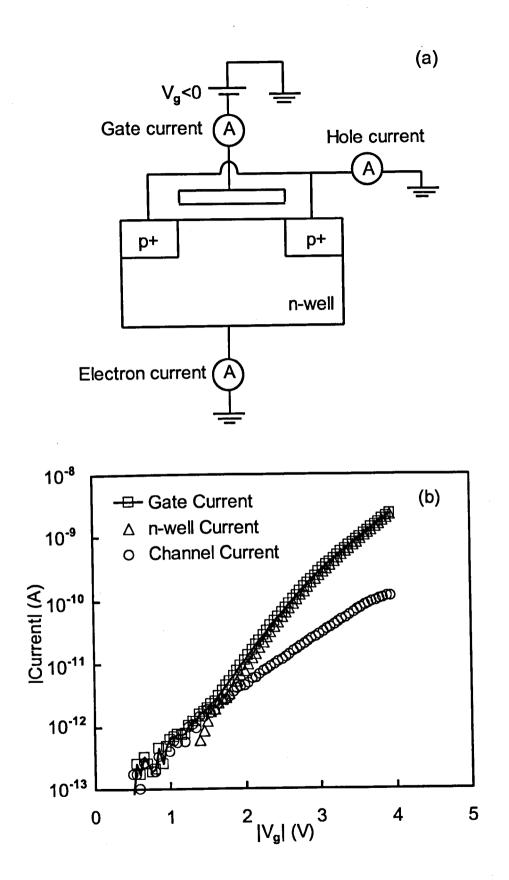

|                                           | 2.5.2.                                        | Substrate hot carrier injection techniques                    | 43         |

| Refe                                      | References                                    |                                                               |            |

|                                           |                                               |                                                               |            |

| 3. Role of Hydrogen in Hole-Induced Electron Trap Generation |                                                                    |    |

|--------------------------------------------------------------|--------------------------------------------------------------------|----|

| 3.1.                                                         | Introduction                                                       | 68 |

| 3.2.                                                         | Experimental conditions                                            | 69 |

| 3.3.                                                         | Hydrogen species released near the Si/SiO2 interface               | 71 |

|                                                              | 3.3.1. Bombardment effects on electron trap generation             | 71 |

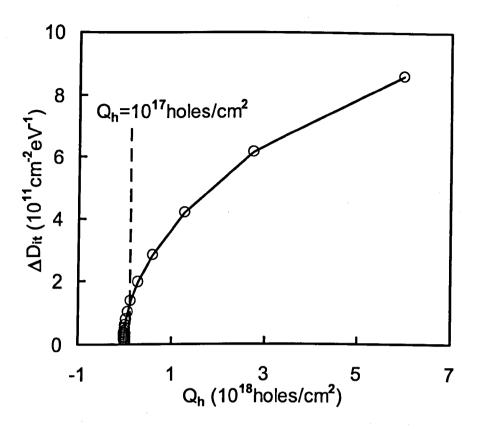

|                                                              | 3.3.2. Threshold for electron trap generation and hydrogen release | 73 |

| 3.4.                                                         | Hydrogen species released in the SiO <sub>2</sub>                  | 74 |

| 3.5.                                                         | Hydrogen species released near the gate/SiO <sub>2</sub> interface | 75 |

| 3.6.                                                         | Conclusions                                                        | 78 |

| References                                                   |                                                                    |    |

Table of contents

| 4. Trapping Kinetics of Electron Traps Generated in Silicon Dioxides |                                                                                                    |                                                                  | 104   |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|

| 4.1.                                                                 | Introd                                                                                             | uction                                                           | 104   |

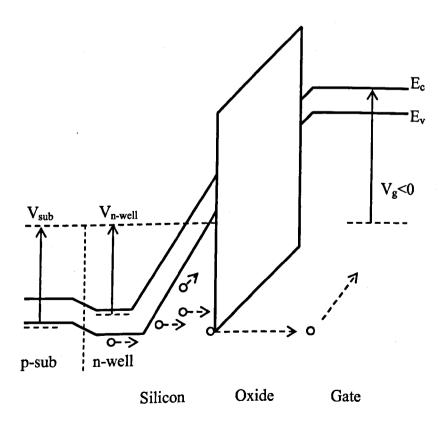

| 4.2.                                                                 | Trapp                                                                                              | ing kinetics of electron traps generated under SHI               | * 106 |

|                                                                      | 4.2.1.                                                                                             | Effects of positive charges                                      | 107   |

|                                                                      |                                                                                                    | 4.2.1.1. Low stress level                                        | 107   |

|                                                                      |                                                                                                    | 4.2.1.2. High stress level                                       | 108   |

|                                                                      |                                                                                                    | 4.2.1.3. Support for the correction method                       | 109   |

|                                                                      | 4.2.2.                                                                                             | Trapping kinetics and trap properties                            | 110   |

|                                                                      |                                                                                                    | 4.2.2.1. The first order model                                   | 110   |

|                                                                      |                                                                                                    | 4.2.2.2. Support for the presence of two capture cross sections  | 111   |

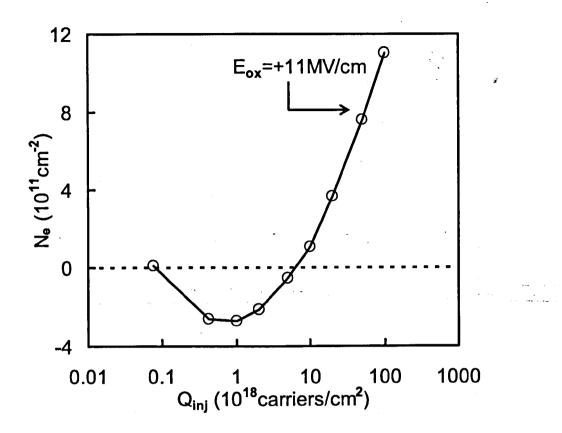

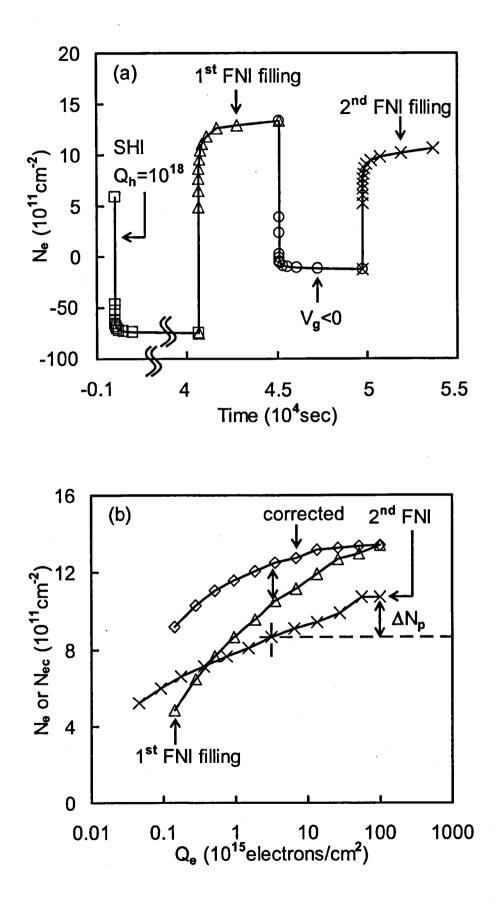

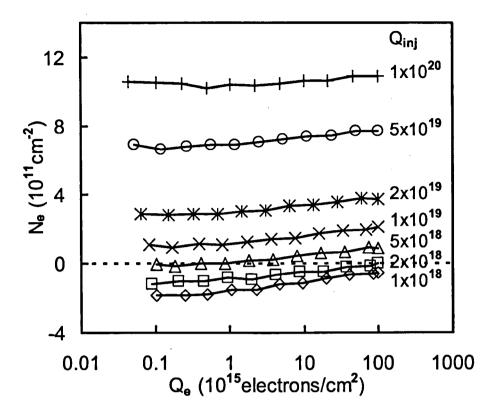

| 4.3.                                                                 | Trapping kinetics of electron traps generated under FNI                                            |                                                                  | 113   |

|                                                                      | 4.3.1.                                                                                             | Difficulties                                                     | 113   |

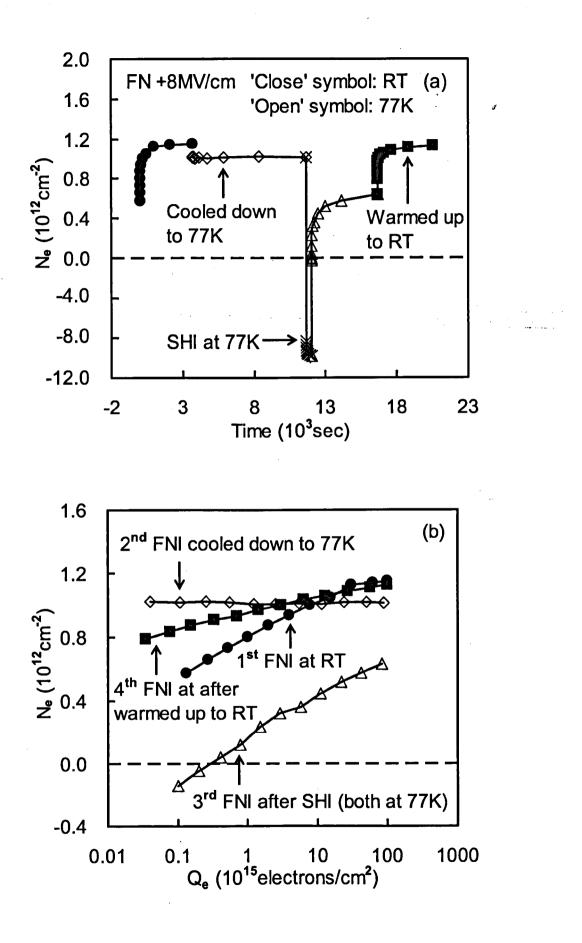

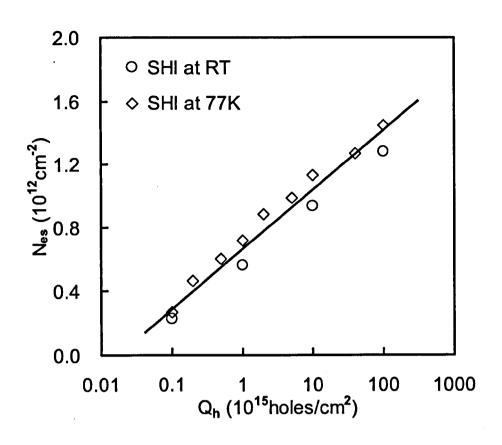

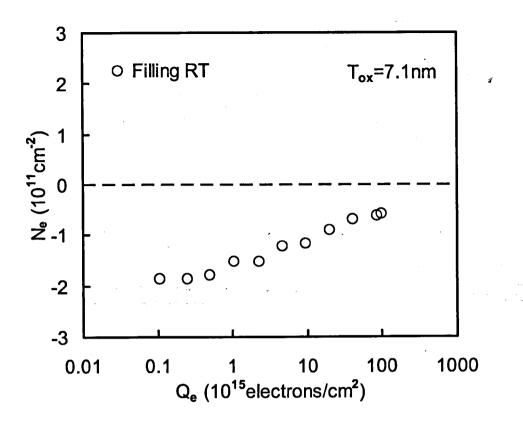

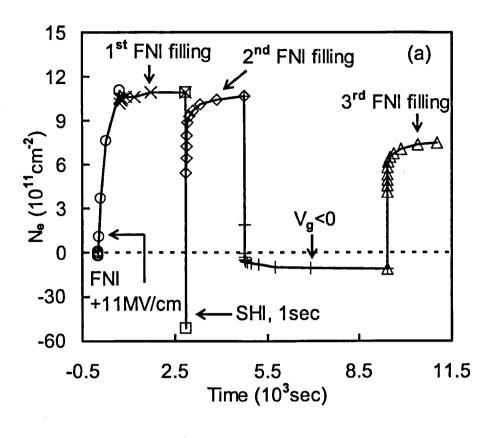

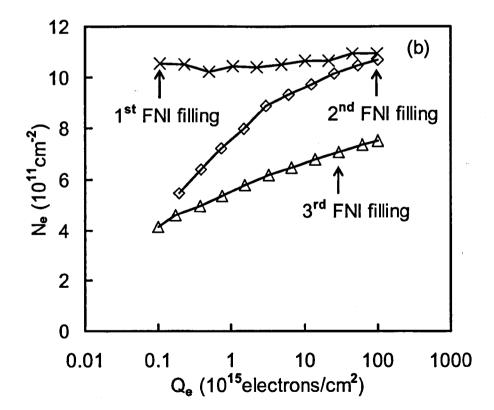

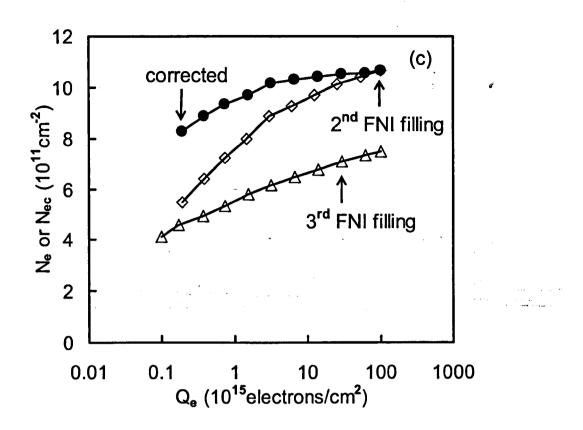

|                                                                      |                                                                                                    | 4.3.1.1. Positive charges formed during FNI                      | 113   |

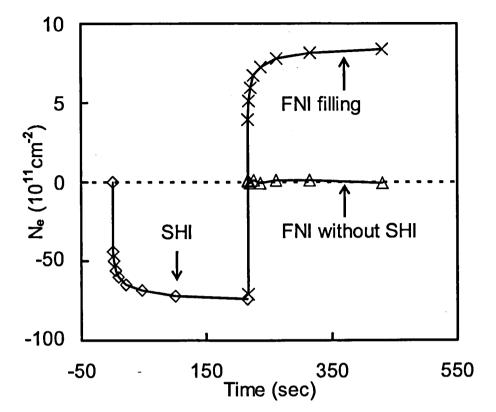

|                                                                      |                                                                                                    | 4.3.1.2. Separation of trap creation from filling                | 115   |

|                                                                      | 4.3.2.                                                                                             | Trapping kinetics                                                | 115   |

| 4.4.                                                                 | <ul> <li>4.3. Trapp</li> <li>4.3.1.</li> <li>4.3.2.</li> <li>4.4. Trapp</li> <li>4.4.1.</li> </ul> | ng kinetics of electron traps generated on thick oxides          | 116   |

|                                                                      | 4.4.1.                                                                                             | Trapping kinetics                                                | 116   |

|                                                                      | 4.4.2.                                                                                             | A comparison of traps generated in oxides of different thickness | ses   |

|                                                                      |                                                                                                    |                                                                  | 117   |

| 4.5.                                                                 | Conclu                                                                                             | ision                                                            | 118   |

| Refe                                                                 | rences                                                                                             |                                                                  | 119   |

|                                                                      |                                                                                                    | ,                                                                |       |

|                                                                      |                                                                                                    |                                                                  |       |

| 5. Neg | Negative Bias Temperature Instability                        |                                                                                                                                                                                                                                                   |     |

|--------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1.   | Introd                                                       | Introduction<br>Investigation of NBTI using traditional measurement method<br>5.2.1. Typical NBTI generation<br>5.2.2. Types of positive charges<br>5.2.3. Effects of experiment parameters on generated positive charges<br>5.2.3.1. Stress time | 149 |

| 5.2.   | . Investigation of NBTI using traditional measurement method |                                                                                                                                                                                                                                                   | 150 |

|        | 5.2.1.                                                       | Typical NBTI generation                                                                                                                                                                                                                           | 151 |

|        | 5.2.2.                                                       | Types of positive charges                                                                                                                                                                                                                         | 151 |

|        | 5.2.3.                                                       | Effects of experiment parameters on generated positive charges                                                                                                                                                                                    | 153 |

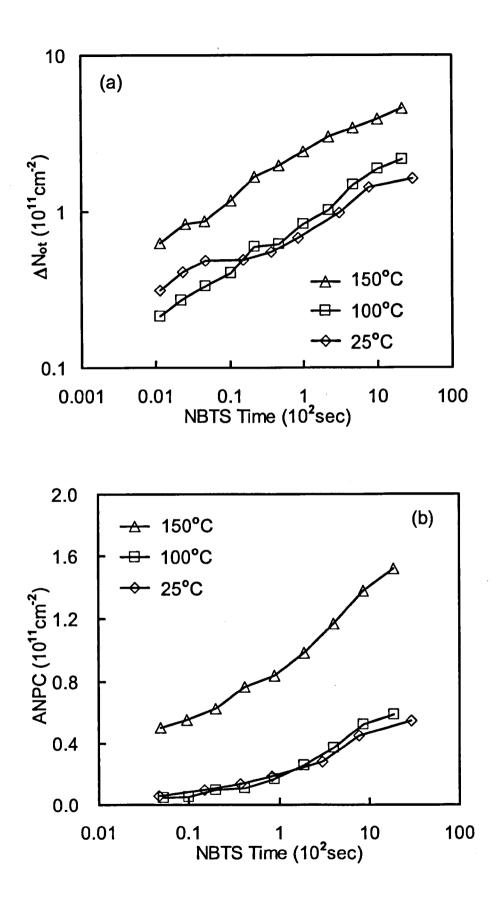

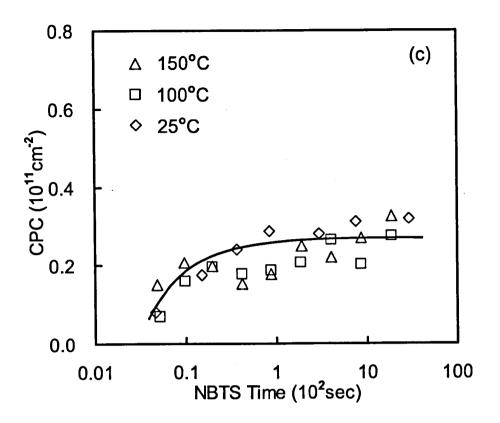

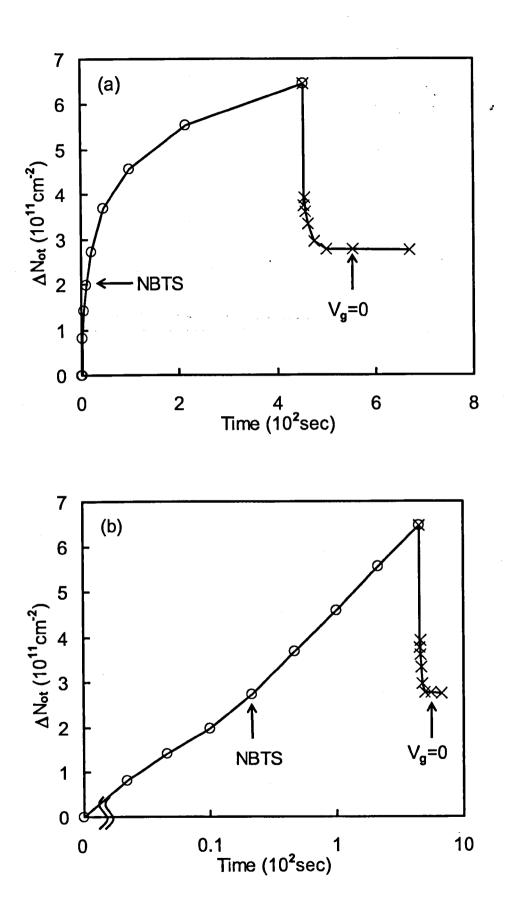

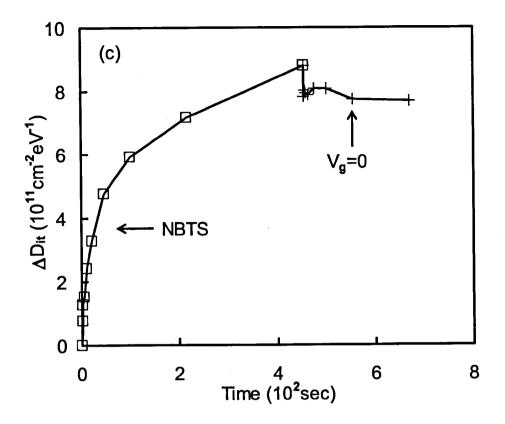

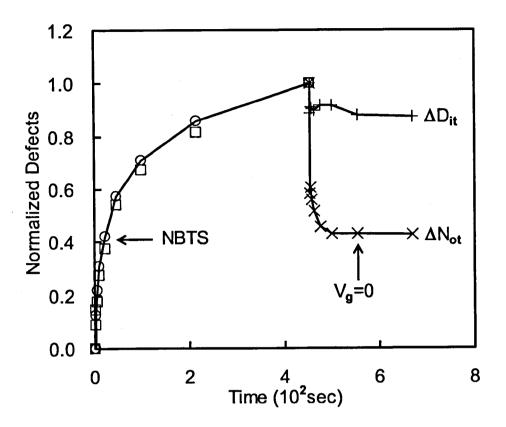

|        |                                                              | 5.2.3.1. Stress time                                                                                                                                                                                                                              | 153 |

|        |                                                              | 5.2.3.2. Thermal stability                                                                                                                                                                                                                        | 154 |

|        |                                                              | 5.2.3.3. Stress temperature                                                                                                                                                                                                                       | 154 |

|        |                                                              |                                                                                                                                                                                                                                                   |     |

<u>- vi -</u>

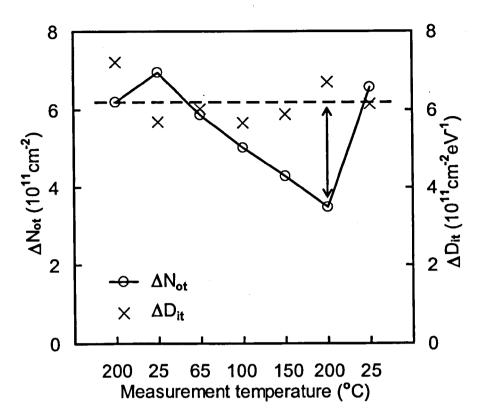

|            | 5.2.4. | Effects of measurement temperature                                  | 155 |

|------------|--------|---------------------------------------------------------------------|-----|

|            |        | 5.2.4.1. On ANPC and CPC                                            | 155 |

|            |        | 5.2.4.2. On effective charge density and interface states           | 155 |

|            | 5.2.5  | Dynamic NBTS                                                        | 158 |

|            | 0.2.0. | 5.2.5.1. Same NBTS time                                             | 158 |

|            |        | 5.2.5.2. Same positive charge generation                            |     |

|            | 526    | Implications to NBTI tests                                          | 159 |

|            |        | Conclusions                                                         | 160 |

| 52         | - · ·  |                                                                     | 161 |

| 5.5.       |        | igation of NBTI using 'On-The-Fly' measurement method               | 162 |

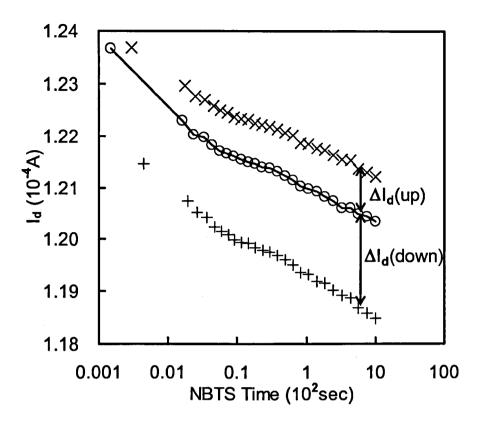

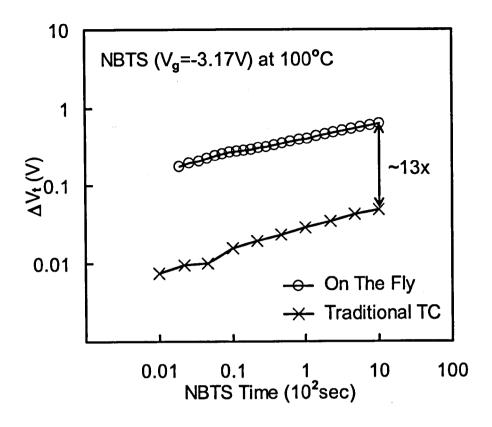

|            | 5.3.1. | Main differences between 'On-The-Fly' and traditional measuren      |     |

|            |        |                                                                     | 162 |

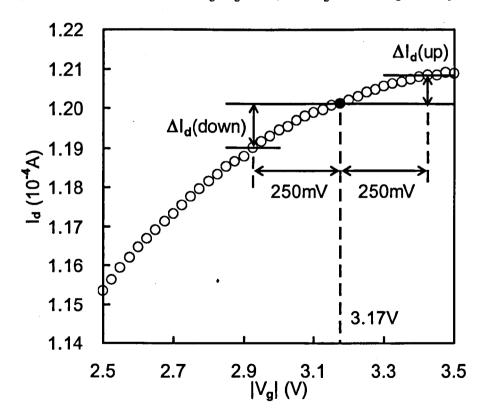

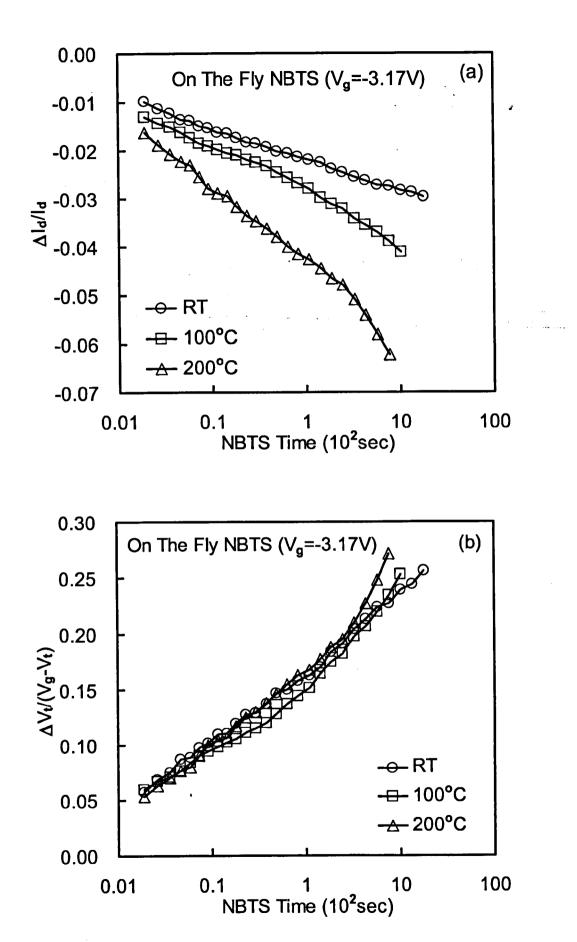

|            | 5.3.2. | Estimation of NBTI induced effective mobility variation             | 163 |

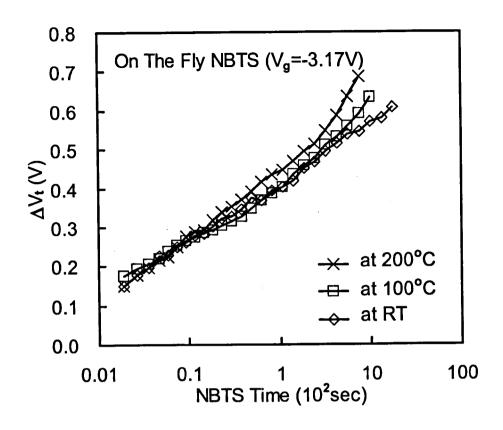

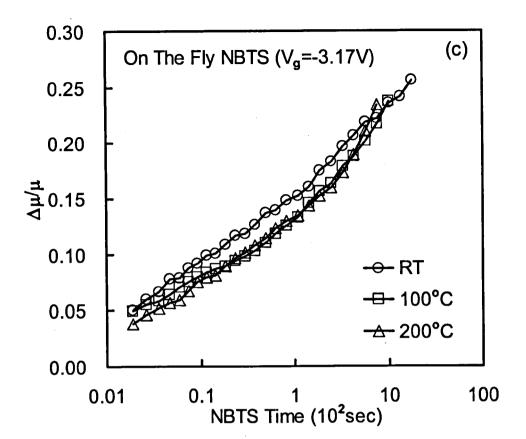

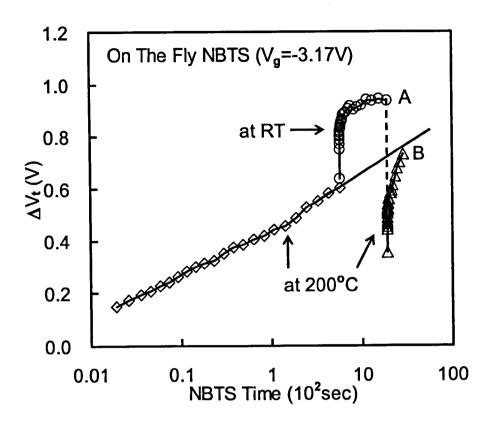

|            | 5.3.3. | Effects of measurement temperature                                  | 168 |

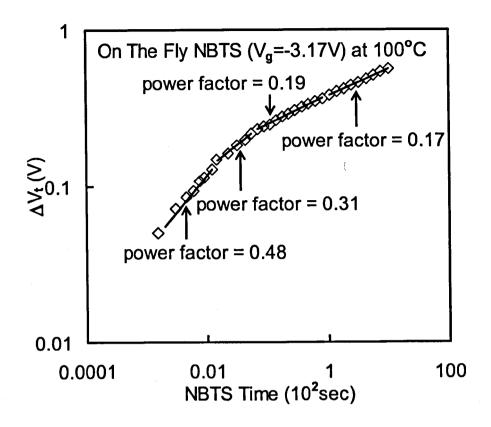

|            | 5.3.4. | Effects of stress time                                              | 171 |

|            | 5.3.5. | Effects of stress voltage                                           | 172 |

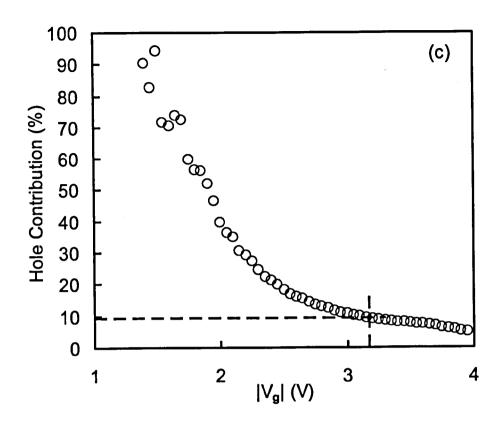

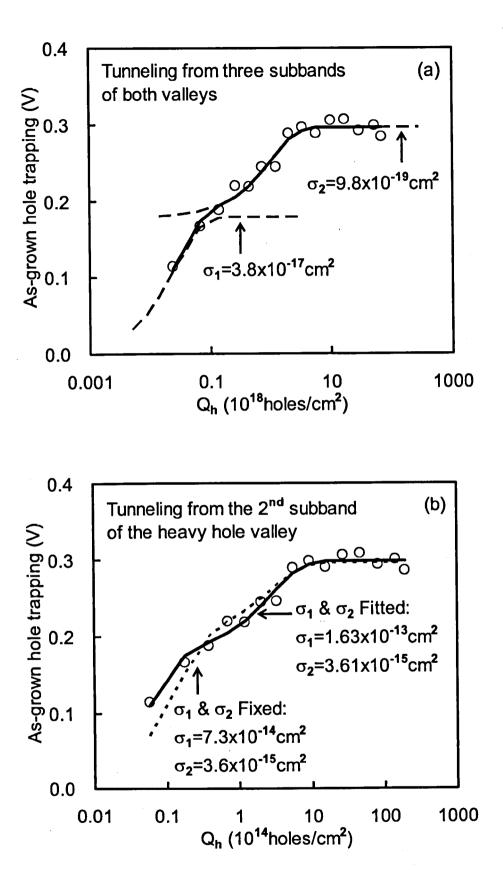

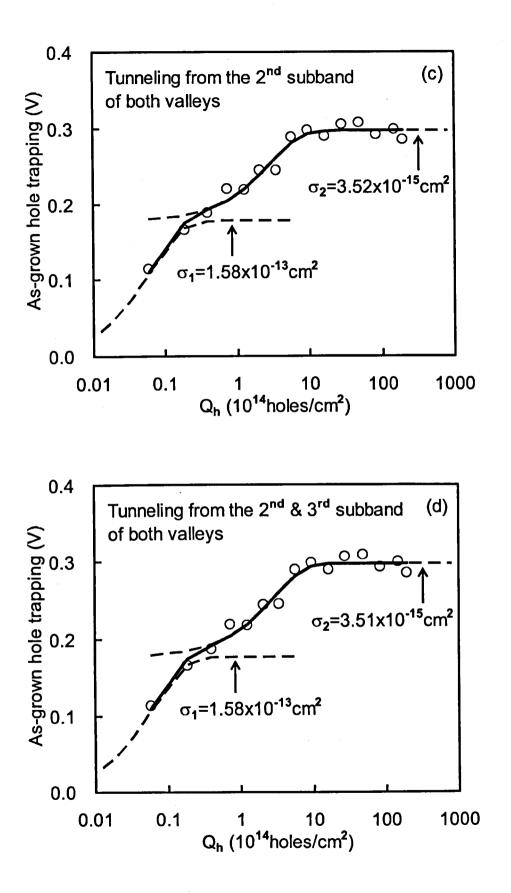

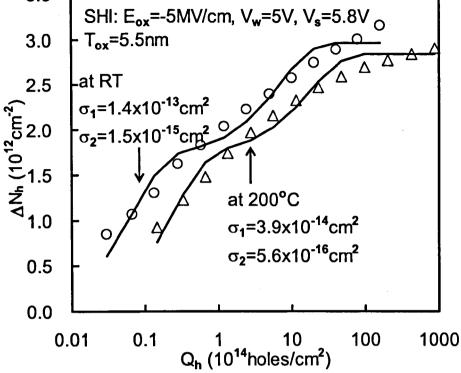

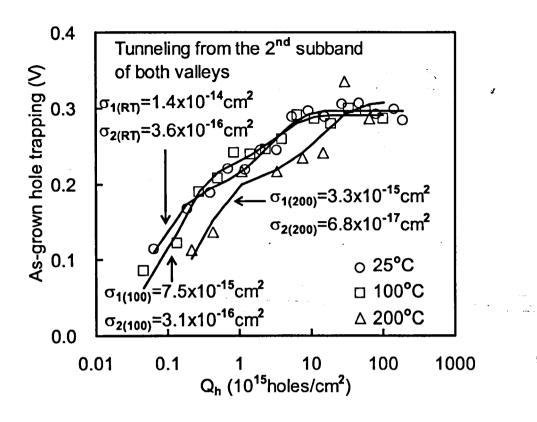

|            | 5.3.6. | As-grown hole traps in thin dielectric                              | 172 |

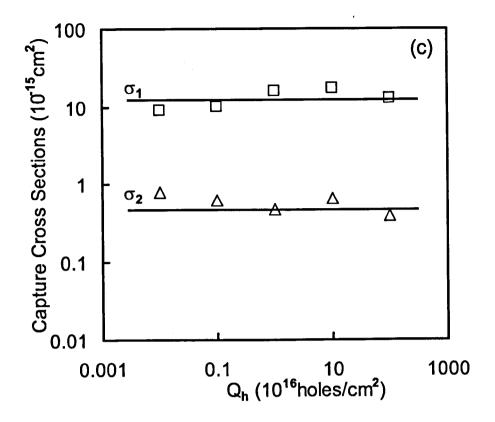

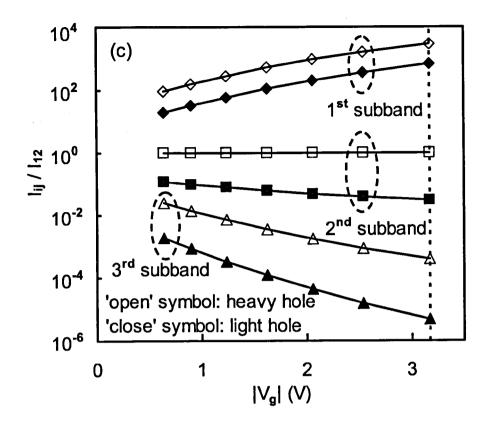

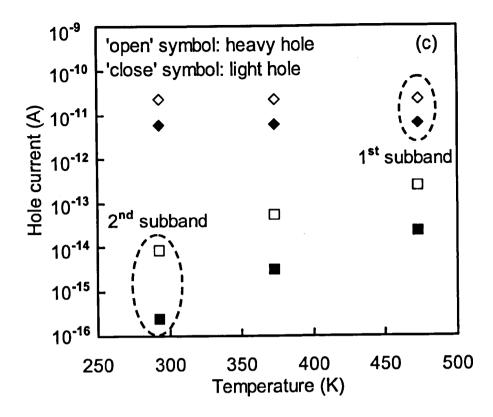

|            |        | 5.3.6.1. Capture cross sections evaluated from the measured hole    |     |

|            |        | current                                                             | 173 |

|            |        | 5.3.6.2. An explanation for the difference in capture cross section | l   |

|            |        | · ·                                                                 | 174 |

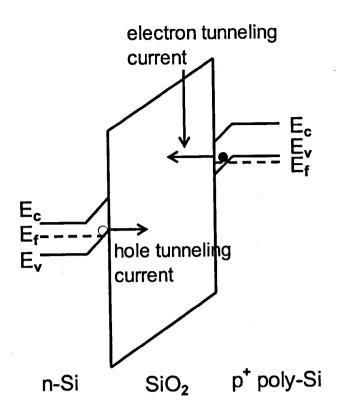

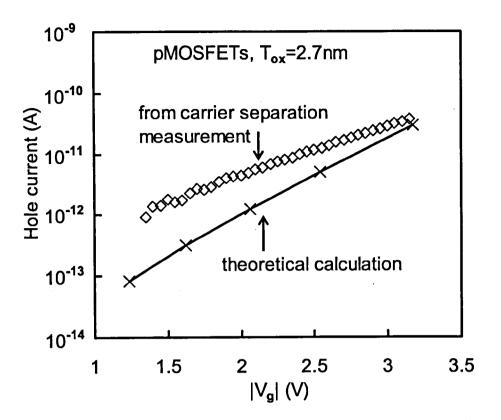

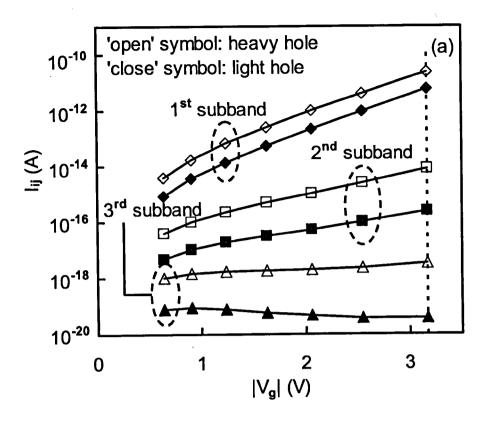

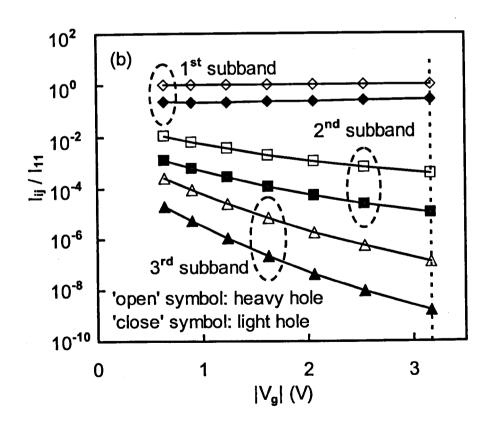

|            | 5.3.7. | Hole current calculation                                            | 174 |

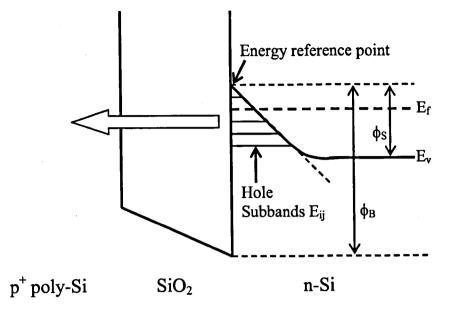

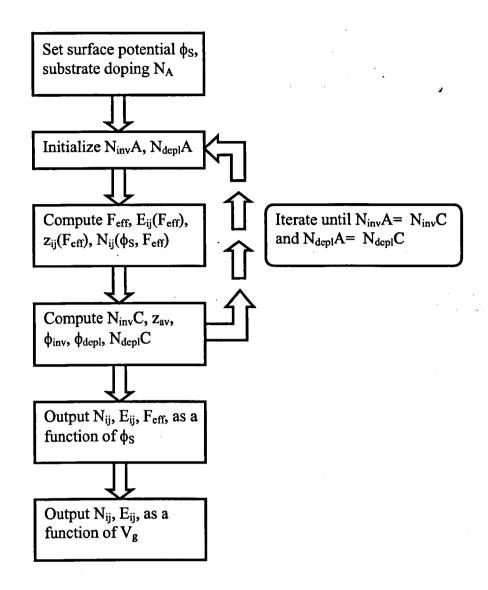

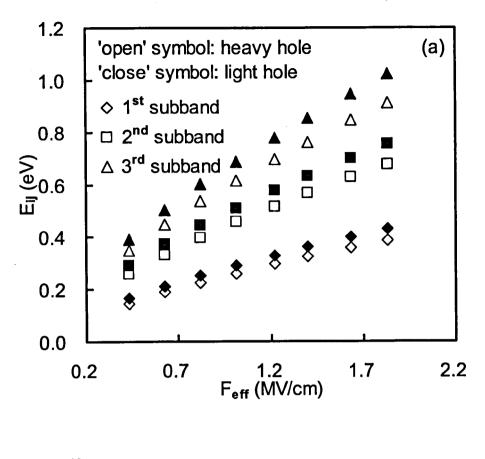

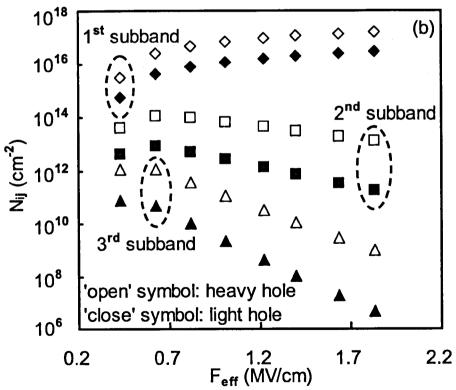

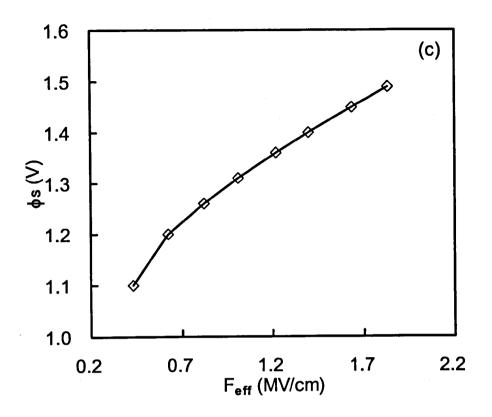

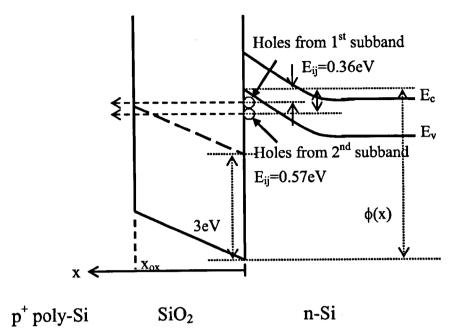

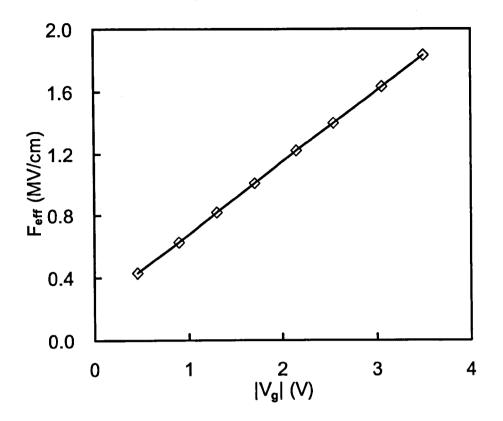

|            |        | 5.3.7.1. Inversion layer charge carrier calculation                 | 175 |

|            |        | 5.3.7.2. Direct tunneling current calculation                       | 175 |

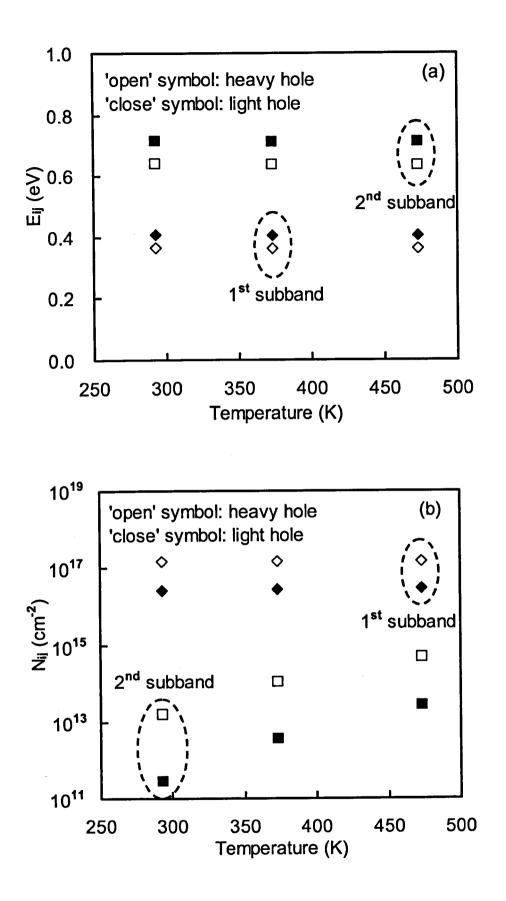

|            | 538    | Estimation of capture cross sections                                |     |

|            | 5.5.0. | 5.3.8.1. Room temperature                                           | 180 |

|            |        | -                                                                   | 180 |

|            | 520    | 5.3.8.2. Effects of temperature                                     | 181 |

| <b>n</b> 4 |        | Conclusions                                                         | 182 |

| Refe       | rences |                                                                     | 183 |

.

| 6. Cor | clusior | ns and Future Work                                             | 260    |

|--------|---------|----------------------------------------------------------------|--------|

| 6.1.   | Conclu  | usions                                                         | 260    |

|        | 6.1.1.  | Conclusions on the role of hydrogen in hole-induced electron   | 1 trap |

|        |         | generation                                                     | 260    |

|        | 6.1.2.  | Conclusions on the trapping kinetics of electron traps generat | ted in |

|        |         | silicon dioxides                                               | 261    |

|        | 6.1.3.  | Conclusions on the negative bias temperature instability       | 262    |

| 6.2.   | Future  | work                                                           | 264    |

٠

# List of publications

...

266

# **1** A Review of the Degradation of Gate Dielectrics in MOSFETs

#### 1.1. Introduction

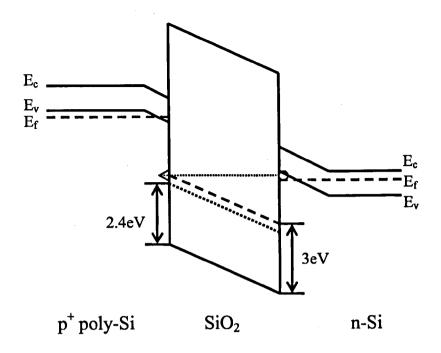

The advance in MOS devices has improved the quality of our life significantly in the last three decades or so. The success of MOS devices heavily relies on the excellent insulating properties of gate silicon dioxides and their near perfect interface with silicon. The gate silicon dioxide is a amorphous insulator with a high bandgap of about 9 eV and high energy barriers against electron and hole injection from silicon [1]. It can be easily grown on Si with low defect density. The excellent scaling and process integration of gate silicon dioxides are mainly due to the stability and insensitivity of the insulator to process steps following the oxidation.

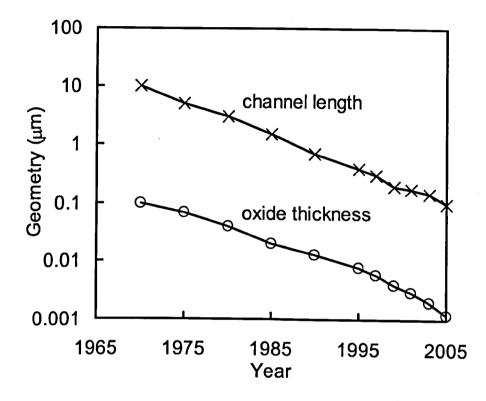

In a continuous drive to increase integrated circuit performance through shrinkage of the circuit elements, the dimensions of MOSFETs have been scaled down following a trend known as Moores's law [2-4]. Moores's Law describes the exponential growth of chip complexity due to decreasing minimum feature size, accompanied by concurrent improvements in circuit speed, memory capacity, and cost per bit. To maintain the gate control and reduce the short channel effects, the gate  $SiO_2$  has been decreased in thickness from hundred of nanometers (nm) 40 years ago to less than 2 nm today, as shown in Figure 1.

Gate silicon dioxides are not perfect and suffer from reliability problems. A very narrow region of transition occurs from the mono-crystalline silicon substrate to the amorphous silicon dioxide layer, which contains a high density of non-saturated bonds, strained bonds and broken bonds [5,6]. These imperfections or defects introduce localized energy levels in the silicon forbidden gap at the SiO<sub>2</sub>/Si interface. Defects are also present in the oxide bulks. The density of these defects is a function

of processing conditions, such as the growth temperature/pressure and the chemical interaction of these so-called "intrinsic" defects with chemical impurities, such as H and Cl, introduced during IC processing [5]. As the oxide scaling down, its intrinsic reliability limits are approached and might become a major showstopper for future technology.

Figure 1. Trend in MOSFET scaling. The channel length and the oxide thickness have been reduced by two orders of magnitude since early seventies.

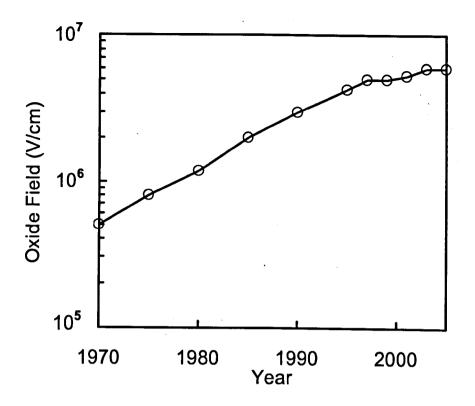

During device operation, the thin gate oxide is subjected to a high electrical field. As the CMOS technology progresses, Figure 2 shows that this field has gradually increased. Even the lowering of operation voltage for recent CMOS generations has not stopped this trend. Values as high as 6 MV/cm are reached in the current generation of CMOS technology. At this field, carriers can be easily injected into the oxide and lead to a gradual degradation of the oxide. Generated defects can trap some of the injected carriers and change the electrical behavior of the MOSFET. Eventually a sudden breakdown occurs as the generation sums up to a critical amount.

Figure 2. Oxide electric field as a function of time for CMOS circuits. Oxide field have increased from below 1 MV/cm in the early seventies to 6 MV/cm today.

According to their spatial location, generated traps are classified as either bulk oxide traps or interface traps. Interface traps are located at or very near the  $Si/SiO_2$  interface and are able to exchange charges with the silicon bands on time scales ranging from picoseconds to hours [6]. They are distributed in energy throughout the silicon band gap. Their charge states are determined by the interface Fermi-level. Bulk oxide traps are located farther away from the  $Si/SiO_2$  interface and are much more difficult to exchange charges directly with the silicon. Bulk defects include both electron traps and hole traps, which can be either neutral or charged [5].

Generated defects can affect device operation in three ways. First, they can capture electrons or holes and build up space charges, which shift parameters, such as threshold voltage and transconductance [7,8]. Second, electron traps can assist electron tunneling through the dielectric [9,10]. This stress induced leakage current (SILC) can considerably reduce the non-volatile memory retention time. Third, the build-up of electron traps triggers the dielectric breakdown [11,12]. This time-dependent dielectric breakdown (TDDB) and SILC and their relation to the

preceding trap generation have been numerously studied over the past three decades. But even today, a complete understanding has not yet been achieved. The knowledge of the trap generation mechanism and trapping-detrapping characteristics is the key issue for understanding TDDB and SILC.

In this chapter, the important concepts related to the degradation of gate oxides will be reviewed. These include the sources of instabilities, charge carrier injection, interface states generation, electron trap generation, trapping/detrapping, and positive charge generation.

### 1.2. Sources of instabilities and charge carrier injection

#### 1.2.1. Irradiation

The generation of defects in the oxide and at the interface of MOSFETs under irradiation has been widely reported [14-21]. The radiation source can be vacuum ultraviolet light, X-ray, electron beam or any other high energy sources. The common feature of these sources is that their photon energy is large than 9 eV, the band gap of silicon dioxides [21]. The irradiation induced degradation in MOSFETs begins when ionising radiation is absorbed in the oxide, creating electron-hole pairs. Depending on the kind of irradiation and the polarity of the applied field, some fraction of these charged pairs will undergo recombination process. Electrons that have higher mobility can be swept out of the oxide and the holes of lower mobility will have a high probability of being trapped in the oxide. Degraded characteristics include changes in MOSFET threshold voltage, reduced inversion layer mobility, increased minority-carrier generation and increased low-frequency noise [20].

#### 1.2.2. Plasma charging

Plasma-assisted processes are widely used in the manufacturing of VLSI devices. The degradation of gate oxides in MOS devices due to plasma processing was reported [22-27]. During plasma processing, ions and electrons are collected by the metal or polysilicon electrodes connected to the gate. Due to this charge collection, a voltage appears on the electrode and causes tunnelling current to flow through the gate oxide. This results in charge build-up, the generation of new oxide traps, and the generation of interface states. H. C. Shin and C. M. Hu [22] suggested that the plasma charging could be reduced by reducing the ion density or the electron temperature. Maintaining a very uniform plasma charging current during the etching, the proper use of protection diodes and the antenna design rule will reduce the plasma damage to an acceptable level.

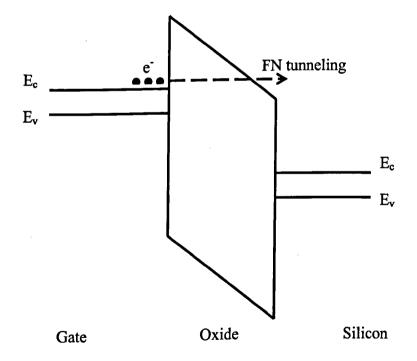

## 1.2.3. Fowler-Nordheim injection and substrate hot carrier injection

These are uniform injection techniques, and will be described in details in the section 2.5 of Chapter 2.

#### 1.2.4. Channel hot carrier injection

When MOSFETs operating in saturation, the electric field peaks in the vicinity of the substrate-drain junction due to the pinch-off condition. If the lateral electric field is sufficiently high, strong carrier heating can result in electrons with an energy high enough to create electron-hole pairs by impact ionisation [28-31]. Those hot carriers having energy over 3.2 eV for electrons and 4.8 eV for holes can be injected into the oxide [29]. Hot carrier injection into the SiO<sub>2</sub> depends strongly on the biasing conditions of the device and on the mode of operation (subthreshold, linear or saturation). The device degradation is most severe if it is biased to maximise the substrate current, which occurs at  $V_g \approx V_d/2$  [28]. For  $V_g > V_d/2$ , electron injection is dominant. However, when  $V_g$  is close to the threshold voltage ( $V_g \approx V_i$ ), hole injection dominates [30]. In addition to the degradation of transistor performance, electron trapping and related damages also cause significant reliability problems for EPROM devices, such as the "program window closure" effect [31].

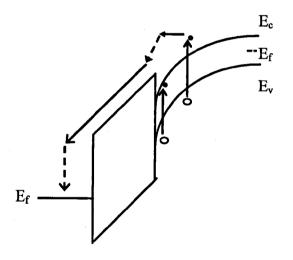

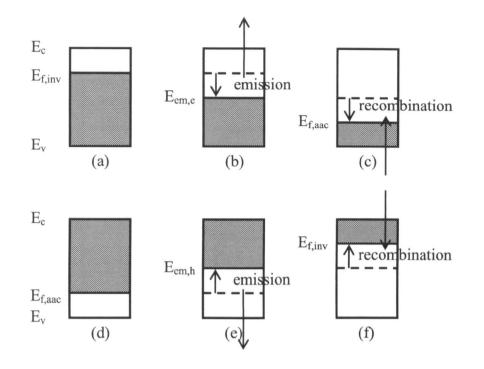

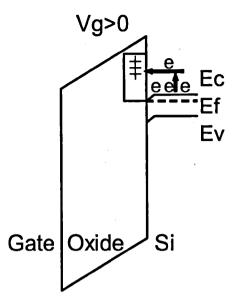

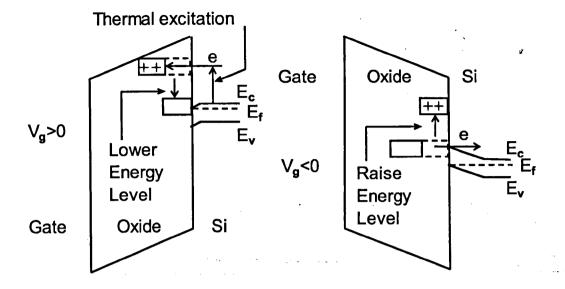

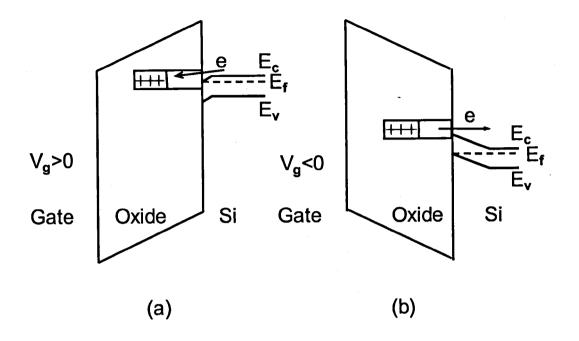

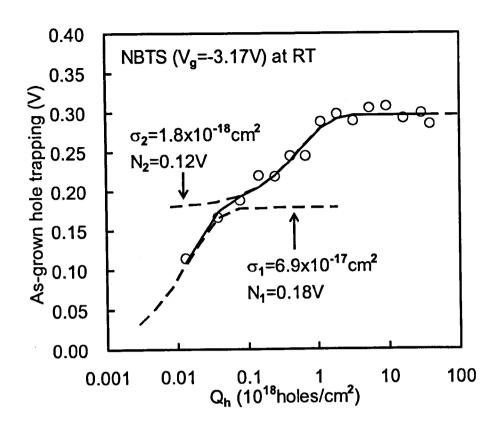

#### 1.2.5. Avalanche injection

In avalanche injection [21,32-34], the MOS capacitor is operated in the deep depletion condition, as shown by the energy band diagram in Figure 3. Charge carriers are accelerated rapidly by the applied electric fields. When the gate voltage is high enough to produce avalanche breakdown in the silicon, carriers generated in the depletion layer will be accelerated to sufficient energy for impact ionisation to occur. This creates plasma of energetic hole-electron pairs near the interface. Some of the electrons or holes created will have enough energy to surmount the interfacial energy barrier and enter the SiO<sub>2</sub>. The energy barrier for electron injection is 3.2 eV, whereas it is 4.8 eV for hole injection. As a result, electrons have a higher injection probability. Avalanche is a uniform injection technique and is used in MOS capacitors.

Figure 3. Energy band diagram shows a MOS capacitor operated in the deep depletion condition during avalanche injection.

#### **1.3.** Electron traps in the oxide

#### 1.3.1. Electron trap generation

Electron trapping in silicon dioxides has been investigated for the last three decades or so. Early work [35-38] was focused on impurity-related traps. There are three classes of impurities: sodium, implants and hydrogen/water. Sodium introduces both deep and shallow level of electron traps in the oxide [36,39]. For modern semiconductor industry, the use of ultra-clean technology reduces the sodium contamination to a negligible level. The most commonly used implants are Arsenic (As), Phosphorus (P) and Boron (B). Boron does not introduce traps into the oxide, but both As and P do [36,37]. The trap density was reported to be 0.7-1 times of the ion density in the oxide [37]. With careful control of the implantation, these traps are generally not important for modern CMOS processes.

It is most difficult to eliminate hydrogen/water from the device and it is generally believed that it still plays a crucial role in modern device instability. Nicollian et al. [35] showed that diffusion of H<sub>2</sub>O into the oxide created a trap with a capture cross section ( $\sigma$ ) in the order of 10<sup>-17</sup> cm<sup>2</sup>. When Aluminum is used as the gate, hydrogen also introduces a trap of  $\sigma = 10^{-18}$  cm<sup>2</sup> [38]. For a poly-si-gated device used in industry, however, these relatively large traps were absent. The electron trap in the gate oxide of a modern MOSFET has a capture cross-section in the order of 10<sup>-19</sup> cm<sup>2</sup> or less [40,41].

Since all the 'well-known' electron traps mentioned above are not important in a modern device, previous work on them is of limited use. For a poly-si-gated device, most of electron traps are generated under high field stress. It is these generated traps that cause leakage and trigger breakdown [11-13]. Despite the past efforts, our understanding of the electron traps is still poor. For example, the microstructure of generated electron traps has not been unambiguously identified and agreement on damaging species has not been reached [42-44].

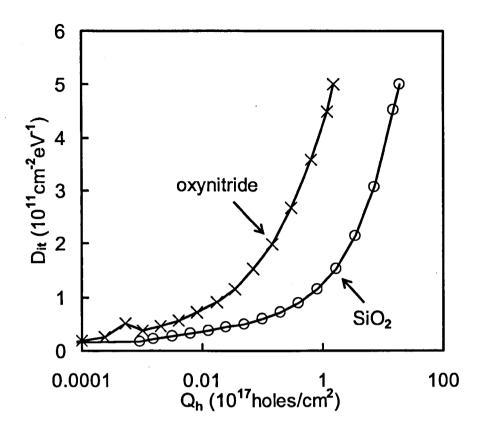

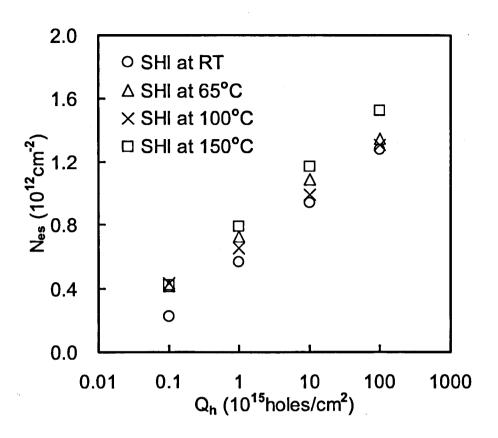

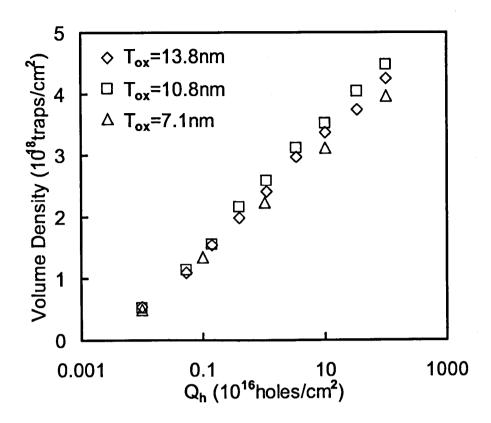

The researchers at IBM [40] believe that the damaging species are hydrogen-related for thin oxides, while the researchers at Lucent Technology [44] believe that holes are the species. For the hydrogen theory, the problem is that there is no convincing direct evidence showing that hydrogen can create new traps in the oxide bulk, although it is well accepted that hydrogen generates interface states at room temperature [45]. For the hole theory, it was proposed that the recombination of electrons and holes led to the generation [46]. It was also shown that the oxide broke down at a constant hole fluence,  $Q_h$ , under Fowler-Nordheim injection (FNI) at room temperature [11]. However, this is not strong enough to suggest that there is a causal relation between these two.  $Q_h$  is not a constant anymore under substrate hot hole injection [47] or at different temperatures [48]. The impact of hydrogen on holeinduced electron trap generation will be investigated in Chapter 3.

#### 1.3.2. Models proposed on electron trap generation

Several models have been proposed for the electron trap generation. In summary, there are at least four trap generation models: the "hydrogen release model", the "anode hole injection model", the "electric field energy model", and the "electron-hole recombination model".

#### 1.3.2.1. Hydrogen release model

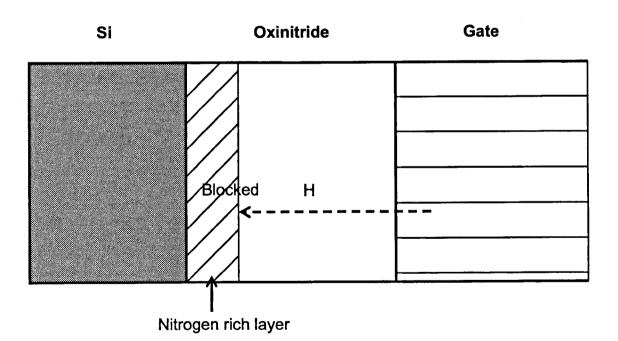

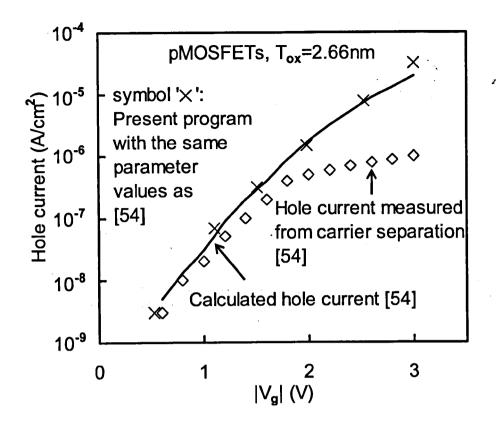

The hydrogen release model has been suggested since 1980's [40,49-51], in which the electrons tunnel through the oxide potential barrier and reach the anode with sufficient energy to release hydrogen from the anode/oxide interface. Hydrogen is always present in sufficient amounts because of interface annealing applied to reduce the initial interface trap density. The released hydrogen diffuses through the oxide and can generate electron traps. This phenomenon is thermally activated above 200K. This model is supported by the observation that, when an oxide (without poly-Si gate) on a silicon substrate is exposed to a remote hydrogen plasma, the interface trap creation evolves similarly to the interface trap creation induced by a hot electron stress [24,52]. It is also supported by the observation of hydrogen buildup in the dielectric after stress [53], and by the theoretical calculations and experimental observation of the interaction of hydrogen with the oxide lattice [54-56].

#### 1.3.2.2. Anode hole injection model

In the anode hole injection model [57], it is believed that holes injected from the anode dominate the electron trap generation. However, the precise role of holes in the trap generation process and the details of the microscopic mechanism of the trap generation are still uncertain. Difficulties in studying this process arise from the inability of many techniques to separately control the hole and the electron injection. When the gate oxide of a nMOSFET is stressed with a positive gate voltage, with source and drain grounded, electrons tunneling through the oxide are injected from the transistor channel and provided from the source and drain. In this configuration, a positive current can be measured at the substrate (charge separation technique) [58,59]. The substrate current density has a similar oxide field dependence as the FN-current density. The ratio between gate and substrate current depends on the oxide field.

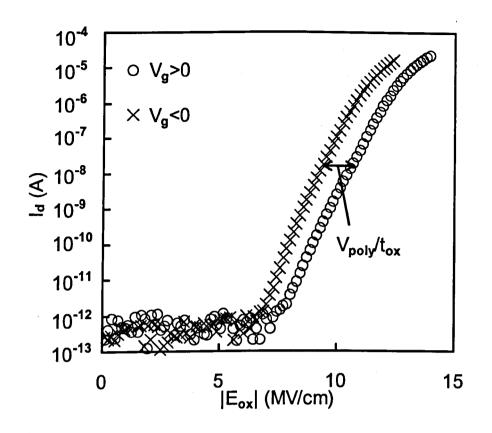

A well-known and widely accepted explanation for the physical origin of this substrate current is given in refs. [57,58,60]. When the injected electrons enter the anode (the poly-Si gate), they lose their energy by creating high energetic holes and the holes can then be injected back into the oxide. The hole flow reaches the cathode and is measured as a positive substrate current. Another possible explanation for the substrate current is the creation of holes in the cathode by photons generated in the anode [60]. In anode hole injection model, the probability for a tunneling electron to generate an anode hole is found to be almost constant during the whole stress under a constant-voltage-stress. This probability slightly increases under a constant-current-stress, where the increase is very small for thin oxides. At room temperature, it has been observed [11,58] that the hole fluence reaches a critical value at breakdown, which remains constant in a wide range of electrical field from 8 MV/cm to 14 MV/cm.

For lower temperature, the hole fluency at breakdown decreases with increasing oxide field [61]. For temperatures above 300K, it increases for higher oxide field [62]. These temperature effects indicate that the hole fluency is possibly not controlling the breakdown. In ref. [60], it is demonstrated that with a gate bias below 7.8 V, the dominant source of the hole current is photo-excitation of valence band electrons in the cathode by light generation in the anode. It is also shown [63] that the injected electrons relax their energy by light emission. Recent work by IMEC [64] shows that most of the holes in substrate current do not traverse through the gate, which means that the substrate current could significantly overestimate the anode hole injection.

#### 1.3.2.3. Electric field model

Some authors have suggested that the electric field itself induces sufficient energy directly into the oxide to cause electron trap creation (electric field energy model) [65-69]. However, experimental results under both tunneling stress and hot electron injection have confirmed that the breakdown of silicon dioxide is related to the electron fluency through the dielectric and not solely due to the interaction of the electric field with the dielectric lattice [70]. Recent studies have also shown a direct correlation between the energy dependence of damage produced using tunneling electron injection and that produced using hot electron injection [71-73]. This means that electron energy could be the dominating factor, rather than the oxide field. These results suggest that the electric field model does not correctly describe the breakdown of ultra-thin oxides.

#### 1.3.2.4. Electron-hole recombination model

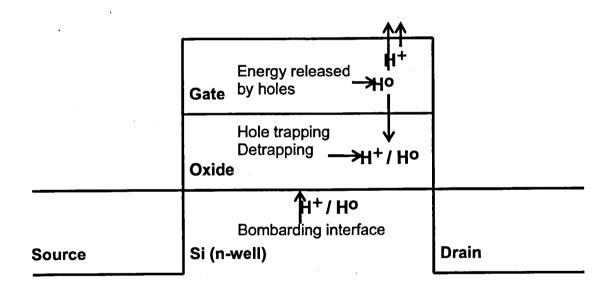

It is well known that some injected holes can be trapped and then neutralized by recombining with electrons. The energy released by electron-hole recombination in the oxide could generate electron traps [74,75]. The holes are produced by either anode hole injection or by impact ionization in the oxide layer near the anode [76]. These secondary hole generation mechanism can be observed down to hot electron

energies of 5 eV and 9 eV respectively [76]. Once the holes are generated and/or introduced into the oxide layer, they are mobile and can move throughout the oxide bulk to the interfaces where some are trapped in energetically "deep" sites believed to be caused by oxygen vacancies [77]. Conduction band electrons can continuously recombine with these holes and generate electron traps [21,46,49,58]. This defect generation mechanism is process dependent and appears to be related to the hydrogen content of the oxide [21]. It reaches a steady-state value dictated by the hole generation probability and the recombination kinetics with free electrons. It has been suggested that defect generation by the recombination of an electron with a trapped hole is observed only when electrons are injected into the conduction band of the oxide [21].

#### **1.3.3.** Electron trapping kinetics

Generation of acceptor-like electron traps in gate oxides is an important source for device instability. It has been found that electrons injected into the gate oxide have a certain, small probability of being captured in electron traps present in the oxide bulk [40].

Our understanding of the generated trap is still limited, partially because of the lack of a well accepted trapping model. Developing a trapping model is highly desirable for understanding the generated electron traps, since it allows us to determine their effective physical size, namely capture cross section. It will also give us information on how many types of electron traps are generated. Information like this will be valuable when the origin of generated traps is explored and models for oxide breakdown and SILC are developed [11,78].

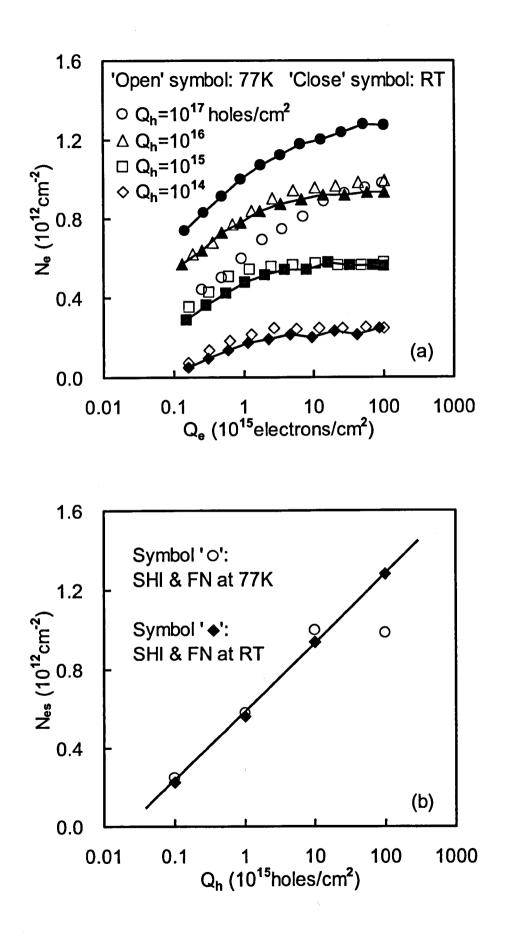

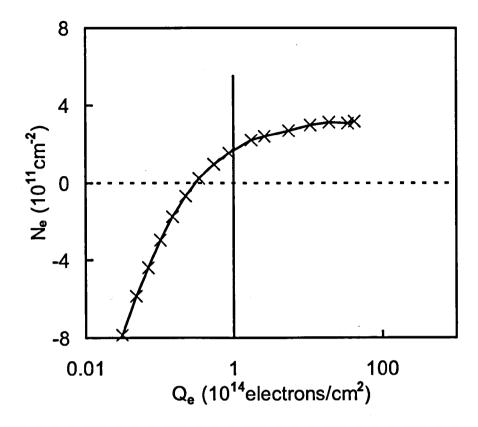

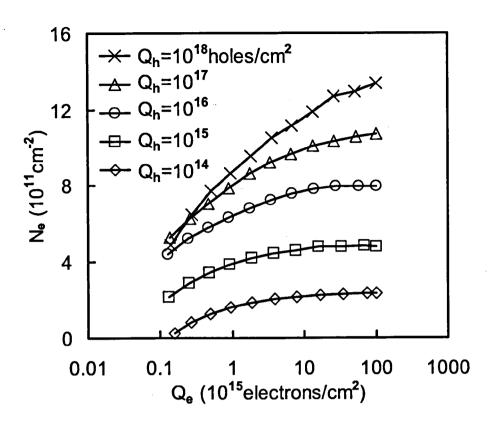

The most well known trapping model is the first order model [35,37,79] and it has been applied successfully for as-grown electron traps [35,37]. Although it was proposed that this model could also be applied for generated traps [38], this verdict has not been adopted generally. Only limited works [80] were carried out on electron trapping kinetics for poly-si gated devices. Non-uniform electron injection was used and consequently, uncertainty exists in the density of injected electrons [79,81]. In the first order model, it is assumed that the traps may have multiple-capture cross sections. The areal density of the trapped electrons, N, is described by,

$$N = \sum_{i=1}^{M} N_i \cdot \left[ 1 - \exp\left(\frac{-\sigma_i \cdot Jt}{q}\right) \right]$$

(1)

where M is the number of measurable electron capture cross sections,  $N_i$  is the saturation density of traps with a capture cross section of  $\sigma_i$ .

The minimum numbers of distinct cross sections and the corresponding trap densities can be determined by fitting with experimental data. Using this approach, the more cross sections are used, the better fitting will be. Oxide defects with trapping cross sections of approximately 10 ~ 100 atomic dimensions ( $\sigma \approx 10^{-13} \sim 10^{-14}$  cm<sup>2</sup> for charged traps) and one atomic dimension ( $\sigma \approx 10^{-16} \sim 10^{-17}$  cm<sup>2</sup> for neutral traps) have been identified by using this method, which is the reasonable dimensions for coulombic and neutral defect sites respectively. Introduction of more different electron trap cross sections can give better fitting with the test results. However, this may be an artefact. For example, the generation of new traps at very large electron injection level may be responsible for very small capture cross sections. Therefore, it is important to find the supporting evidence for the presence of different cross sections, so that they are physically meaningful.

In Chapter 4, the difficulties of studying the electron trapping kinetics for generated traps will be overcome by a careful selection of experimental conditions and testing samples. A new method is developed to compensate the offsetting effects of positive charge formation on electron trapping kinetics. As a result, the number of capture cross sections can be unambiguously determined. The dependence of trap density for a given capture cross section on stress level is examined.

#### **1.4.** Positive charges in the oxide

#### 1.4.1. Positive charge formation

As the downscaling of gate oxides continues, trap density in the oxide bulk will reduce, but positive charges formed near to the  $SiO_2/Si$  interface become relatively important. For gate oxides used in industry, hole trapping is the most important process for positive charge formation.

Positive charges can be formed in silicon dioxides in a number of ways. In the early generation of metal-oxide-semiconductor devices, both mobile and immobile sodium ions were found in the oxide [82,83], which caused device instabilities. In a modern MOS device, the sodium ion is eliminated by using the ultra-clean process. However, fixed positive charges are still formed near the oxide/silicon interface during the fabrication. It was suggested that these fixed charges were partially ionized silicon atoms [84], although this was challenged recently [85,86]. Recent work [85-87] shows that positive charges can be formed in the oxide by interacting with H<sub>2</sub> at a temperature over  $500^{\circ}$ C. The formed charges are fixed when the device has no gate or has a metal gate [86]. However, they become mobile when the oxide is capped by a layer of polycrystalline silicon [87]. It has been proposed that these mobile protons can be used for non-volatile memories [87].

After fabrication, positive charges can also be introduced into the oxide during the device operation. In an irradiative environment, it is well-known that positive charge formation is one of the main sources for device instabilities [88]. They are also formed under a high electrical field (e.g., > 7 MV/cm [38,50]), which is used for programming non-volatile memories [89,90]. Even during the operation of a MOS field-effect transistor (MOSFET) at the relatively low oxide field, formation of positive charges was observed [90].

In addition, two different types of positive charges have been reported [91,92]. One of them is the trapped hole, which, once neutralized, can not be recharged without further hole injection. The other is referred to by various names, including anomalous positive charges [93,94], slow states [95], border traps [96], and switching oxide traps [97]. The main difference from the trapped hole is that it can be positively charged again under a negative gate bias without switching on the hole injection [91,92]. Formation of anomalous positive charges is generally considered to be a complicated issue and our understanding of it is still poor. For example, it is not known if there is more than one type of anomalous positive charges. There is also a lack of evidences for clarifying the relation between anomalous positive charges and hole traps.

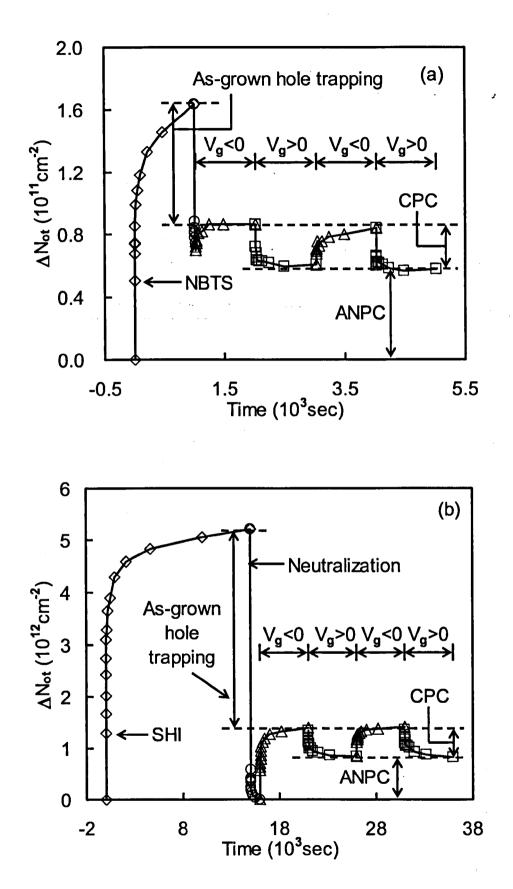

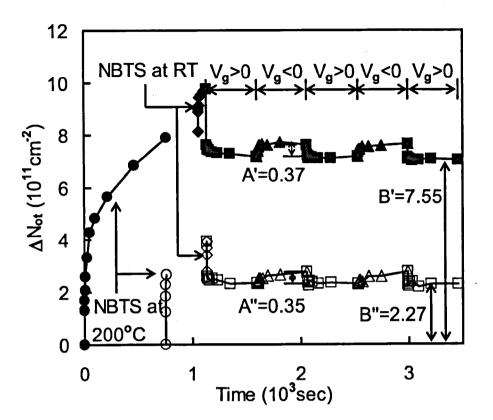

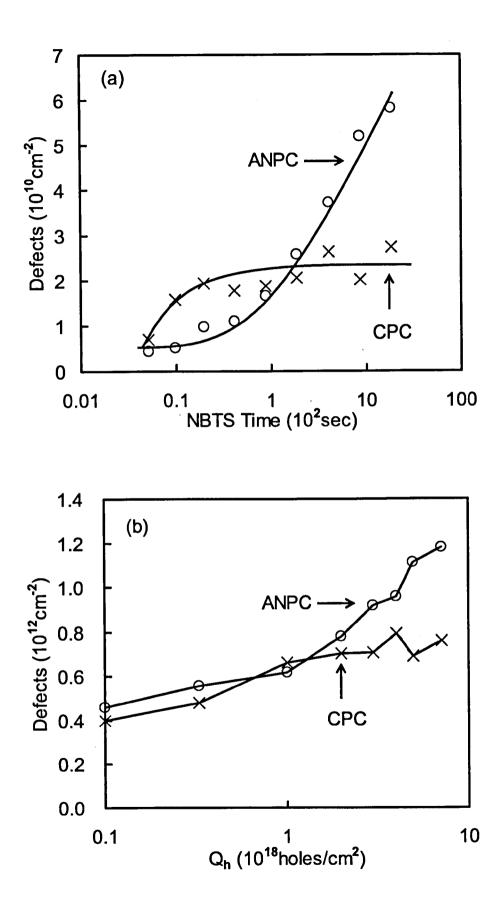

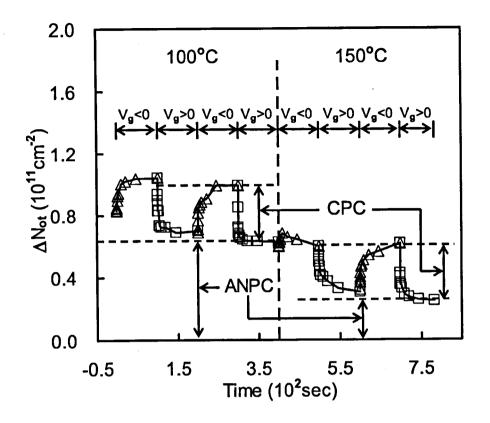

Previous works [98-101] at this university have shown that that generated hole traps behave quite differently from as-grown ones, although they have similar capture cross section in the order of  $10^{-13} \sim 10^{-14}$  cm<sup>2</sup> [31,98,102,103]. Three different types of hole traps are identified [101,104]. One of them is as-grown, the other two are created. Generated hole traps consist of two components: anti-neutralization positive charges (ANPC) and cyclic positive charges (CPC). After neutralization, both of them can be recharged positively under a negative gate bias,  $V_g < 0$  (-5 MV/cm), without hole injection. When the gate polarity is switched to positive, the CPC can be neutralized at a speed similar to its charging. The neutralization of ANPC, however, is much more difficult. Additionally, the discharging of CPC is insensitive to temperature, while the discharging of ANPC is thermally accelerated. It was proposed that the most important process for hole-trap generation is the direct interaction of injected holes with the oxide [104].

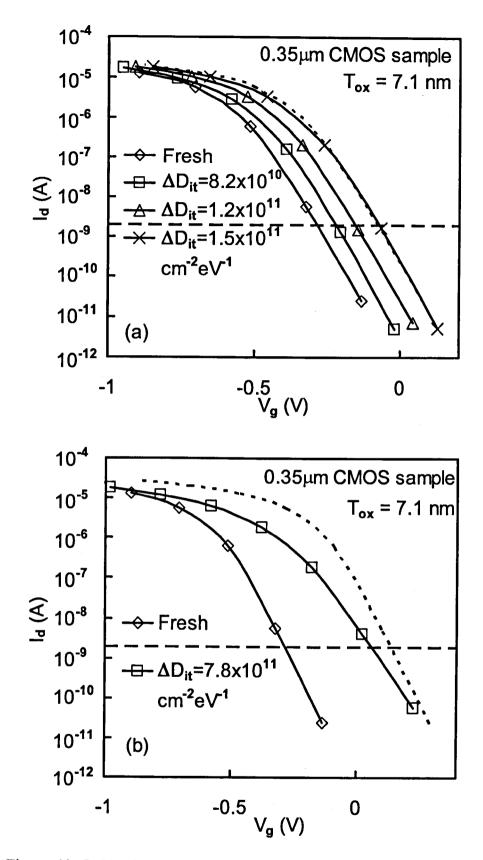

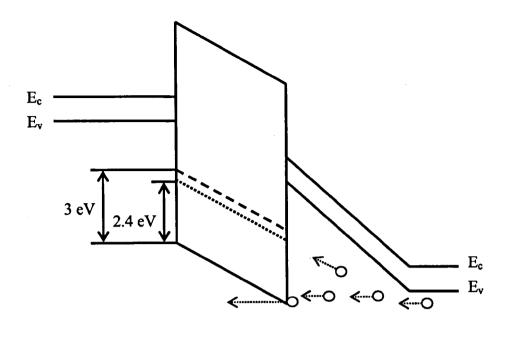

#### 1.4.2. Negative bias temperature instability

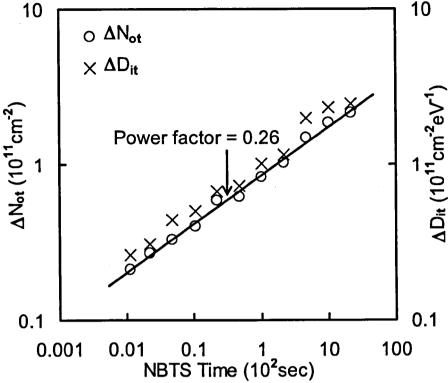

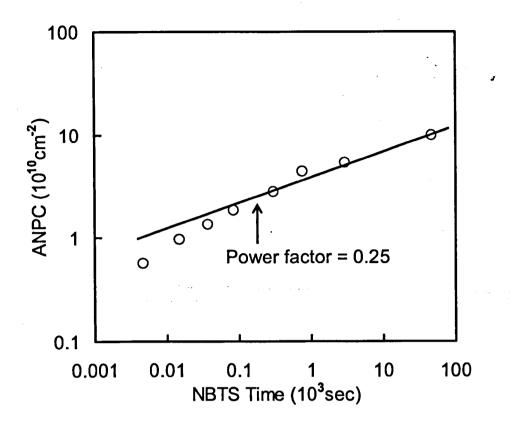

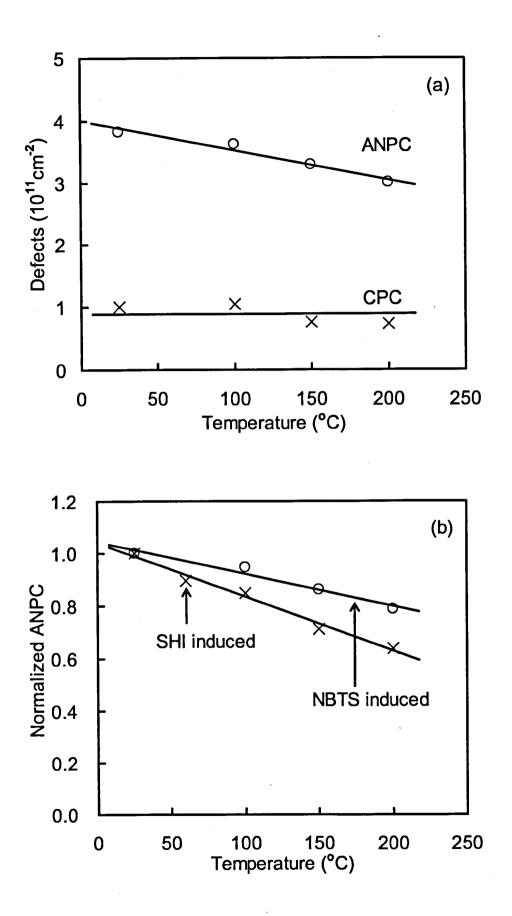

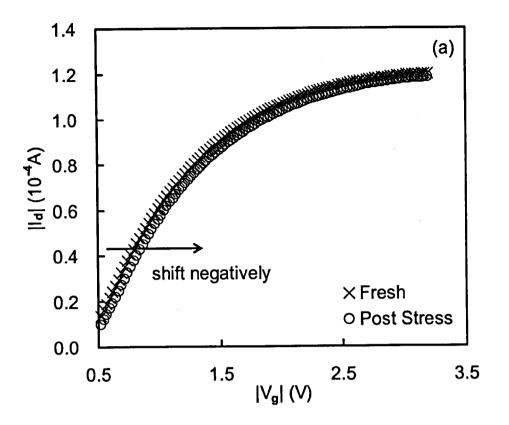

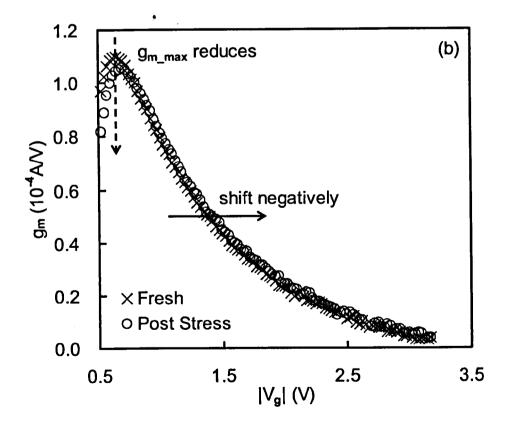

Negative bias temperature instability (NBTI) takes place in p-channel MOS devices under negative gate voltage at elevated temperature. NBTI leads to a number of adverse effects on devices, such as absolute drain current  $I_{dsat}$ , and transconductance  $g_m$ , decrease and absolute "off" current  $I_{off}$ , and threshold voltage  $V_t$  increase. Typical stress temperatures lie in the 100°C ~ 200°C range. The increased importance of NBTI has motivated many investigations in this area. As early as 1967, Deal et al. [108,109] reported that both the interface trap density  $N_{it}$ , and oxide charge density  $N_{ox}$ , increased upon negative bias stress. The rate of increase of both  $N_{it}$  and  $N_{ox}$  were similar. Six years later, Goetzberger et al [110] reported the same observation. Again in 1977, Jeppson and Svensson [111] confirmed the observation that there is an equal growth of the oxide charge and the interface trap density, independent of the BTI stress field and temperature. The close correlation between  $N_{it}$  and  $N_{ox}$  was also been confirmed by many other researches [111-115]. Another common observation is the generation of interface trap and positive oxide charge follow a power-law time dependence with a power factor in the range of  $0.2 \sim 0.3$  [105,111,116,117].

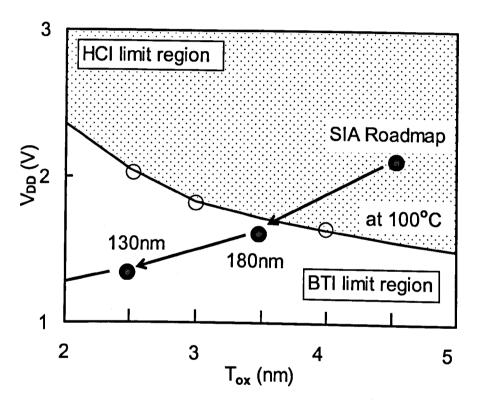

Figure 4. The transition of lifetime limitation mechanisms as a function of gate oxide thickness. When the thickness is below 3.5 nm, degradation due to BTI becomes to limit the device lifetime [106].

As the oxide becomes thinner, NBTI is becoming increasingly important, mainly because of two reasons. First, for each new generation of CMOS process, both operation temperature and electrical field increases. Second, to suppress the boron penetration and increase the dielectric constant, the nitrogen density in the gate oxide is increasing rapidly. It is reported that nitridation enhances NBTI and positive charge formation [105-107]. Figure 4 shows that for a gate oxide thinner than 3.5 nm,

the NBTI replaces hot carrier induced degradation as the limiting mechanism for device lifetime. It is therefore important to revisit the NBTI.

The most common models proposed for NBTI induced trap generation will be presented below. The first model discusses trap creation via hydrogen interaction dynamics. The second model proposed trap formation by the interaction of SiH with holes at the Si/SiO<sub>2</sub> interface. The last model describes trap creation via chemical species interaction and diffusion.

#### 1.4.2.1. Hydrogen model

A hydrogen terminated interface trap precursor can be represented by

$$Si_3 \equiv SiH$$

High electric field can dissociate the silicon-hydrogen bond, leading to:

$$Si_3 \equiv SiH \rightarrow Si_3 \equiv Si_{\bullet} + H^0$$

where  $H^0$  is a neutral interstitial hydrogen atom or atomic hydrogen. Atomic hydrogen is highly reactive and considered being a fast diffuser in the oxide [118]. The availability of SiH bonds for dissociation under high electric field is the rate-limiting process for this reaction.

Recent first-principles calculations show that the positively charged hydrogen or proton ( $H^+$ ) is the only stable charge state of hydrogen at the interface.  $H^+$  reacts directly with the SiH to form an interface trap, according to the reaction [119]:

$$Si_3 \equiv SiH + H^+ \rightarrow Si_3 \equiv Si_{\bullet} + H_2$$

.

The above reaction uses the fact that the SiH complex (or passivated dangling bond chemical species) is polarized such that a more positive charge resides near the Si atom and a more negative charge resides near the hydrogen atom. Mobile  $H^+$  migrates towards the negatively charged dipole region of the SiH molecule. The  $H^+$  atom then reacts with the  $H^-$  to form  $H_2$  leaving behind a positively charged Si dangling bond. In this model,  $H_2$  can later dissociate to again act as a catalyst to disrupt additional SiH bonds. This process, in theory, can continue so long as hydrogen is available and SiH bonds are available to react. The reaction between hydrogenous species ( $H^+$  or  $H_2$ ) and SiH bonds is the rate-limiting process for this reaction model.

#### 1.4.2.2. Hole model

This model explains NBTI induced trap formation by the interaction of SiH with "hot holes" or holes near or at the Si/SiO<sub>2</sub> interface [113,116,120-122]. Dissociation involving holes is given by

$$Si_3 \equiv SiH + h^+ \rightarrow Si_3 \equiv Si_{\bullet} + H^+$$

During NBTI stress, holes are attracted to the  $SiO_2/Si$  interface. This model is consistent with the results that a positive substrate bias accelerates NBTI degradation, reduces the device lifetime [107]. Holes induced SiH bonds dissociation is the rate-limiting process for this reaction model.

#### **1.4.2.3.** Electrochemical model

Jeppson and Svensson were the first to propose a diffusion-reaction concept to explain the  $t^{0.25}$  dependence of NBTI degradation [111].

$$Si_3 \equiv SiH + O_3 \equiv SiOSi \equiv O_3 \rightarrow Si_3 \equiv Si_{\bullet} + O_3 \equiv Si^+ + O_3 \equiv SiOH + e^-$$

Y D<sub>it</sub> Qf X to Si

According to this model, the silicon interface contains a large number of defects (i.e. SiH bond), which are electrically inactive, but may be electrically activated during NBTI. When the interface defect (i.e. SiH bond) is electrically activated, the diffusing species (e.g. H) leaves the defect site and reacts with the SiO<sub>2</sub> lattice to form an OH group bonded to an oxide atom, leaving a trivalent Si atom  $(Si_0^+)$  in the oxide and one trivalent Si<sub>s</sub> at the Si interface. The Si<sub>0</sub><sup>+</sup> forms the oxide charge and the Si<sub>s</sub> forms the interface trap. It has been proposed that X and Y in the reaction are H<sub>2</sub> and H<sup>0</sup>, respectively. This model agrees with the observation that similar amount of interface traps and positive charges are generated. The hydrogen reaction and diffusion are the rate-limiting process for this reaction model.

## References

- 1. S. M. Sze, "Physics of semiconductor devices," J. Willy & Sons, 1981.

- 2. G. E. Moore, "Cramming more components onto integrated circuits," Electronics, 38, 114 (1965).

- 3. R. R. Schaller, "Moore's law: past, present, and future," IEEE Spectrum, 34, 52 (1997).

- 4. R. D. Issac, "The future of CMOS technology," IBM J. Res. Dev., 44, 369 (2000).

- 5. P. Balk, The Si-SiO2 system, Elsevier, Amsterdam, Chapter 1, 1998.

- 6. C. R. Helms, The Si-SiO2 system, Elsevier, Amsterdam, Chapter 3, 1998.

- 7. G. Groeseneken, R. Bellens, G. Van den bosch and H.E. Maes, "Hot-carrier degradation in submicrometre MOSFETs: from uniform injection towards the real operating conditions," Semicond. Sci. Tech., 10, 1208 (1995).

- J. F. Zhang and W. Eccleston, "Effects of high field injection on the hot carrier induced degradation of submicrometer pMOSFET's," IEEE Trans. Elec. Dev., 42, 1269 (1995).

- 9. D. J. DiMaria and E. Cartier, "Mechanism for stress-induced leakage currents in thin silicon dioxide films," J. Appl. Phys., 78, 3883 (1995).

- J. De Blauwe, D. Wellekens, J. Van Houdt, R. Degraeve, L. Haspeslagh, G. Groeseneken and H. E. Maes, "Impact of tunnel-oxide nitridation on endurance and read-disturb characteristics of Flash E(2)PROM devices," Microelectronic Eng., 36, 301 (1997).

- R. Degraeve, G. Groeseneken, R. Bellens, J. L. Ogier, M. Depas, P. J. Roussel and H. E. Maes, "New insights in the relation between electron trap generation and the statistical properties of oxide breakdown," IEEE Trans. Elec. Dev., 45, 904 (1998).

- 12. J. H. Stathis and D. J. DiMaria, "Oxide scaling limit for future logic and memory technology," Microelectronic Eng., 48, 395 (1999).

- R. Degraeve, B. Kaczer and G. Groeseneken, "Ultra-thin oxide reliability: searching for the thickness scaling limit," Microelectronics Reliability, 40, 697 (2000).

- 14. V. V. Afanasev, A. Stesmans, A. G. Revesz and H. L. Hughes, "Trap generation in buried oxides of silicon-on-insulator structures by vacuum ultraviolet radiation," J. Electrochem. Soc., 144, 749 (1997).

- 15. M. Knoll, D. Braunig and W. R. Fahrner, "Generation of oxide charge and interface states by ionizing-radiation and by tunnel injection experiments," IEEE Trans. on Nucl. Sci., 29, 1471 (1982).

- E. M. Verbitskaya, V. K. Eremin and A. M.Ivanov, "Formation of radiation defects in high-resistivity silicon as a result of cyclic irradiation and annealing," Semiconductors, 31, 189 (1997).

- P. M. Lenahan and P. V. Dressendorfer, "Effects of bias on radiation-induced paramagnetic defects at the silicon-silicon dioxide interface," Appl. Phys. Lett., 41, 542 (1982).

- D. L.Griscom, "Diffusion of radiolytic molecular-hyderogen as a mechanism for the post-irradiation buildup of interface states in SiO2-on-si structures," J. Appl. Phys., 58, 2524 (1985).

- N. S. Saks, C. M. Dozier and D. B. Brown, "Time-dependence of interface trap formation in MOSFETs following pulsed irradiation," IEEE Trans. Nucl. Sci., 35, 1168 (1988).

- 20. D. B. Brown and N. S. Saks, "Time-dependence of radiation-induced interface trap formation in metal-oxide-semiconductor devices as a function of oxide thickness and applied field," J. Appl. Phys., **70**, 3734 (1991).

- 21. S. K. Lai, "Interface trap generation in silicon dioxide when electrons are captured by trapped holes," J. Appl. Phys., 54, 2540 (1983).

- 22. H. C. Shin and C. M. Hu, "Thin gate oxide damage due to plasma processing," Semicond. Sci. Tech., 11, 463 (1996).

- 23. T. Brozek and C. R. Viswanathan, "Increased hole trapping in gate oxides as latent damage from plasma charging," Semicond. Sci. Tech., **12**, 1551 (1997).

- 24. E. Cartier and J. H. Stathis, "Atomic hydrogen-induced degradation of the Si/SiO2 structure," Microelectronic Eng., 28, 3 (1995).

- 25. T. Brozek, L. H. Peng and C. R. Viswanathan, "Role of test stress levels in detection of process-induced latent charging damage in MOS transistors," in Proc 1<sup>st</sup> Int. Symp. on Plasma Process-Induced Damage, Santa Clara, p.81, USA (1996).

- 26. J. C. King and C. M. Hu, "Effect of low and high-temperature anneal on process induced damage of gate oxide," IEEE Elec. Dev. Lett., 15, 475 (1994).

- 27. M. Creusen, H. C. Lee, S. Vanhaelemeersch and G. Groeseneken, "The effect of plasma damage and different annealing ambients on the generation of latent interface states," in Proc 3<sup>rd</sup> Int. Symp. on Plasma Process-Induced Damage, Honolulu, p.217, USA (1998).

- 28. C. T. Wang, "Hot carrier design consideration for MOS devices and circuits," Van Nostrand Reinhold, New York, 1992.

- 29. P. E. Cottrell, R. R. Troutman and T. H. Ning "Hot-electron emission in nchannel IGFETS," IEEE Trans. Elec. Dev., 26, 520 (1979).

- W. L. Chen and T. P. Ma, "Channel hot-carrier induced oxide charge trapping in NMOSFET's," in Tech. Digest IEEE 37<sup>th</sup> Int. Electron Devices Meeting, Washington, p.731, USA (1991).

- 31. J. M. Aitken and D. R. Young, "Avalanche injection of holes into SiO2," IEEE Trans. Nucl. Sci., 24, 2128 (1977).

- 32. S. Ogawa, N. Shiono and M. Shimaya, "Neutral electron trap generation in SiO2 by hot holes," Appl. Phys. Lett., 56, 1329 (1990).

- 33. C. T. Sah, J. Y. C. Sun and J. J. T. Tzou, "Generation-annealing kinetics if the interface donor states at 0.25 eV above the midgap and the turn-around phenomena on oxidized silicon during avalanche electron injection," J. Appl. Phys., 54, 2547 (1983).

- 34. J. F. Zhang and W. Eccleston, "Positive bias temperature instability in MOSFET's," IEEE Trans. Elec. Dev., 45, 116 (1998).

- E. H. Nicollian, C. N. Berglund, P. F. Schmidt and J. M. Andrews, "Electron trapping/detrapping within thin SiO<sub>2</sub> films in the high field tunneling regime," J. Appl. Phys., 42, 5654 (1971).

- 36. D. J. DiMaria, The properties of electron and hole traps in thermal silicon dioxide layers grown on silicon. In S. T. Pantelides (ed.), *The Physics of SiO2 and its Interfaces*, New York: Pergamon, 160, 1978.

- R. F. De Keersmaecker and D .J. DiMaria, "Electron trapping and detrapping characteristics of arsenic-implanted SiO<sub>2</sub> layers," J. Appl. Phys., 51, 1085 (1980).

- 38. J. F. Zhang, S. Taylor, and W. Eccleston, "Electron trap generation in thermally grown SiO<sub>2</sub> under Fowler-Nordheim stress," J. Appl. Phys., **71**, 725 (1992).

- 39. J. F. Zhang, Wiley Encyclopedia of Electrical and Electronics Eng., 22, 540 (1999).

- 40. D. J. DiMaria and J. W. Stasiak, "Trap creation in silicon dioxide produced by hot-electrons," J. Appl. Phys., 65, 2342 (1989).

- 41. D. R. Wolters and J. J.van der Schoot, "Kinetics of charge trapping in dielectrics," J. Appl. Phys., 58, 831 (1985).

- 42. D. J. DiMaria and J. H. Stathis, "Anode hole injection, defect generation, and breakdown in ultrathin silicon dioxide films," J. Appl. Phys., 89, 5015 (2001).

- 43. D. Esseni, J. D. Bude and L. Selmi, "On interface and oxide degradation in VLSI MOSFETs Part I: Deuterium effect in CHE stress regime," IEEE Trans. Elec. Dev., 49, 247 (2002).

- 44. J. D. Bude, B. E. Weir and P. J. Silverman, "Explanation of stress-induced damage in thin oxides," in Tech. Digest IEEE 44<sup>th</sup> Int. Electron Devices Meeting, San Francisco, p.179, USA (1998).

- L. Do Thanh and P. Balk, "Elimination and generation of Si-SiO<sub>2</sub> interface traps by low-temperature hydrogen annealing," J. Electrochem. Soc., 135, 1797 (1988).

- 46. I. C. Chen, S. Holland, and C. Hu, "Electron-trap generation by recombination of electrons and holes in SiO<sub>2</sub>," J. Appl. Phys., **61**, 4544 (1987).

- H. Satake, S. Takagi and A. Toriumi, "Evidence of electron-hole cooperation in SiO<sub>2</sub> dielectric breakdown," International Reliability Physics Symposium Proceedings, 156 (1997).

- 48. B. Kaczer, R. Degraeve, N. Pangon, T. Nigam and G. Groeseneken, "Investigation of temperature acceleration of thin oxide time-to-breakdown," Microelectronic Eng., 48, 47 (1999).

- D. J. DiMaria, E. Cartier and D. Arnold, "Impact ionization, trap creation, degradation, and breakdown in silicon dioxide films on silicon," J. Appl. Phys., 73, 3367 (1993).

- 50. D. J. DiMaria, D. J. Buchaman, D. A. Stathis and R. E. Stahlbush, "Interface states induced by the presence of trapped holes near the silicon-silicon dioxide interface," J. Appl. Phys., 77, 2032 (1995).

- 51. D. J. DiMaria, "Temperature-dependence of trap creation in silicon dioxide," J. Appl. Phys., 68, 5234 (1990).

- 52. E. Cartier, D. A. Buchanan and J. G. Dunn, "Atomic hydrogen-induced interface degradation of reoxidized-nitrided silicon dioxide on silicon," Appl. Phys. Lett., 64, 901 (1994).

- 53. D. A. Buchanan, A. D. Marwick, D. J. DiMaria and L. Dori, "Hot-electroninduced hydrogen redistribution and defect generation in metal-oxidesemiconductor capacitors," J. Appl. Phys., 76, 3595 (1994).

- 54. P. E. Blochl and J. H. Stathis, "Hydrogen electrochemistry and stress-induced leakage current in silica," Phys. Rev. Lett., 83, 372 (1999).

- 55. A. Yokozawa and Y. Miyamoto, "First-principles calculations for charged states of hydrogen atoms in SiO2," Phys. Rev. B, 55, 13783 (1997).

- 56. V. V. Afanas'ev and A. Stesmans, "H-complexed oxygen vacancy in SiO2: Energy level of a negatively charged state," Appl. Phys. Lett., **71**, 3844 (1997).

- 57. K. F. Schuegraf and C. M. Hu, "Metal-Oxide-Semiconductor field-effecttransistor substrate current during Fowler-Nordheim tunneling stress and silicon dioxide reliability," J. Appl. Phys., **76**, 3695 (1994).

- 58. I. C. Chen, S. Holland, K. K. Young, C. Chang and C. Hu, "Substrate hole current and oxide breakdown," Appl. Phys. Lett., 49, 669 (1986).

- 59. Z. A. Weinberg, M. V. Fischetti and Y. Nissancohen, "SiO2-induced substrate current and its relation to positive charge in field-effect transistors," J. Appl. Phys., 59, 824 (1986).

- 60. D. J. DiMaria, E. Cartier and D. A. Buchanan, "Anode hole injection and trapping in silicon dioxide," J. Appl. Phys., 80, 304 (1996).

- H. Satake and A. Toriumi, "Substrate hole current generation and oxide breakdown in Si MOSFETs under Fowler-Nordheim electron tunneling injection," in Tech. Digest IEEE 39<sup>th</sup> Int. Electron Devices Meeting, Washington, p.337, USA (1993).

- 62. B. Kaczer, R. Degraeve, N. Pangon and G. Groeseneken, "The influence of elevated temperature on degradation and lifetime prediction of thin silicondioxide films," IEEE Trans. Elec. Dev., 47, 1514 (2000).

- 63. E. Cartier, J. C. Tsang, M. V. Fischetti and D. A. Buchanan, "Light emission during direct and Fowler-Nordheim tunneling in ultra thin MOS tunnel junctions," Microelectronic Eng., 36, 103 (1997).

- 64. M. Rasras, D. de Wolf, G. Groeseneken, B. Kaczer, R. Degraeve and H. E. Maes, "Photo-carrier generation as the origin of Fowler-Nordheim-induced substrate hole current in thin oxides," in Tech. Digest IEEE 45<sup>th</sup> Int. Electron Devices Meeting, Washington, p.465, USA (1999).

- 65. D. J. Dumin, J. R. Maddux, R. S. Scott and R. Subramoniam, "A model relating wearout to breakdown in thin oxides," IEEE Trans. Elec. Dev., **41**, 1570 (1994).

- 66. R. S. Scott, N. A. Dumin, T. W. Hughes, D. J. Dumin and B. T. Moore, "Properties of high voltage stress generated traps in thin silicon oxides," in Proc IEEE 33<sup>rd</sup> Int. Reliability Phys. Symp., Las Vegas, p.131, USA (1995).

- B. Schlund, C. Messick, J. S. Suehle and P. Chaparala, "A new physics-based model for time-dependent-dielectric-breakdown," in Proc IEEE 34<sup>th</sup> Int. Reliability Phys. Symp., Dallas, p.84, USA (1996).

- J. W. McPherson and H. C. Mogul, "Disturbed bonding states in SiO2 thinfilms and their impact on time-dependent dielectric breakdown," in Proc IEEE 36<sup>th</sup> Int. Reliability Phys. Symp., Reno, p.47, USA (1998).

- 69. M. Kimura, "Field and temperature acceleration model for time-dependent dielectric breakdown," IEEE Trans Elec. Dev., 46, 220 (1999).

- E. M. Vogel, J. S. Suehle, M. D. Edelstein, B. Wang, Y. Chen and J. B. Bernstein, "Reliability of ultrathin silicon dioxide under combined substrate hot-electron and constant voltage tunneling stress," IEEE Trans. Elec. Dev., 47, 1183 (2000).

- 71. D. J. DiMaria, "Defect generation under substrate-hot-electron injection into ultrathin silicon dioxide layers," J. Appl. Phys., 86, 2100 (1999).

- 72. D. J. DiMaria, "Defect generation in field-effect transistors under channel-hotelectron stress," J. Appl. Phys., 87, 8707 (2000).

- 73. D. J. DiMaria, "Electron energy dependence of metal-oxide-semiconductor degradation," Appl. Phys. Lett., 75, 2427 (1999).

- H. Uchida and T. Ajioka, "Electron trap center generation due to hole trapping in SiO2 under Fowler-Nordheim tunneling stress," Appl. Phys. Lett., 51, 433 (1987).

- H. Satake, S. Takagi, A. Toriumi, "Evidence of electron-hole cooperation in SiO2 dielectric breakdown," in Proc IEEE 35<sup>th</sup> Int. Reliability Phys. Symp., Denver, p.156, USA (1997).

- 76. D. J. DiMaria, "Hole trapping, substrate currents, and breakdown in thin silicon dioxide films," IEEE Elec. Dev. Lett., 16, 184 (1995).

- 77. A. Yankova, L. DoThanh and P. Balk, "Effects of thermal nitridation on the trapping characteristics of SiO2-films," Solid-State Elec., **30**, 939 (1987).

- D. Ielmini, A. S. Spinelli, M. A. Rigamonti and A. L. Lacaita, "Modeling of SILC based on electron and hole tunneling - Part I: Transient effects," IEEE Trans. Elec. Dev., 47, 1258 (2000).

- J. F. Zhang, S. Taylor and W. Eccleston, "A quantitative investigation of electron trapping in SiO<sub>2</sub> under Fowler-Nordheim stress," J. Appl. Phys., 71, 5989 (1992).

- M. Brox and W. Weber, "Dynamic degradation in MOSFET's Part I: The physical effects," IEEE Trans. Elec. Dev., 38, 1852 (1991).

- W. L. Chen, A. Balasinski and T. P. Ma, "Lateral profiling of oxide charge and interface traps near MOSFET junctions," IEEE Trans. Elec. Dev., 40, 187 (1993).

- R. Williams, "Photoemission of electrons from silicon into silicon dioxide," Physical Rev., 140, A569 (1965).

- D. J. DiMaria, "Capture and release of electrons on NA+-Related trapping sites in the SiO2 layer of metal-oxide-semiconductor structures at temperatures between 77-degrees-K and 296-degrees-K," J. Appl. Phys., 52, 7251 (1981).

- 84. B. E. Deal, "Current understanding of charges in thermally oxidized silicon structure," J. Electrochem. Soc., 121, 198c (1974).

- W. L. Warren, K. Vanheusden, J. R. Schwank, D. M. Fleetwood, P. S. Winokur, and R. A. B. Devine, "Mechanism for anneal-induced interfacial charging in SiO2 thin films on Si," Appl. Phys. Lett., 68, 2993 (1996).

- V. V. Afanas'ev and A. Stesmans, "Positive charging of thermal SiO2/(100)Si interface by hydrogen annealing," Appl. Phys. Lett., 72, 79 (1998).

- K. Vanheusden, W. L. Warren, R. A. B. Devine, D. M. Fleetwood, J. R. Schwank, M. R. Shaneyfelt, P. S. Winokur and Z. J. Lemnios, "Non-volatile memory device based on mobile protons in SiO2 thin films," Nature, 386, 587 (1997).

- 88. D. M. Fleetwood, M. J. Johnson, T. L. Meisenheimer, P. S. Winokur, W. L. Warren and S. C. Witczak, "1/f noise, hydrogen transport, and latent interface-

trap buildup in irradiated MOS devices," IEEE Trans. Nucl. Sci., 44, 1810 (1997).

- R. Bellens, E. De Schrijver, G. Van den bosch, G. Groeseneken, P. Heremans and H. E. Maes, "On the hot-carrier-induced poststress interface-trap generation in n-channel MOS-transistors," IEEE Trans. Elec. Dev., 41, 413 (1994).

- V. H. Chan and J. E. Chung, "The impact of nMOSFET hot-carrier degradation on CMOS analog subcircuit performance", IEEE J. Solid-St. Circ., 30, 644 (1995).

- 91. L. P. Trombetta, F. J. Feigl and R. J. Zeto, "Positive charge generation in metal-oxide-semiconductor capacitors," J. Appl. Phys., 69, 2512 (1991).

- R. K. Freitag, D. B. Brown and C. M. Dozier, "Evidence for two types of radiation-induced trapped positive charge," IEEE Trans. Nucl. Sci., 41, 1828 (1994).

- D. R. Young, E. A. Irene, D. J. DiMaria, R. F. De Keersmaecker and H. Z. Massoud, "Electron trapping in SiO2 at 295 and 77 K," J. Appl. Phys., 50, 6366 (1979).

- 94. R. E. Stahlbush, E. Cartier and D. A. Buchanan, "Anomalous positive charge formation by atomic hydrogen exposure," Microelectronic Eng., 28, 15 (1995).

- S. K. Lai and D. R. Young, "Effects of avalanche injection of electrons into silicon dioxide – generation of fast and slow interface states," J. Appl. Phys., 52, 6231 (1981).

- 96. D. M. Fleetwood, "Effects of hydrogen transport and reactions on microelectronics radiation response and reliability," Microelectronics Reliability, 42, 523 (2002).

- 97. A. J. Lelis and T. R. Oldham, "Time dependence of switching oxide traps," IEEE Trans. Nucl. Sci., 41, 1835 (1994).

- J. F. Zhang, H. K. Sii, G. Groeseneken and R. Degraeve, "Hole trapping and trap generation in the gate silicon dioxide," IEEE Trans. Elec. Dev., 48, 1127 (2001).

- J. F. Zhang, C. Z. Zhao, H. K. Sii, G. Groeseneken, R. Degraeve, J. N. Ellis and C. D. Beech, "Relation between hole traps and hydrogenous species in silicon dioxides," Solid-State Elec., 46, 1839 (2002).

- 100. J. F. Zhang, C. Z. Zhao, G. Groeseneken, R. Degraeve, J. N. Ellis and C. D. Beech, "Hydrogen induced positive charge generation in gate oxides," J. Appl. Phys., 90, 1911 (2001).

- 101. J. F. Zhang, C. Z. Zhao, A. H. Chen, G. Groeseneken and R. Degraeve, "Holetraps in silifcon dioxides – Part I: Properties," IEEE Trans. Elec. Dev., 51, 1267 (2004).

- 102. T. H. Ning, "Capture cross section and trap concentration of holes in silicon dioxide," J. Appl. Phys., 47, 1079 (1976).

- 103. G. Van den bosch, G. Groeseneken, H. E. Maes, R. B. Klein and N. S. Saks, "Oxide and interface degradation resulting from substrate hot-hole injection in metal-oxide-semiconductor field-effect transistors at 295 and 77 K," J. Appl. Phys., 75, 2073 (1994).