SCHOOL OF ENGINEERING

# CHARACTERIZATION OF HIGH-K LAYERS AS THE GATE DIELECTRIC FOR MOSFETS

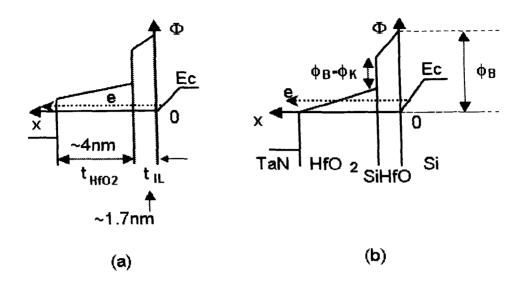

# **MOHAMMED B ZAHID**

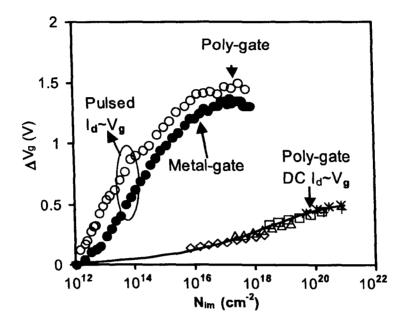

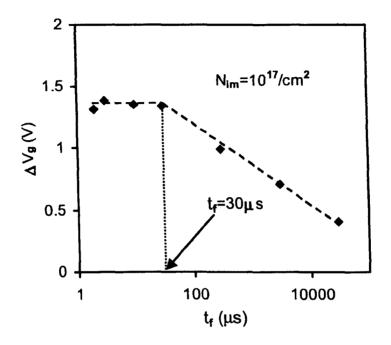

A thesis submitted in partial fulfillment of the requirements of Liverpool John Moores University for the degree of Doctor of Philosophy

This research programme was carried out in collaboration with the Interuniversity Micro-Electronics Center (IMEC)

**DECEMBER 2006**

### ACKNOWLEDGMENTS

Here I am writing the last page of my thesis. I know that trying to explicitly thank everybody who helped me, directly or indirectly to accomplish this work during these 3 years is by far not simple. So this is the moment and the part where I would like to express my gratitude to everyone which was involved.

I would like to acknowledge my supervisor, Prof. J. F. Zhang for all the help and continuous guidance, advice, encouragement and fruitful discussions throughout the project and for the opportunity he gave me to do my PhD project at Liverpool John Moores University and in Collaboration with Interuniversity Micro-Electronic Center (IMEC) in Belgium.

I also deeply appreciate Dr. C. Z. Zhao for his advice and support throughout the project. Many thanks to other members of our Microelectronic research group, Mr. Mo Huai Chang, Mr. Y. G. Wang for their discussions during the time that I worked on my project at Liverpool John Moore University.

I would like to acknowledge Prof. Guido Groeseneken for giving me the opportunity to carry out half of my PhD project at IMEC and my supervisor, Dr. Robin Degraeve, for all the help and continuous guidance and fruitful discussions throughout the project during my stay at IMEC. Many thanks to Florence, Thomas, Luigi, Lionel, Marc, Guillaume, Etienne, Bastien, Rachid, Adelina, Maria, Barry, Sahar, Christian, Rozbeh and Laurent. Without them, my stay at IMEC wouldn't have been so wonderful. Working with all of them has entirely been, and will always be, my pleasure and privilege. Many thanks to Yves, Michael, Muddassar, Sabri, Mohammed, Issac, Rumbi, Rizwana, Lokesh, Mathiew, Reinaldo, Heera, Surita, Yasmeen for the good time and laugh we had together in Liverpool.

Last but not the least, I owe deep gratitude to my parents and to all my family, for their love and support, for their patience with me and for the education I received during all these years.

Zahid Mohammed B,

Liverpool, December, 2006

The best way to predict the future is to invent it.

Alan Kay

You have an idea today, a better tomorrow, but the best of all ...never Sir Robert Watson Watt

### ABSTRACT

As the gate oxide thickness of the Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) is continuously scaled down with lateral device dimensions, the gate leakage current during operation increases exponentially. This increase in leakage current raises concerns regarding power consumption and device reliability. Alternative dielectrics with higher dielectric constant (high-k) than that of SiO<sub>2</sub> have been searched. High-k layers allow the use of physically thicker gate dielectrics, so that the gate leakage current is controlled. The intensive world-wide research has identified the Hfdielectric as the lead candidate for future CMOS technologies. However, the commercial application of Hf-dielectrics as the gate oxide has been held back by a number of issues, including process integration, low carrier mobility, and high instability.

This project focuses on characterizing the defect responsible for the instability of Hf-dielectrics. The thesis consists of six chapters. After an introduction in Chapter 1, the characterization techniques used are described in Chapter 2. Two main contributions are: setting up the pulse transfer characteristic technique and developing a newly improved charge pumping technique called Variable  $T_{charge}$ - $T_{discharge}$  Charge Pumping (VT<sup>2</sup>CP).

The research results are presented in Chapters 3, 4 and 5. Chapter 3 characterizes as-grown electron traps in  $HfO_2/SiO_2$  stacks. The issues addressed include the impact of measurement technique on electron trapping, contribution of different current components to trapping, trap location, and the capture cross section and trapping kinetics. It is shown that the use of pulse transfer characteristic technique is essential for measuring electron trapping, since the traditional quasi-dc transfer characteristic is too

slow and the loss of charges is significant. The trap assisted tunneling and the thermally enhanced conduction contributes little to trapping. The trapping does not pile up at the interfaces and the region near to one or both ends of  $HfO_2$  has little trapping, when compared with the trapping in the bulk. To evaluate the electron fluency through the gate stack, efforts are made to estimate the trapping-induced transient gate current through simulation. This allows the determination of two capture cross sections: one in the order of  $10^{-14}$ cm<sup>2</sup> and the other in the order of  $10^{-16}$ cm<sup>2</sup>.

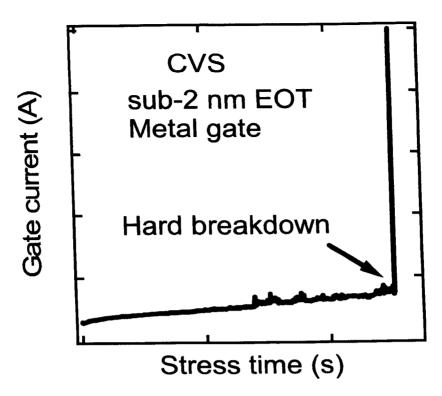

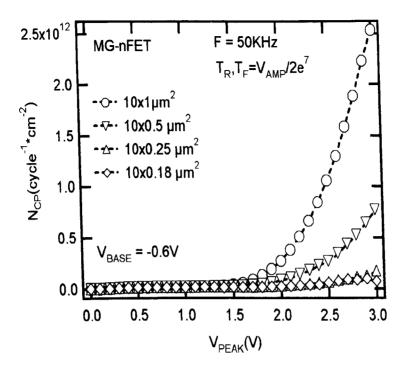

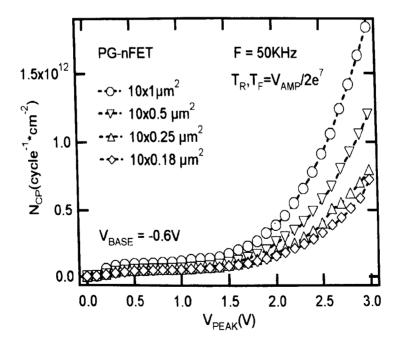

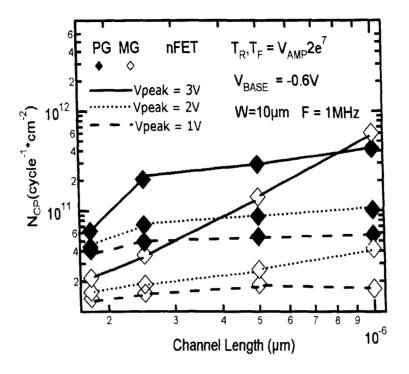

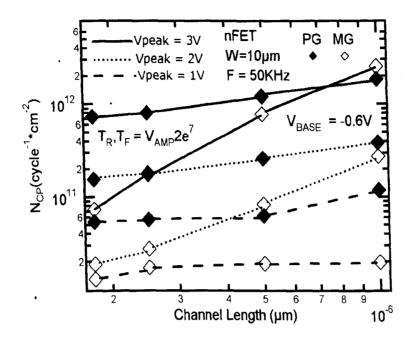

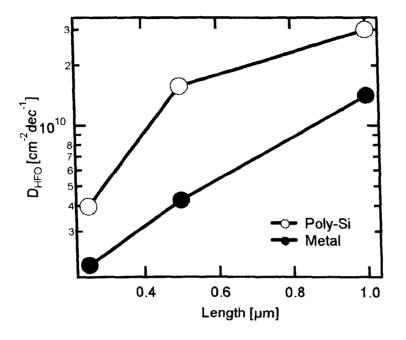

Chapter 4 concentrates on the characterization of generated electron traps and the time dependent dielectric breakdown (TDDB). Amplitude charge pumping and frequency sweep charge pumping are used to investigate the impact of gate electrodes and channel length on charging and discharging of the bulk defects. As channel length increases, it is found that bulk trapping increases and TDDB time shortens. Efforts are made to show that there is a quantitative correlation between the trapping and TDDB data. The newly improved  $VT^2CP$  is used to separate trapping in the interfacial SiO<sub>2</sub> from that in HfO<sub>2</sub>. The results show that new traps are generated in both layers and the generation follows a power law with similar power factors. Investigation is also carried out to assess the dependence of trap generation on process and deposition conditions. Finally, it is found that Hf-dielectric with metal gate always suffers hard-breakdown.

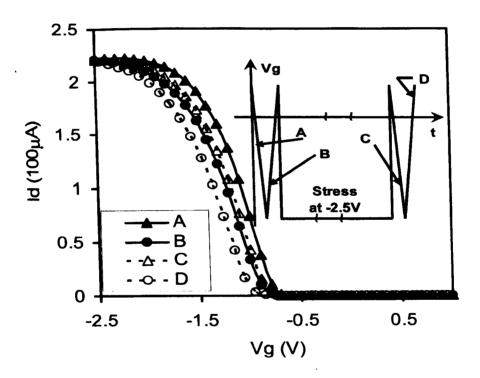

In Chapter 5, attention is turned to positive charging in Hf-dielectric. It is shown that the use of metal gate enhances the positive charging, when stressed under a positive gate bias. This is explained by assuming that there is a large number of hydrogenous species within the metal gate or at its interface with gate dielectric. Two types of threshold voltage instabilities have been identified for pMOSFETs. The first one results in a loop in the transfer characteristics when a pulse is applied to the gate. The second one is caused by the generation of new positive charge. Both are enhanced by

V

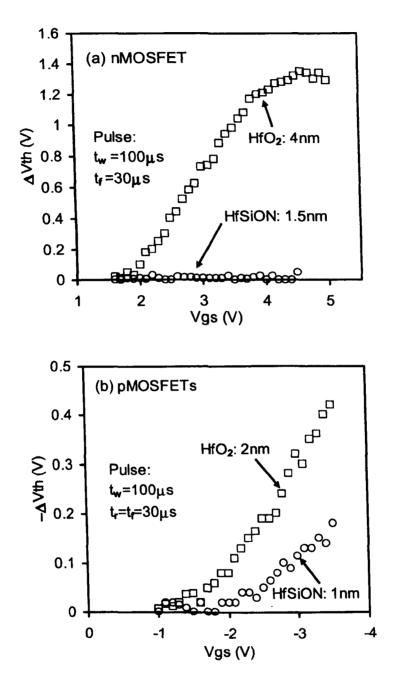

nitridation. For sub-2nm Hf-dielectric, the threshold voltage instability of pMOSFETs can be more severe than that of nMOSFETs and it can be a limiting factor for the operation voltage.

Finally, the project is summarized in Chapter 6 and the future work is discussed.

### LIST OF PUBLICATIONS

### CONFERENCES PAPERS

- M.B.Zahid, L.Pantisano, R.Degraeve, M.Aoulaiche, I.Ferain, L.Trojman, E.San Andres, S.Severi, M.Toledano, B.O'Sullivan S.De Gendt, M.Heyns, G.Groeseneken, "Optimization of hole trapping in HfSiON causing V<sub>T</sub>-instability in 1nm EOT pMOS," Accepted and to be Presented at VLSI 2007

- M.B.Zahid, R. Degraeve, L. Pantisano, J. F. Zhang, G. Groeseneken, "Defects Generation in SiO<sub>2</sub>/HfO<sub>2</sub> Studied With Variable t<sub>charge</sub> - t<sub>discharge</sub> Charge Pumping (VT<sup>2</sup>CP)," Accepted and to be Presented at IRPS 2007

- M.B.Zahid, R. Degraeve, J. F. Zhang, G. Groeseneken," Impact of Process Conditions on Interface and High-κ Trap Density Studied by Variable Tcharge-Tdischarge Charge Pumping (VT<sup>2</sup>CP)," Accepted and to be Presented at INFOS 2007

- M.B.Zahid, R.Degraeve, T.Kauerauf, G.Groeseneken, J.F.Zhang, "Investigation of Channel-length dependent Time-to-Breakdown (t<sub>BD</sub>) with variable frequency charge pumping," in 36th IEEE SISC, Arlington, USA, November 2005

- C.Z.Zhao, M.B.Zahid, J. F. Zhang, G. Groeseneken, R. Degraeve, and S. De Gendt, "Properties and dynamic behavior of electron traps in HfO<sub>2</sub>/SiO<sub>2</sub> stacks," Microelectronic Eng., vol.80, pp.366-369, 2005.

- M. Toledano-Luque, L. Pantisano, R. Degraeve, M.B.Zahid, I. Ferrain, E. San Andrés, G. Groeseneken, S. De Gent," Charge Pumping HfSiON defect spectroscopy after Substrate Hot Electron Injection," Accepted and to be Presented at INFOS 2007

R. Degraeve, T. Kauerauf, M. Cho, M. B. Zahid, L-Å. Ragnarsson, D.P. Brunco, B. Kaczer, Ph. Roussel, S De Gendt, G. Groeseneken, "Degradation and breakdown of 0.9 nm EOT SiO<sub>2</sub>/ALD HfO<sub>2</sub>/metal gate stacks under positive Constant Voltage Stress", IEDM Technical Digest, pp. 419-422, 2005

#### JOURNAL PAPERS

- 1. C. Z. Zhao, M.B.Zahid, and J. F. Zhang," Threshold voltage instability of pMOSFETs with Hf-based dielectrics," Applied Physics Letters 2006, Accepted

- Z. Zhao, J. F. Zhang, M.B.Zahid, B. Govoreanu, G. Groeseneken, and S. De Gendt," Determination of capture cross sections for as-grown electron traps in HfO<sub>2</sub>/HfSiO stacks", J. Appl. Phys. 100, 093716 (2006)

- J.F.Zhang, C.Z.Zhao, M.B.Zahid, G. Groseneken, R. Degraeve, and S. De Gendt," An assessment of the location of as-grown electron traps in HfO<sub>2</sub> /HfSiO stacks", IEEE Electron Dev. Lett., 27:1010, 817-820, 2006.

- T. Kauerauf, R. Degraeve, M.B.Zahid, M. Cho, B. Kaczer, Ph. Roussel, G. Groeseneken, H. Maes and S. De Gendt," Abrupt breakdown in dielectric/metal gate stacks: A potential reliability limitation?," Electron Devices Letters Vol.26, Issue:10, pp 773-775, 2005

- 5. C.Z.Zhao, J.F.Zhang, and M.B.Zahid, "Impact of gate materials on positive charge formation in HfO<sub>2</sub>/SiO<sub>2</sub> stacks," Appl. Phys. Lett. 89, 023507, 2006

- M. Toledano-Luque, L. Pantisano, R. Degraeve, M.B.Zahid, E. San Andrés, G. Groeseneken, S. De Gent," New Developments In Charge Pumping Measurements On Thin Stacked Dielectrics," In Preparation and to be submitted to TED

# **LIST OF ABBREVIATIONS**

| Abbreviations         | Signification                                     |

|-----------------------|---------------------------------------------------|

| ALCVD                 | Atomic Layer Chemical Vapor Deposition            |

| ALD                   | Atomic Layer Deposition                           |

| APC                   | Anomalous Positive charges                        |

| BD                    | BreakDown                                         |

| CP                    | Charge Pumping                                    |

| CVS                   | Constant Voltage Stress                           |

| DPN                   | Decoupled Plasma Nitridation                      |

| ЕОТ                   | Equivalent Oxide Thickness                        |

| FGA                   | Forming Gas Anneal                                |

| FUSI                  | Fully Silicide                                    |

| HBD                   | Hard BreakDown                                    |

| HfO <sub>2</sub>      | Hafnium dioxide                                   |

| HfSiON                | Hafnium Silicate Oxide Nitride                    |

| IL                    | Interfacial Layer                                 |

| MOCVD                 | Metal Organic Chemical Vapor Deposition           |

| MOSFET                | Metal Oxide Semiconductor Field Effect Transistor |

| NBTI                  | Negative Bias Temperature Instability             |

| N <sub>2</sub>        | Nitrogen                                          |

| NH <sub>3</sub>       | Ammonia (Nitrogen bounded to hydrogen)            |

| <b>O</b> <sub>2</sub> | Dioxygen                                          |

| PDA                   | Post Deposition Anneal                            |

| PVD                   | Physical Vapor Deposition                         |

| SBD                   | Soft BreakDown                                    |

| SiO <sub>2</sub>      | Silicon Oxide                                     |

| SILC                  | Stress Induced Leakage Current                    |

| SION                  | Silicon Oxide Nitride                             |

| TaN                   | Tantalum Nitride                                  |

| TDDB                  | Time Dependent Dielectric Breakdown               |

| TiN                   | Titanium Nitride                                  |

| WKB                   | Wentzel-Kramers-Brillouin                         |

| ZrO <sub>2</sub>      | Zirconium dioxide                                 |

| Symbols                       | Description                                                 | Unit                               |

|-------------------------------|-------------------------------------------------------------|------------------------------------|

| Δ                             | Differential operator                                       |                                    |

| σ                             | Capture cross section                                       |                                    |

| β                             | Beta                                                        |                                    |

| μ                             | Micro                                                       |                                    |

| ħ                             | h is the Plank's constant                                   | ħ=h/(2π)                           |

| E SiO2                        | Dielectric Constant of SiO <sub>2</sub>                     | t                                  |

| E o                           | Electric permittivity of vacuum                             | F/cm                               |

| $\mathcal{E}_{iL}$            | Dielectric constant of the interfacial layer                |                                    |

| E HfO                         | Dielectric constant of HfO <sub>2</sub>                     |                                    |

| Ψms                           | Work function difference                                    | V                                  |

| <b>Φ(x)</b>                   | Bottom edge of conduction band in the oxide                 | eV                                 |

| $\phi_{\scriptscriptstyle B}$ | Energy barrier height at the IL / Substrate L               | eV                                 |

| Øĸ                            | Conduction band offset between HfO <sub>2</sub> and Silicon | eV                                 |

| ρ                             | Volume density                                              | cm <sup>3</sup>                    |

| $\Delta_{I}$                  | Current Step                                                | A                                  |

| A                             | Area                                                        | cm <sup>2</sup>                    |

| Cox                           | Oxide Capacitance                                           | F cm <sup>-2</sup>                 |

| DIL                           | Density of Interface Traps                                  | cm <sup>-2</sup>                   |

| D <sub>HFO</sub>              | HfO <sub>2</sub> trap density per decade frequency          | cm <sup>-2</sup> dec <sup>-1</sup> |

| D <sub>HfO2</sub>             | Trap generation in HfO <sub>2</sub>                         | cm <sup>-2</sup> dec <sup>-1</sup> |

| DOT                           | Frequency dependent HfO <sub>2</sub> bulk traps density     | cm <sup>-2</sup>                   |

| D <sub>SiO2</sub>             | Trap generation in SiO <sub>2</sub>                         | cm <sup>-2</sup> dec <sup>-1</sup> |

| Eij                           | Sub-band energy level                                       | eV                                 |

| E <sub>F</sub>                | Fermi level                                                 | eV                                 |

| EOT                           | Equivalent Oxide Thickness                                  | nm                                 |

| f                             | frequency                                                   | Hz                                 |

| Feff                          | Effective electrical filed strength                         | eV                                 |

| f <sub>ij</sub>               | Frequency at the dielectric /substrate interface            | Hz                                 |

| gi                            | Degeneracy of the i <sup>th</sup> valley                    |                                    |

| I <sub>CP</sub>               | Charge pumping current                                      | Α                                  |

| ID                            | Drain current                                               | Α                                  |

| IG                            | Gate current                                                | Α                                  |

| J <sub>de</sub>               | Gate current density caused by charge trapping              | Area/cm <sup>2</sup>               |

| Jge                           | Current density caused by electron flowing through the gate | Area/cm <sup>2</sup>               |

| J <sub>gm</sub>               | Gate current density per unit area                          | Area/cm <sup>2</sup>               |

| Jg                            | Gate current density                                        | Area/cm                            |

| k                             | Boltzmann constant                                          | J/K                                |

| L                             | Length                                                      | μm                                 |

| m <sub>di</sub>               | The density of states effective mass                        | kg                                 |

| m <sub>zi</sub>               | the effective mass in the i <sup>th</sup> valley            | kg                                 |

| m <sub>iL</sub>               | Electron mass in IL                                         | kg                                 |

| mo                            | Free electron mass                                          | kg                                 |

| m                             | Effective electron mass                                     | 1                                  |

Effective electron mass

Electron mass in SiO<sub>2</sub>

mox

m<sub>SiO2</sub>

# LIST OF SYMBOLS

kg

kg

| N <sub>A</sub><br>N <sub>depl</sub> | Substrate doping density<br>Charged dopant per unit area in the depletion layer | cm <sup>-3</sup> |

|-------------------------------------|---------------------------------------------------------------------------------|------------------|

| N <sub>ic</sub>                     | Electron fluency calculated with the transient gate current                     | cm <sup>-2</sup> |

| N <sub>ij</sub>                     | Density of charge carriers available for tunnelling                             | cm <sup>-2</sup> |

| N <sub>im</sub>                     | Electron fluency calculated without the transient gate current                  | cm <sup>-2</sup> |

| N <sub>inj</sub>                    | Electron fluency                                                                | cm <sup>-2</sup> |

| Niny                                | Total carrier density in the inversion layer                                    | cm <sup>-2</sup> |

| q                                   | Elementary charge                                                               | C                |

| Q                                   | Charge                                                                          | C                |

| Qc                                  | Pumped charge per cycle                                                         | C                |

| T                                   | Temperature                                                                     | К                |

| t <sub>BD</sub>                     | Time to breakdown                                                               | Sec              |

| t <sub>f</sub>                      | Fall time of the pulse                                                          | μs               |

| t <sub>g</sub>                      | Negligible trapping region located near the gate                                | nm               |

| t <sub>iL</sub>                     | Thickness of the interfacial layer                                              | nm               |

| t <sub>HfO2</sub>                   | Thickness of the HfO <sub>2</sub>                                               | nm               |

| t <sub>pw</sub>                     | Pulse width                                                                     | μs               |

| t <sub>top</sub>                    | Peak period of the pulse                                                        | μs               |

| ts                                  | Negligible trapping region from the HfSiO interface                             | nm               |

| t <sub>r</sub>                      | Rise time of the pulse                                                          | μs               |

| T <sub>Rij</sub>                    | Correction factor                                                               |                  |

| <b>TWKB</b> <sub>ij</sub>           | WKB tunnelling probability                                                      |                  |

| V <sub>TH</sub>                     | Threshold Voltage                                                               | V                |

| VTHC                                | Created Threshold Voltage                                                       | V                |

| VG                                  | Gate Voltage                                                                    | V                |

| V <sub>HfO2</sub>                   | Voltage drop across HfO <sub>2</sub>                                            | V                |

| ViL                                 | Voltage drop across the Interface Layer                                         | V                |

| Vox                                 | Voltage drop across the oxide                                                   | V                |

| W                                   | Width                                                                           | μm               |

| X <sub>Hf</sub>                     | HfO <sub>2</sub> thickness                                                      | nm               |

and the first water in the state of the second state of the second

# CONTENTS

| Acknowledgments                                                                                                                                                             | ii                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Abstract                                                                                                                                                                    | iv                           |

| List of publications                                                                                                                                                        | vii                          |

| List of Abbreviations                                                                                                                                                       | ix                           |

| List of Symbols                                                                                                                                                             | X                            |

| Contents                                                                                                                                                                    | xii                          |

| Chapter 1 Introduction                                                                                                                                                      | 15                           |

| 1.1 Historical evolution                                                                                                                                                    | 15                           |

| 1.2 Challenges for further downscaling                                                                                                                                      | 16                           |

| 1.3 Requirements of high-k gate dielectrics                                                                                                                                 |                              |

| 1.4 Outline of the thesis                                                                                                                                                   | 19                           |

| Chapter 2 Characterization Techniques for High-k Dielectrics                                                                                                                | 23                           |

| <ul> <li>2.1 Conventional techniques.</li> <li>2.1.1 Conventional C-V</li> <li>2.1.2 Conventional I<sub>D</sub> ~V<sub>G</sub>.</li> <li>2.1.3 Stress and sense.</li> </ul> | 24<br>25                     |

| <ul> <li>2.2 Times resolved techniques.</li> <li>2.2.1 Pulsed C-V</li> <li>2.2.2 Pulsed I<sub>D</sub>~V<sub>G</sub>.</li> </ul>                                             | <b> 28</b><br>28             |

| <ul> <li>2.3 Formulae for pulsed I<sub>D</sub>~V<sub>G</sub> technique</li></ul>                                                                                            | 33<br>34                     |

| <ul> <li>2.4 Charge Pumping (CP)</li></ul>                                                                                                                                  | <b> 39</b><br>40<br>42<br>46 |

| 2.5 Time Dependent Dielectric Breakdown (TDDB)<br>2.5.1 Physics of breakdown<br>2.5.1.1 Fowler-Nordeim Tunneling                                                            | 52                           |

| <ul><li>2.5.1.2 Direct Tunneling</li><li>2.5.1.3 Trap Assisted Tunneling</li><li>2.5.1.4 Poole-Frenkel mechanism</li></ul>                                                  | 55<br>56<br>56               |

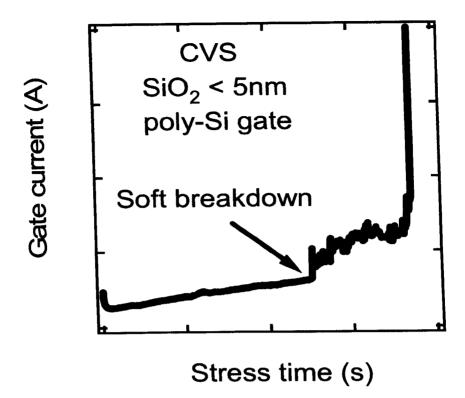

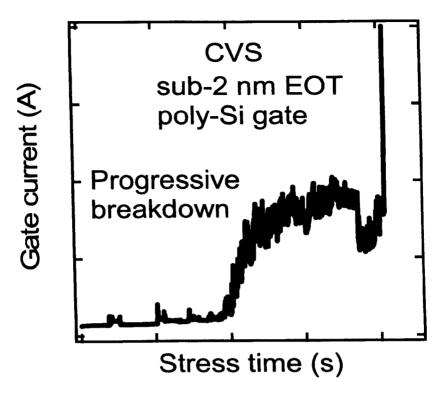

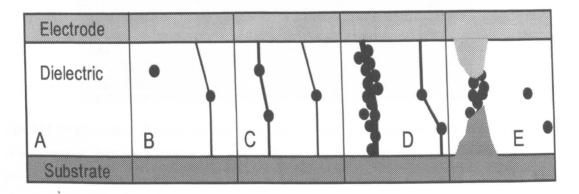

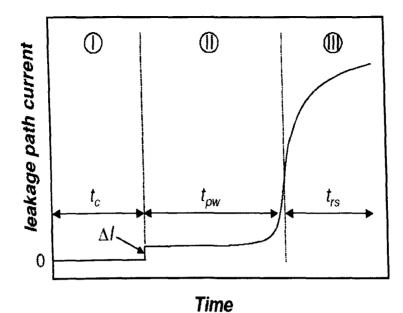

| <ul><li>2.5.2 Techniques of Breakdown Tests</li><li>2.5.3 Soft Breakdown and Hard Breakdown</li><li>2.5.3.1 Oxide Breakdown</li></ul>                                       | 61                           |

| 2.5.4 Advanced measurement sequences                                                                                                                | 68                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

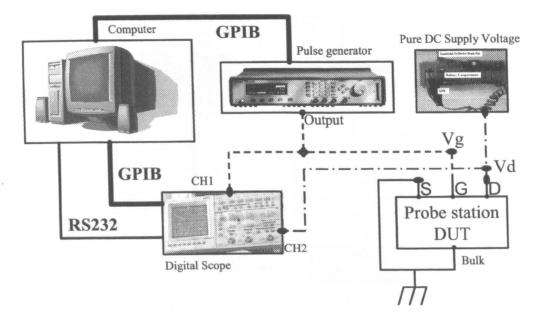

| 2.6 Instrument and technical overview                                                                                                               |                              |

| 2.6.1 Measurement set-up                                                                                                                            |                              |

| 2.6.1.1 Pulse $I_{D} \sim V_{G}$                                                                                                                    |                              |

| 2.6.1.2 Charge Pumping                                                                                                                              |                              |

| 2.6.1.3 Time dependent dielectric breakdown                                                                                                         |                              |

| 2.6.2 Instruments characteristics                                                                                                                   |                              |

| 2.6.2.1 Pure DC Voltage Supply characteristics                                                                                                      |                              |

| 2.6.2.2 Pulse Generator characteristics                                                                                                             |                              |

| 2.6.2.3 Oscilloscope characteristics                                                                                                                | 79                           |

| 2.6.2.4 Keithley K4200                                                                                                                              | 79                           |

| 2.7 Conclusion                                                                                                                                      | 80                           |

| Chapter 3 Characterization of as-grown electron traps                                                                                               |                              |

| 3.1 Introduction                                                                                                                                    |                              |

| 3.2 Properties and dynamic behaviour of electron traps in HfO <sub>2</sub> /SiO <sub>2</sub>                                                        | stacks 83                    |

| 3.2.1 Devices and Techniques                                                                                                                        |                              |

| 3.2.2 Impacts of measurement techniques on trapping                                                                                                 |                              |

| 3.2.3 Dependence on conduction mechanism                                                                                                            |                              |

| -                                                                                                                                                   |                              |

| 3.3 Location of as grown electron traps in HfO <sub>2</sub> /HfSiO stacks                                                                           |                              |

| 3.3.1 Devices and Techniques                                                                                                                        |                              |

| 3.3.2 Test Condition                                                                                                                                |                              |

| 3.3.3 Location of as grown electron traps                                                                                                           |                              |

| 3.4 Determination of capture cross section for as-grown electron trap                                                                               | s in                         |

| HfO <sub>2</sub> /HfSiO stacks                                                                                                                      |                              |

| 3.4.1 Devices                                                                                                                                       |                              |

| 3.4.2 Test condition and measurement                                                                                                                |                              |

| 3.4.3 Transient gate current estimation                                                                                                             |                              |

| 3.4.3.1 Numerical modeling of gate current without trapping                                                                                         |                              |

| 3.4.3.2 Numerical modeling of gate current with trapping                                                                                            |                              |

| 3.4.4 Capture cross section extraction                                                                                                              | 112                          |

| 3.4.4.1 Electron fluency estimation                                                                                                                 |                              |

| 3.4.4.2 Capture cross section extraction and trapping kinetics                                                                                      |                              |

| 3.4.5 Dependence on fabrication processes and techniques                                                                                            |                              |

| 3.5 Conclusions                                                                                                                                     |                              |

|                                                                                                                                                     | 174                          |

| •                                                                                                                                                   |                              |

| Chapter 4 Generated electron traps and breakdown                                                                                                    | 124                          |

| •                                                                                                                                                   | 124                          |

| Chapter 4       Generated electron traps and breakdown         4.1 Introduction                                                                     | 124<br>124                   |

| Chapter 4       Generated electron traps and breakdown         4.1 Introduction                                                                     | 124<br>124<br>125<br>125     |

| Chapter 4       Generated electron traps and breakdown         4.1 Introduction                                                                     | 124<br>124<br>125<br>125     |

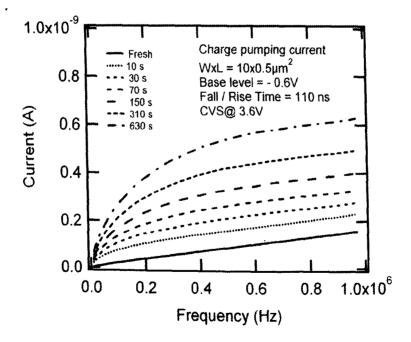

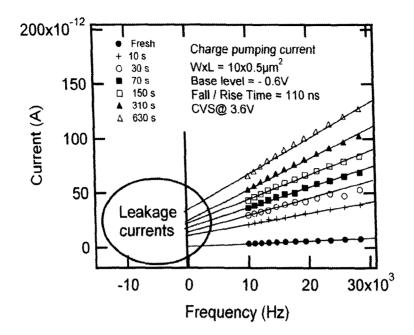

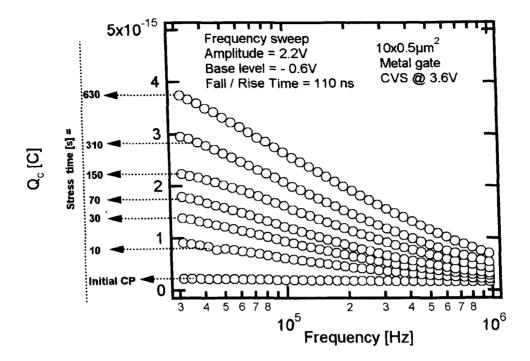

| Chapter 4Generated electron traps and breakdown4.1 Introduction4.2 Conventional Charge Pumping (CP)                                                 | 124<br>124<br>125<br>125<br> |

| Chapter 4       Generated electron traps and breakdown         4.1 Introduction                                                                     |                              |

| Chapter 4       Generated electron traps and breakdown         4.1 Introduction       4.1 Introduction         4.2 Conventional Charge Pumping (CP) |                              |

| Chapter 4       Generated electron traps and breakdown         4.1 Introduction       4.1 Introduction         4.2 Conventional Charge Pumping (CP) |                              |

| Chapter 4       Generated electron traps and breakdown         4.1 Introduction       4.1 Introduction         4.2 Conventional Charge Pumping (CP) |                              |

| 4.3.4 Trap generation in different thickness of HfO <sub>2</sub> and different thickness as | nd    |

|---------------------------------------------------------------------------------------------|-------|

| composition of HfSiO characterized by using VT <sup>2</sup> CP                              | 156   |

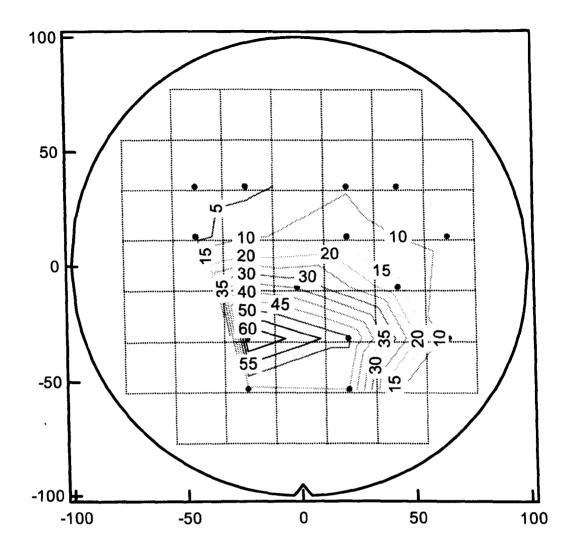

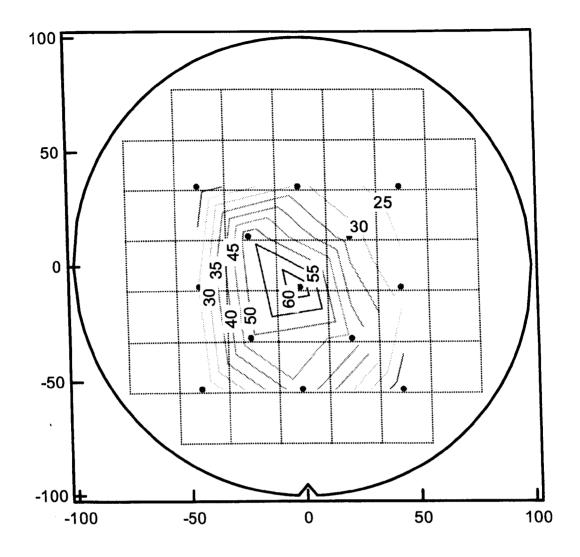

| 4.3.5 Trap Generation evaluated by TDDB and waver level uniformity                          | 160   |

| 4.3.5.1 Evaluation of 2nm HfO <sub>2</sub>                                                  | .160  |

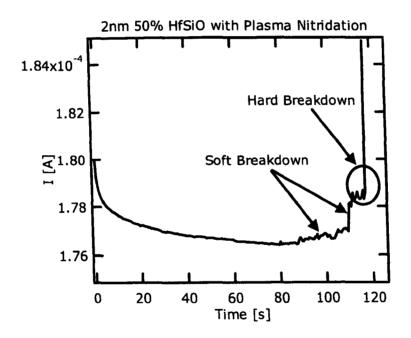

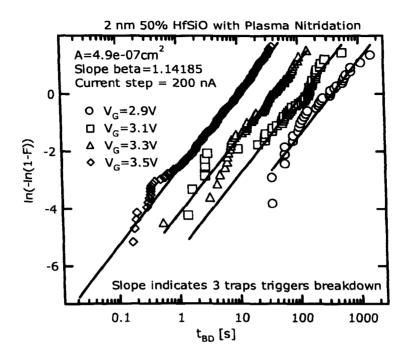

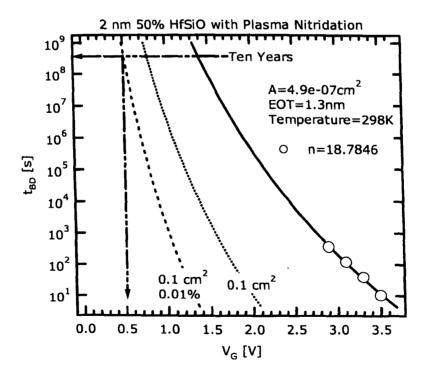

| 4.3.5.2 Evaluation of 2nm 50% HfSiON with Plasma Nitridation                                |       |

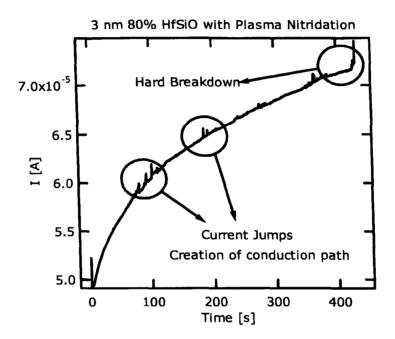

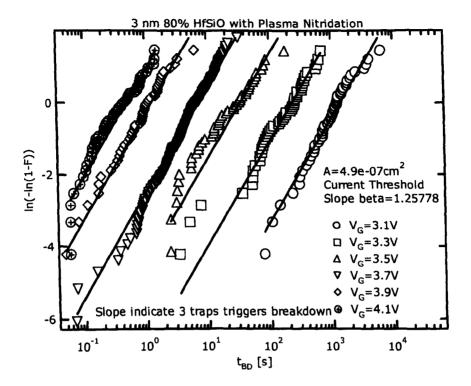

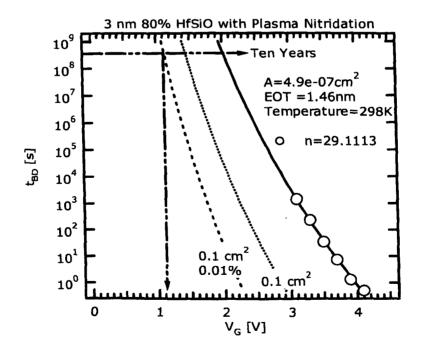

| 4.3.5.3 Evaluation of 3nm 80% HfSiON with Plasma Nitridation                                |       |

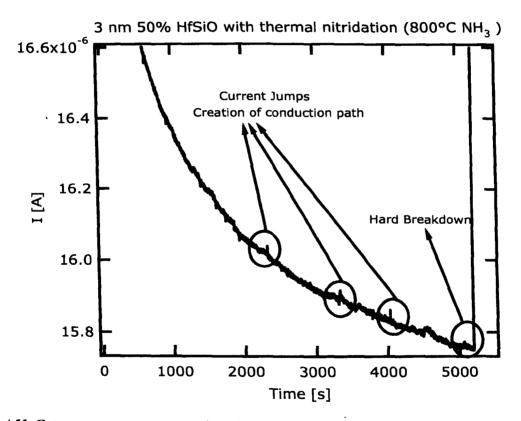

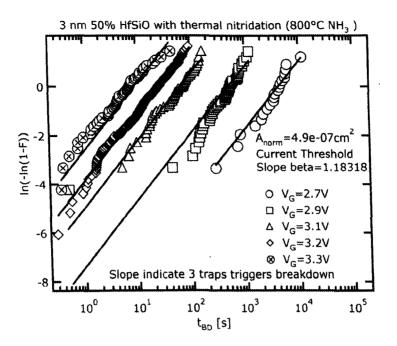

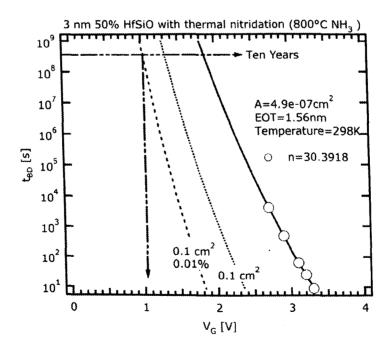

| 4.3.5.4 Evaluation of 3nm 50% HfSiON with Thermal Nitridation                               | . 168 |

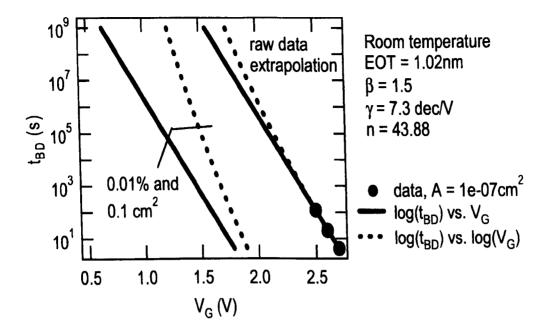

| 4.4 Time Dependent-Dielectric Breakdown                                                     | 170   |

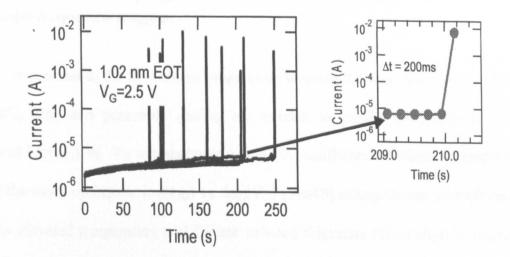

| 4.4.1 Hard breakdown in dielectric/metal gate stack                                         | 172   |

| 4.5 Conclusion                                                                              | 174   |

| Chapter 5 Positive charges and $V_{TH}$ instability                                         | 177   |

| 5.1 Introduction                                                                            | . 177 |

| 5.2 Impact of the gate material on positive charge                                          | . 178 |

| 5.3 Threshold voltage instability of pMOSFETs with Hf-based dielectrics                     | . 184 |

| 5.3.1 Comparisons of V <sub>TH</sub> instability between nMOS and pMOS                      | . 184 |

| 5.4 Separation of as-grown traps from generated traps                                       | . 190 |

| 5.4.1 Generated V <sub>TH</sub> instability                                                 | . 191 |

| 5.5 Impact on operation Voltage                                                             | 196   |

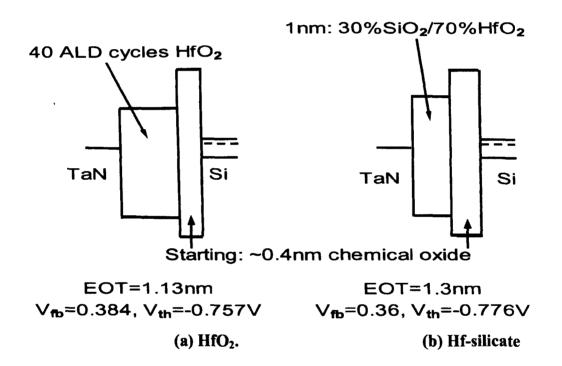

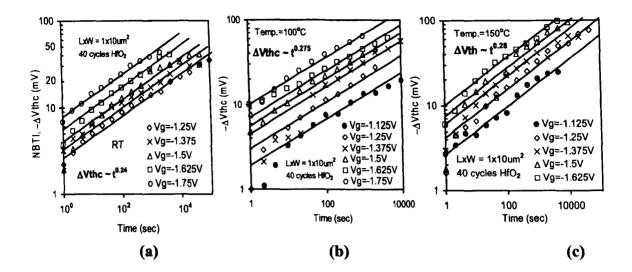

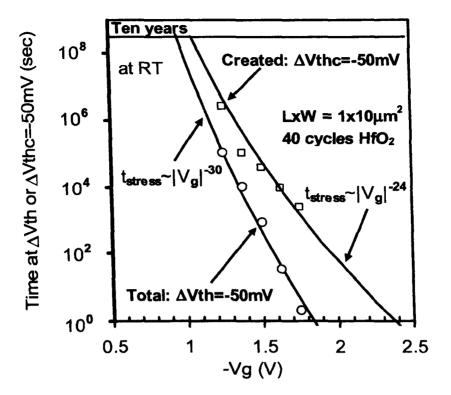

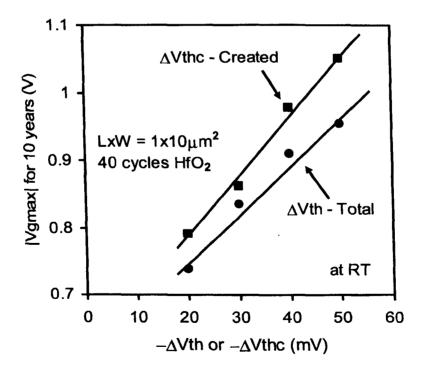

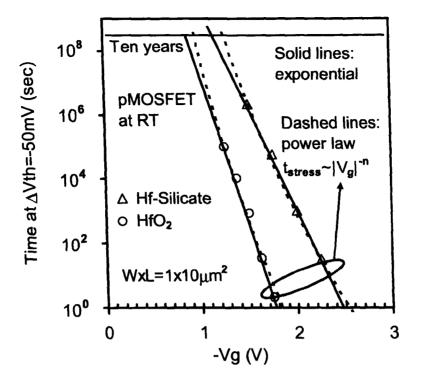

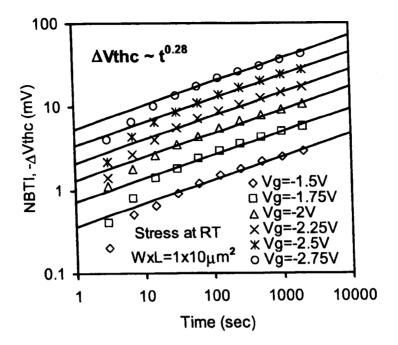

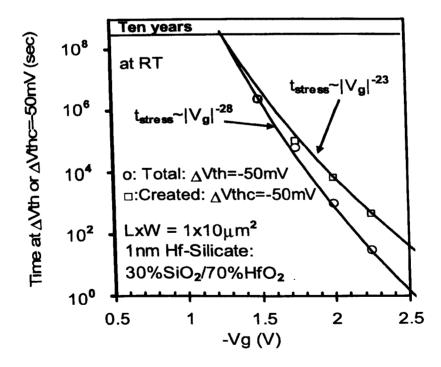

| 5.5.1 NBTI generation in HfO <sub>2</sub>                                                   |       |

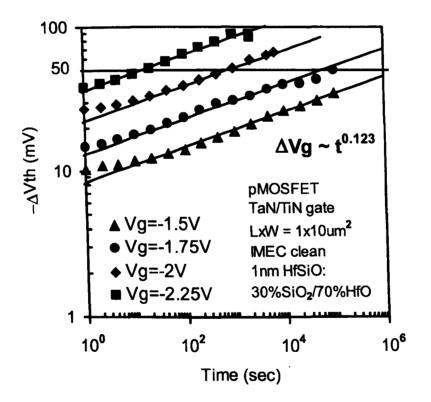

| 5.5.2 NBTI generation in Hf-silicate                                                        |       |

| 5.6 Impact of Nitridation on $V_{TH}$ instability: Comparison between ALD vs                |       |

| MOCVD                                                                                       | 204   |

| 5.6.1 Impact of process conditions on V <sub>TH</sub> instability                           |       |

| 5.7 Conclusions                                                                             |       |

|                                                                                             |       |

| Chapter 6 Conclusions and future work                                                       | . 215 |

| 6.1 Conclusion                                                                              | 215   |

| 6.1.1 Conclusions on the characterizations of as grown electrons traps                      |       |

| 6.1.2 Conclusions on the generated electron traps and breakdown                             |       |

| 6.1.3 Conclusion on positive charges and V <sub>TH</sub> instability                        |       |

| 6.2 Future work                                                                             |       |

|                                                                                             |       |

| References                                                                                  | 224   |

## **CHAPTER 1 INTRODUCTION**

#### **1.1 HISTORICAL EVOLUTION**

In 1947 W. Shockley, J. Bardeen and W.H. Brattain invented the bipolar transistor at Bell Laboratories, Murray Hill, New Jersey. The invention of the transistor, a solid-state amplifier, resulted in great efforts in the field of semiconductor devices. The integration of semiconductor devices on a single chip was one of the consequences of the combined efforts. J. Kilby at Texas Instruments first demonstrated the concept of Integrated Circuits (IC) in 1959.

This concept together with the fabrication of the first Metal Oxide Semiconductor Field Effect Transistor (MOSFET) by D. Kahng and M.M. Attala in 1960 provided the basis for the evolution of the microelectronics industry. Lilienfeld and Heil already proposed the principle of a surface field effect transistor in the early 1930's. The experimental verification of the surface field effect, however, could not be demonstrated for more than 30 years. As an interesting fact, the basic MOSFET structure and the principle of the operation, however, did not change.

In 1960s, Gordon Moore predicted that the number of transistors per chip wills double every 18-24 months. Since then, most of the research efforts have been spent on solving problems occurred when down-scaling the transistor sizes. Today, 90nm CMOS technology has been widely available and chips can have tens of millions of transistors. Although roadmap has been proposed to downscaling devices further in the foreseeable future, this will not be as straightforward as it was in the past. The difficulties encountered by the industry are summarized in the next section

#### **1.2 CHALLENGES FOR FURTHER DOWNSCALING**

They may be roughly divided into two groups:

**Problems due to a reduction in gate oxide thickness**: As the channel length shrinks, the gate oxide thickness must be reduced as well, to maintain the gate control. For the 90nm CMOS technology, the gate oxide has become as thin as 1.5nm. This leads to many difficulties, as listed below:

*The oxide reliability*: Time-Dependent Dielectric Breakdown (TDDB) is strongly dependent on the oxide thickness, as the operation voltage reduces for smaller MOSFETs, it is at a slower rate than the decrease of oxide thickness. This leads to an increase of oxide field strength and TDDB is a crucial issue for the current CMOS industry.

Hot-carrier effects in silicon: the avalanche multiplication, bombardment of SiON/Si interface, and hot-carrier injection into the oxide.

The mobility reduction: due to the high field perpendicular to the interface and defect creation. This leads to the degradation of the driving capabilities of the devices and the speed of the circuits.

When a MOSFET is in its off-state: the voltage drop between the gate and the drain over the thin gate dielectric gives rise a high field. This can cause electron tunneling from the valence band into the conduction band of silicon and form the gate-induced drain leakage current (GIDL).

*Power consumption*: because of the leakage current by tunneling through the gate oxide. For thin SiON, direct tunneling substantially increases the leakage current.

**Problems related to a reduction of channel length and doping**: The downscaling of channel length leads to a number of short channel effects, as described below:

The drain-induced-barrier-lowering (DIBL) effect: When a MOSFET is in its off-state, the bias applied on the drain can increasingly influence the source/body junction for smaller channel length. This lowers the potential barrier at the source/body junction and increases the leakage current. The threshold voltage reduction due to the charge-sharing effect.

The punch-through effect and the parasitic bipolar-transistor action (between source, bulk and drain): With reducing effective channel length the breakdown voltage reduces because the diffusion length of the minority carriers does not scale down.

*Threshold voltage variations*: Statistical variations increase with reduction of dimensions; we have to take care of the spatial tolerances and the variations in the dopant concentration.

The errors caused by ionized irradiation: With shrinking dimensions the total charge in devices reduces with a square law. Under some critical charge the error probability due to ionized irradiation increases rapidly. The ionization can be produced by the  $\alpha$ -particles from the chip-package or by the cosmic rays.

In addition, other important issues include polysilicon gate depletion, increasing resistances of the contacts and the interconnection lines, the isolation between the devices and between the devices and the substrate, as well as the latchup effect in CMOS circuits.

### **1.3 REQUIREMENTS OF HIGH-K GATE DIELECTRICS**

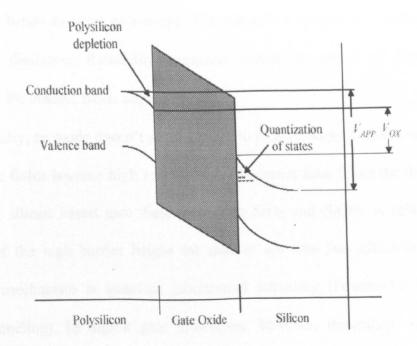

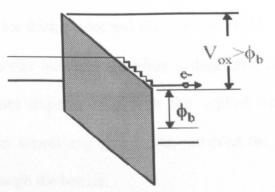

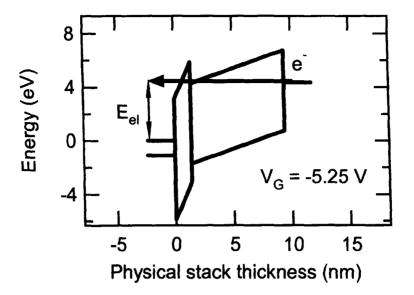

From the problems listed in the previous section, the primary aim of introducing high-k gate dielectrics is to reduce the leakage current. The main factors that determine the leakage current through an insulator are the barrier height and the physical thickness of the layer. To obtain low leakage currents in high-k dielectrics barrier heights of 1.5 eV or higher combined with a significantly higher dielectric constant compared to  $SiO_2$  are required. Theoretical calculations and experimental data show that significant benefit in gate leakage can be obtained for high-k dielectrics like  $Al_2O_3$ ,  $ZrO_2$  and  $HfO_2$ .

Fixed charge and threshold voltage control are another important aspect when considering high-k gate dielectrics. For a standard CMOS process, n-and p- degenerated poly-Si gate electrodes with work functions of 4 eV and 5 eV are used to control the threshold voltage,  $V_T$ , respectively. In MOS devices with high-k dielectrics and poly-Si electrodes  $V_T$  is often found to deviate significantly from the values measured in devices with a SiO<sub>2</sub> control oxide. The observed  $V_T$  shifts are commonly attributed to fixed charge in the dielectric either located at the interface or distributed throughout the film. In order to control  $V_T$  a low fixed charge (<10<sup>11</sup>cm<sup>-2</sup>) is of importance.

Achieving high carrier mobility is considered to be essential. Again,  $SiO_2$  devices serve as a baseline for devices with high-k materials. From literature it is known that most high-k devices suffer from severe mobility degradation. The cause for the degradation is still under debate. Scattering due to fixed charge in the dielectric or remote phonon scattering are proposed as origin for the mobility reduction. The experimental verification of the origin of the low carrier mobility, however, is still missing. In any case, control of fixed charge and understanding of the impact of remote phonons are essential for improving the carrier mobility in high-k devices.

Finally, reliability is considered as a further challenge for high-k materials. Initial experiments suggest that high gate reliability may be obtainable with these materials. However, detailed studies are required to investigate the impact of the atomic structure (amorphous versus crystalline), the interfacial layer, the stress polarity and the gate electrode on the reliability. Early learning is important to understand the reliability limitations of high-k gate dielectrics, which is the objective of this project.

#### **1.4 OUTLINE OF THE THESIS**

CHAPTER 2 INTRODUCES THE DIFFERENT TECHNIQUES TO CHARACTERIZE HIGH-K DIELECTRICS:

Some techniques used for classical SiO<sub>2</sub>-based dielectrics can also be applied to high-k dielectrics. However, due to the specific properties of high-k layers, dedicated measurement methodologies have been introduced recently. Early in the development of high-k gate stacks it was found that they suffer from rather large DC hysteresis and threshold voltage instability effects [YoungC05]. Indeed, it was found that, when combined with a poly-Si gate, the dielectric stack exhibits a defect band of bulk traps that can very efficiently trap electrons. This causes hysteresis in the C-V curve and transistor characteristics. Furthermore, the charge trapping also affects the extraction of important transistor parameters like transconductance, mobility, and threshold voltage.

In this project, various measurement methods, such as Pulsed  $I_D$ -V<sub>G</sub>, Charge Pumping (CP), and Time Dependent Dielectric Breakdown (TDDB) will be modified and used to study these defects and V<sub>T</sub>-instabilities. The details will be given in chapter 2.

#### **CHAPTER 3 CHARACTERIZES AS GROWN ELECTRON TRAPS:**

When SiON is replace by HfO<sub>2</sub>, the presence of as-grown electron traps becomes important as they can induce threshold voltage instability by electron trapping, reduce electron mobility through coulombic scattering [Groes04], [Degra04] and resulting in early breakdown by forming conduction path and reduce the yield substantially [Groes04], [Degra04] [Degra03]. In this chapter as grown electron traps are systematically studied. Their properties and dynamic behaviour in HfO<sub>2</sub>/SiO<sub>2</sub> stacks are carefully analyzed, based on the measurements techniques given in Chapter 2.

After selecting test conditions to ensure that the energy level of filling electrons was above the energy level of traps and measurement time was sufficiently fast that detrapping is negligible and using samples with a progressive reduction of  $HfO_2$  thickness, it is ruled out that the traps are piled up at the  $HfO_2/SiO_2$  interface. A uniform distribution throughout  $HfO_2$  layer does not agree with the test data, either. The results support that there are trapping-free regions around 1.3~1.8nm near to either  $HfO_2/SiO_2$  or gate/ $HfO_2$

The determination of trap capture cross section is carried out by evaluating the gate current and the electron fluency for filling the trap. This is achieved by a numerical simulation to estimate the trapping-induced transient gate current following the application of a pulse to the gate. It is found that trapping can reduce the gate current by two orders of magnitude and the gate current can drop substantially within microseconds. The results show the presence of two distinctive capture cross sections in the order of 10<sup>-14</sup> cm<sup>2</sup> and 10<sup>-16</sup> cm<sup>2</sup>, respectively, which most likely originate from two different types of as-grown electron traps in HfO<sub>2</sub>. These capture cross sections are insensitive to fabrication and processing techniques.

### CHAPTER 4 INVESTIGATES THE GENERATION OF ELECTRON TRAPS AND TIME DEPENDENT DIELECTRIC BREAKDOWN (TDDB):

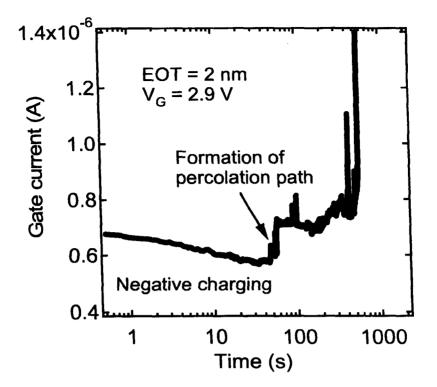

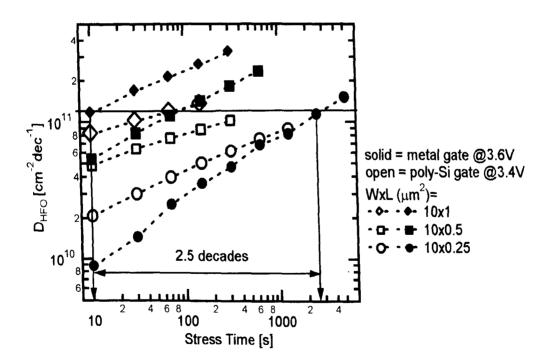

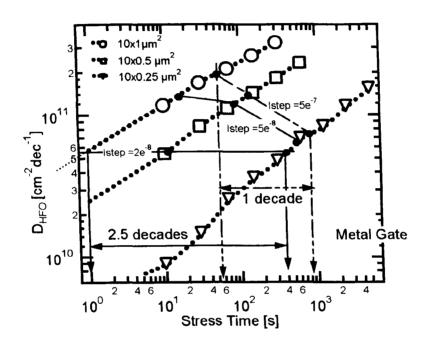

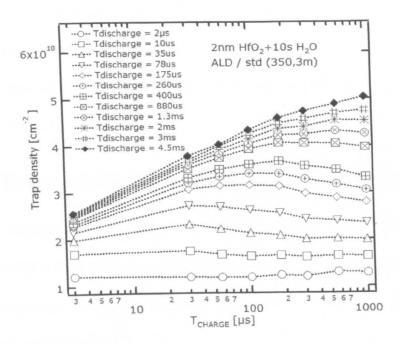

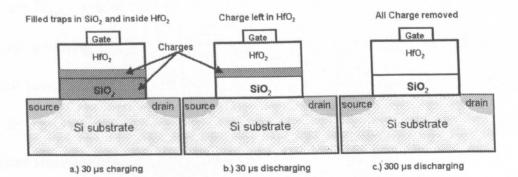

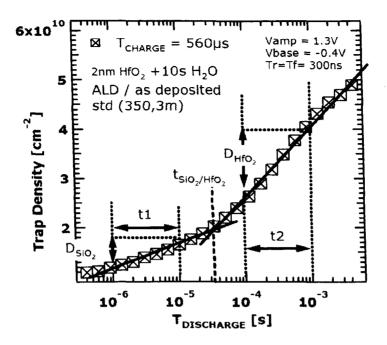

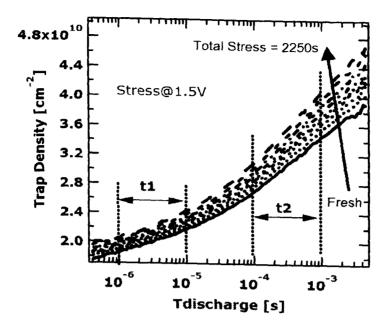

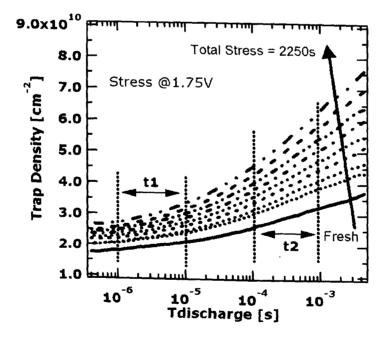

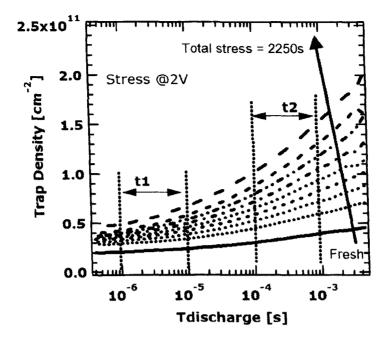

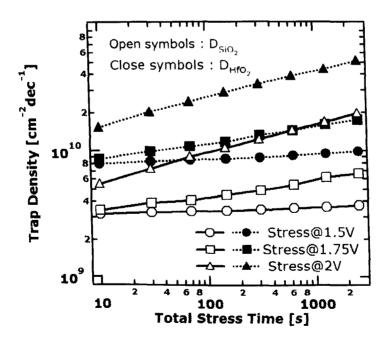

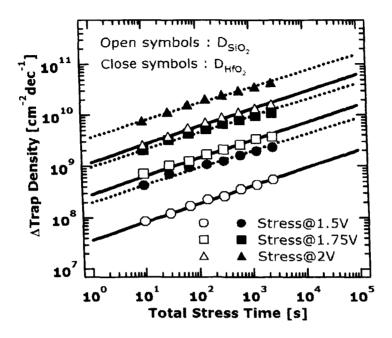

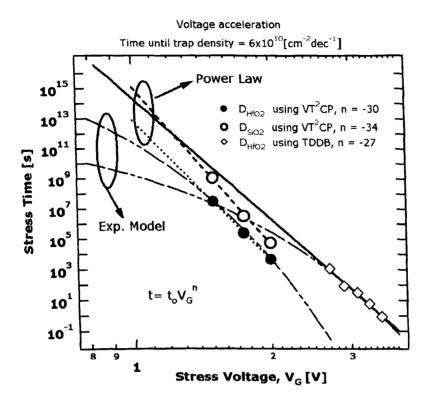

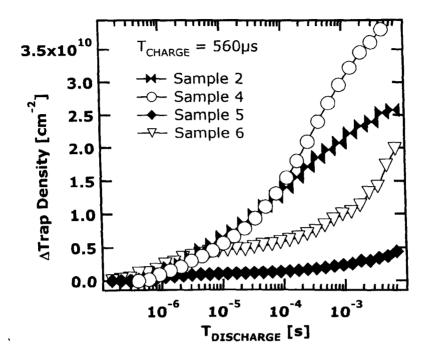

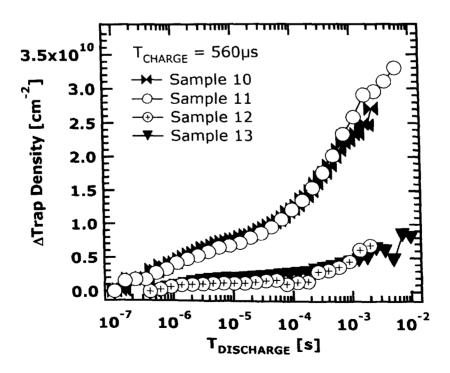

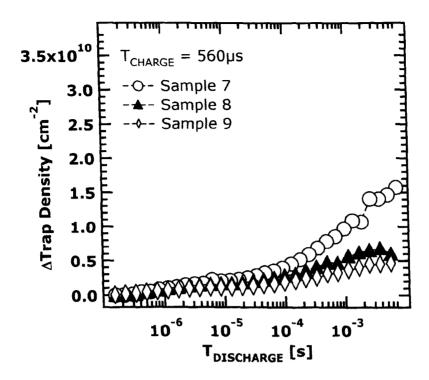

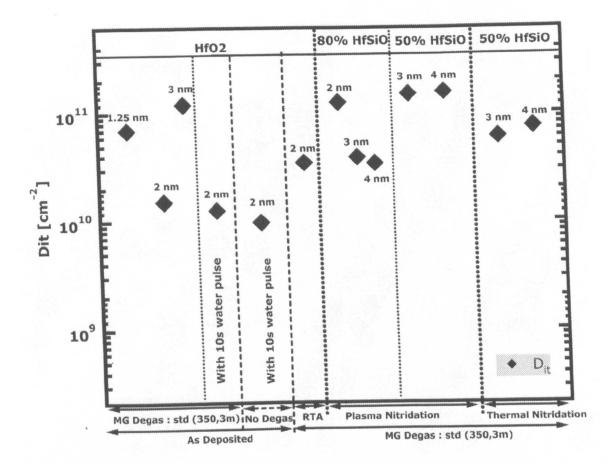

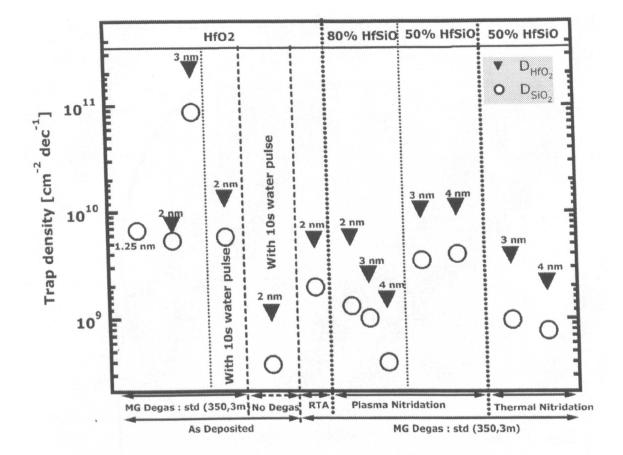

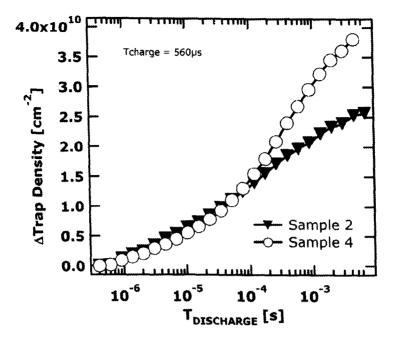

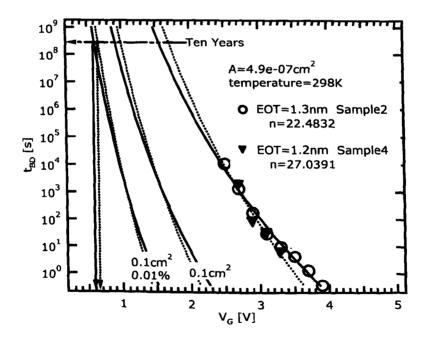

Charge pumping techniques introduce in chapter 2 will be used to investigate the generation of electron traps in SiO<sub>2</sub>/HfO<sub>2</sub> stacks. Specifically, the variable frequency charge pumping will be used to investigate the bulk trap density on both fresh and degraded device with different gate electrodes and an investigation on why time-to breakdown ( $t_{BD}$ ) depends on the channel length will be given. The variable  $t_{charge}$   $t_{discharge}$  charge pumping (VT<sup>2</sup>CP) is found to be more suitable than the variable frequency charge pumping to investigate the states in the interfacial layer and the bulk states at very low frequency (~90 Hz). It is able to clearly separate the traps in the interfacial SiO<sub>2</sub> from the traps in the HfO<sub>2</sub> and observe the creation of new traps in both constituent layers. During degradation at a constant positive voltage, the increase of traps, both in the SiO<sub>2</sub> as well as in the HfO<sub>2</sub>, follows a power law behavior as a function of time with an exponent ~0.32-0.34. The voltage acceleration of creation of HfO<sub>2</sub> traps matches that of the TDDB

The  $VT^2CP$  will be used to compare traps in high-k layers of different  $HfO_2$  thickness, different % Hf in HfSiO, various Post Deposition Anneal (PDA), and different plasma and thermal nitridation.

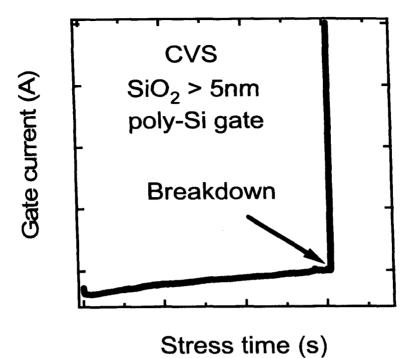

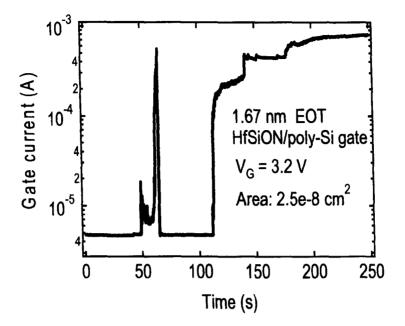

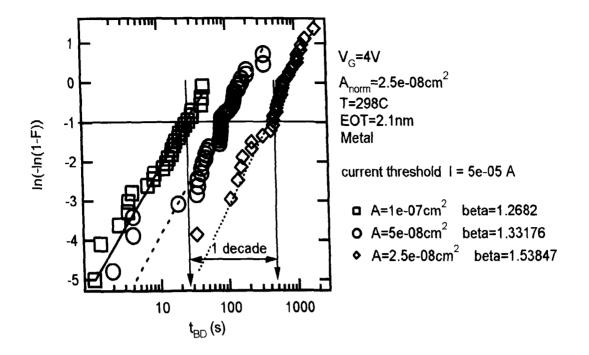

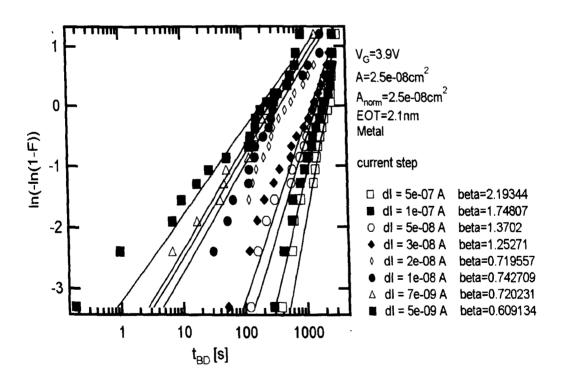

Furthermore, TDDB tests are carried out. TDDB shows that when poly-Si gate is replaced with a metal gate, and TDDB lifetime is consistently limited by an abrupt large current increase of several hundred  $\mu A$ . The occurrence of those large  $\Delta I$  is a potential limitation for the reliability of metal gate devices.

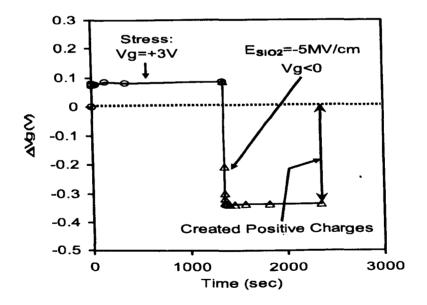

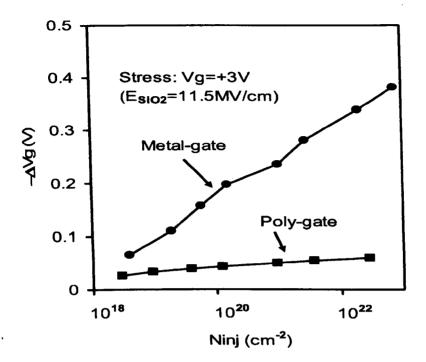

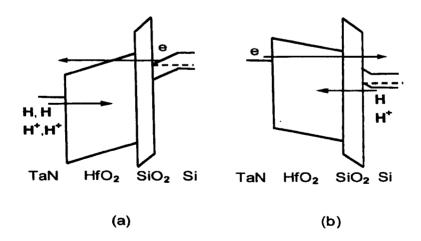

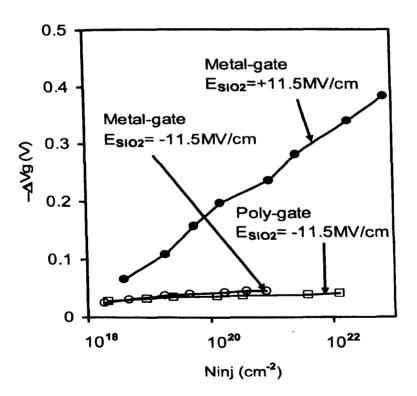

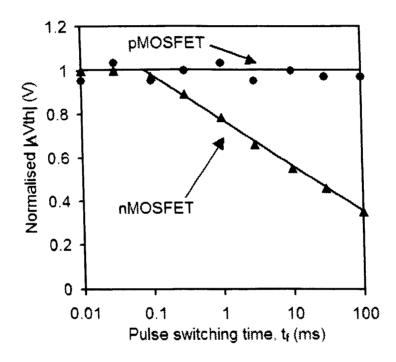

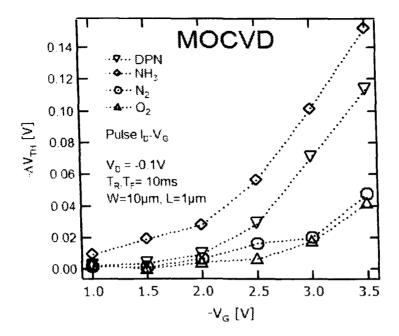

### CHAPTER 5 FOCUSES ON POSITIVE CHARGE GENERATION AND V<sub>TH</sub> Instabilities On NMOSFETS And PMOSFETS

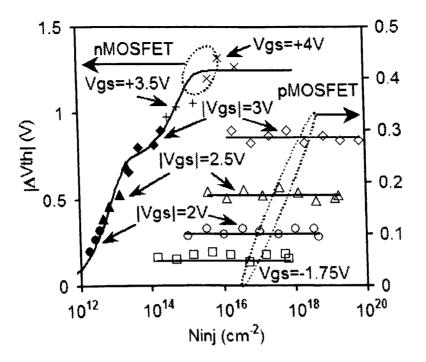

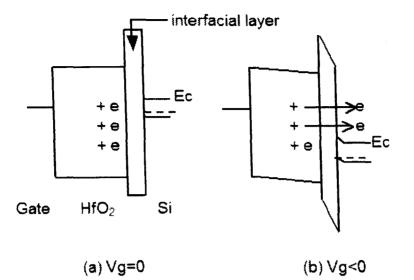

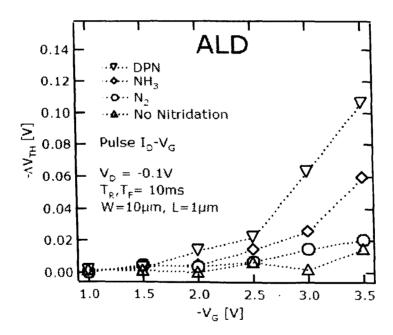

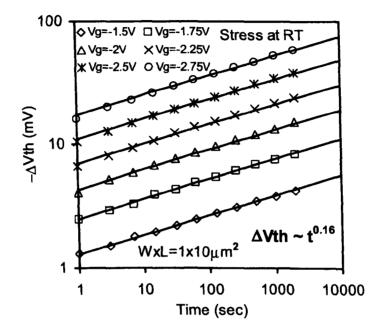

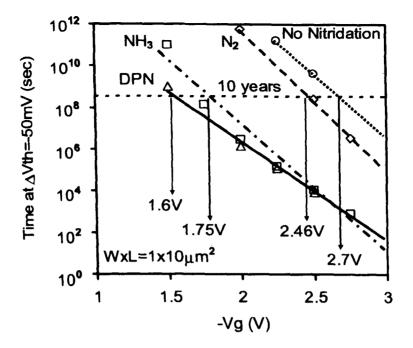

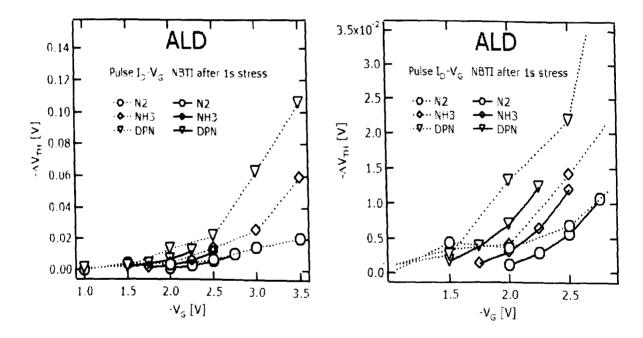

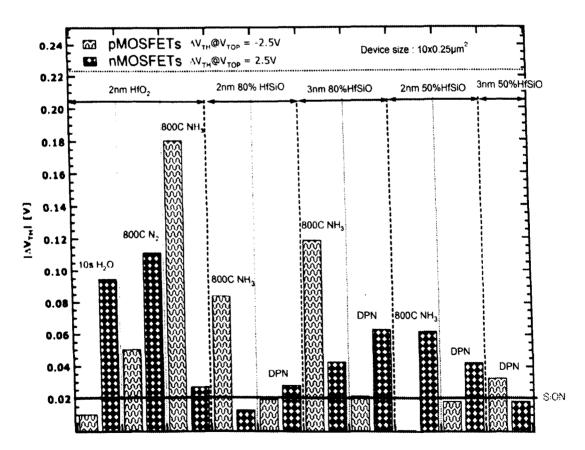

The use of metal gates removes gate depletion, allows aggressive downscaling of equivalent oxide thickness. In this chapter it is demonstrated that changing poly-si gate to metal gate (TaN) affects the positive charge formation in HfO<sub>2</sub>/SiO<sub>2</sub> stacks. Under positive gate bias stresses, the results show that positive charge formation in metal-gated samples is significantly higher than in poly-si gated samples. However, positive charge formation is similar in these two types of samples, when stressed under negative gate bias. The results are explained by assuming that there are more hydrogenous species at the metal/dielectric interface and the hydrogen release from the anode dominates the positive charge formation. The behaviour of positive charges in the stack is also compared with that in a single SiO<sub>2</sub> layer. When compared with nMOSFETs, the V<sub>TH</sub> instability of pMOSFETs using Hf-silicates for sub-2nm nitrided layer is shown to be insensitive to measurement time, does not saturate as stress voltage increases and is not controlled by carrier fluency. Impacts of different process conditions, such as plasma nitridation, thermal nitridation, HfO<sub>2</sub> thickness and Hf content, is carried out. The results show that  $NH_3$  nitridation can give more  $V_{TH}$ instability for pMOSFETS than nMOSFETs with high Hf-content (80%) but similar or less with 50% Hf-content and can reduce the operation voltage by 1V. Also it is shown that nitridation introduces two different types of defects, resulting in two types of instabilities with distinctive characteristics.

#### **CHAPTER 6 CONCLUDES THE NEW FINDINGS AND DISCUSSES THE FUTURE WORK.**

#### **1.4 OUTLINE OF THE THESIS**

22

# CHAPTER 2 CHARACTERIZATION TECHNIQUES FOR HIGH-K DIELECTRICS

Charge trapping in conventional SiO<sub>2</sub> gate dielectrics is commonly studied using either hysteresis measurements or 'stress and sense' techniques. In the past, the same methodology was also been applied to study charge trapping in high-k dielectrics. In a recent study it has been demonstrated that transient charging effects in high-k materials (e.g. HfO<sub>2</sub>) make a reliable assessment of the charge trapping more complicated than in SiO<sub>2</sub>. Therefore fast measurement techniques have been developed to capture the fast transient effects previously not reported. **[Ker04]**, **[Ker03]**, **[Cart04]**, **[Gus04]**. In this chapter, different techniques used for the characterization of high-k dielectrics will be described. In this chapter we will discuss on the different techniques available for the characterization of high-k dielectrics. Conventional, pulsed and advanced techniques will be described also the test condition to calculate the capture cross section will be given.

### **2.1 CONVENTIONAL TECHNIQUES**

In a conventional hysteresis measurement a quasi DC ramp is applied to the MOS device using ramp rates ranging from 0.1V/s to 10V/s. Charge trapping is monitored either using the  $I_D-V_G$  or the Capacitance-Voltage characteristic. In both cases, when charge trapping / detrapping is present, the initial trace will deviate from the final trace due to build up or loss of charges. Fast transient effects, however, are not captured by the conventional hysteresis measurement due to the inherently slow ramp

rates. A schematic drawing of the gate voltage during a hysteresis measurement is shown in Fig. 2.1. [Ker04], [Ker03], [Cart04], [Gus04]

#### 2.1.1 Conventional C-V

The C-V hysteresis measurement provides a fast screening method with respect to instabilities in MOS devices. Additional information on the voltage dependence of the instability can be obtained when the conventional hysteresis measurement is extended using a bias sequence as shown in Fig. 2.1. Furthermore, the use of multiple traces should also allow to address the reversibility of the observed effects. [Cart04], [Gus04]

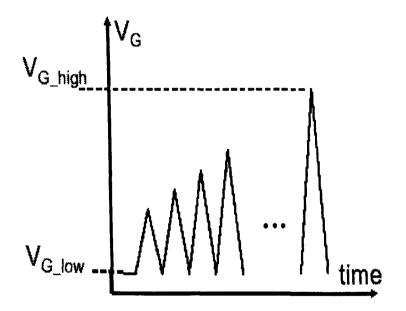

Fig.2.1 Schematic drawing of the gate bias during a hysteresis measurement applied to n-channel MOSFETs. An appropriate negative gate bias ( $V_G$  -low) is chosen to allow for complete discharging, whereas the high level of the gate bias ( $V_G$  -high) is continuously increased to monitor charge trapping in inversion [Ker03], [Cart04]

Previous works shows [Ker03], [Cart04] when the gate bias is swept from negative to positive identical C-V traces are obtained. From this it could be concluded that the gate stack does not suffer from instability. However, when the sweep direction

is reversed from positive to negative the instability become evident depending on the maximum gate bias, C-V shifts of  $\sim 100$ mV and more can easily be measured. When the device is swept further into accumulation (negative gate bias) the C-V trace merge again indicating that the instability completely recovers. The major drawback of the C-V hysteresis or the multiple C-V trace technique is the poor control over the amount of injected charge during such an experiment. Therefore the magnitude of the measured instability can significantly vary depending on the ramp rates of the sweep.

#### 2.1.2 Conventional In ~VG

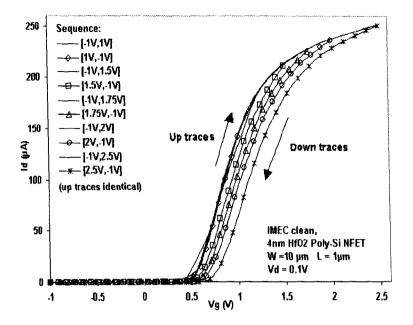

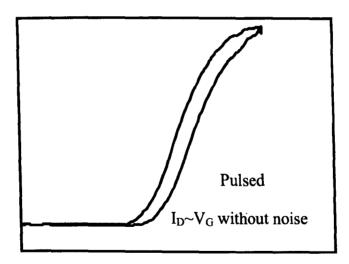

A complementary technique to the C-V hysteresis measurement is the use of multiple  $I_D$ -V<sub>G</sub> traces on MOSFETs. Again sequences of sweeps are taken starting from accumulation, a negative bias for n-channel devices or a positive gate bias for p-channel devices, and sweeping the MOSFET towards inversion successively increasing the maximum voltage. In this case the transfer characteristic is used to monitor the instability as shown in Fig.2.2.

Using this technique a shift of ~100mV and more in the  $I_D$ ~V<sub>G</sub> characteristic can easily be detected depending on the maximum positive gate bias applied to the gate. The use of the linear  $I_D$ ~V<sub>G</sub> characteristic to monitor the instability also allows to study the recovery during the down ramp of the sweep. When going to large positive gate biases, where larger shifts are observed, a stretch-out on the reverse trace is evident. This indicates that a fraction of the instability already dynamically recovers when the high gate bias is reduced.

Fig.2.2  $I_D \sim V_G$  sweeps sequence from accumulation to inversion using conventional technique to monitor instability for n-channel MOSFET.A large shift could be observed when sweep to high voltage.

The use of the conventional  $I_D \sim V_G$  characteristic limits the monitoring capability to the operation mode of the MOS transistor, which is anyway the focus of interest from application point of view. In the case of  $I_D \sim V_G$  instabilities, when applying a sufficient negative gate bias complete recovery are also obtained. [Cart03]

#### 2.1.3 Stress and sense

A further procedure, which was used extensively in the literature to study the instabilities in conventional  $SiO_2$  based gate dielectrics, is known as "stress and sense" method.

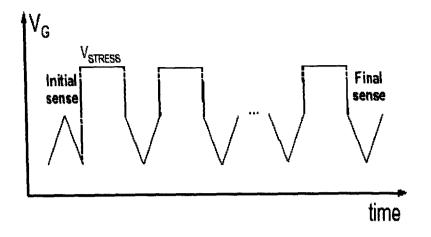

Fig.2.3 Schematic drawing of a "stress and sense" experiment. The stress applied to the device is periodically interrupted to sense the charge state by comparing the  $V_{FB}$  or  $V_T$  to the initial trace.

In this case, first an initial sense measurement is carried out prior to stressing the devices. The stress is then interrupted periodically and a sense measurement is performed. A schematic drawing of the bias sequence in the conventional stress and sense procedure is shown in Fig. 2.3. [ZhaoY]

The instability of the device is extracted by comparing the sense measurement after stress with the initial device characteristic. Predictions to operation conditions are usually made when combining the time dependence with the voltage dependence of the instability. One of the known issues of the "stress and sense" procedure is the inherent time delay between stressing and sensing. In case some recovery of the instability occurs at time periods of the order of ~10 to 100 ms this procedure will not capture its full extent. Furthermore, the selection of the sense condition requires special attention. In any case, the use of this procedure will help to understand the stability of MOSFETs with high-k gate dielectrics.

27

#### **2.2 TIMES RESOLVED TECHNIQUES**

As briefly mentioned in the previous section due to the presence of fast recovery of the instabilities measurement techniques significantly faster than the semiconductor parameter analyzers are required for a correct quantification. Therefore, alternative techniques were introduced which will be discussed in the following section and some of them will be extensively applied to high-k gate stacks in this project.

#### 2.2.1 Pulsed C-V

The pulsed C-V technique is similar to the quasi-static C-V measurement using a linear voltage ramp [Nico82]. A linear voltage ramp is applied to the Device Under Test (DUT) while the capacitor displacement current is recorded using a current meter. The CV characteristic can be readily obtained from the voltage and current values, as it will be explained further below.

In conventional quasi-static measurement often the DUT consists of an MOS capacitor that has no means to provide minority carriers. As a consequence, non-equilibrium carrier concentrations can exist within the device for time spans well above 100µs. Therefore, typical quasi-static CV measurements use a voltage ramp rate well below 1 V/s. The pulsed CV technique employs DUTs that feature a pn-junction at the perimeter of the gate electrode to provide minority carriers. Hence, fast ramp rates of 1kV/s and above can employed without pulling the MOS capacitor out of equilibrium. The resulting CV characteristic is identical to that obtained from a conventional high-frequency CV measurement.

The pulsed CV technique has been used by Weinberg and Fischetti [Wein86] in a study of the SiO<sub>2</sub>- induced substrate current in field-effect transistors. A fast ramp rate in the order of 1kV/s has been used to capture  $V_{FB}$  shifts immediately after application of stress pulse. A similar set-up has been used by Agarwal et al. [Agar02] to study charge transport, however using a slow ramp rate below 1V/s.

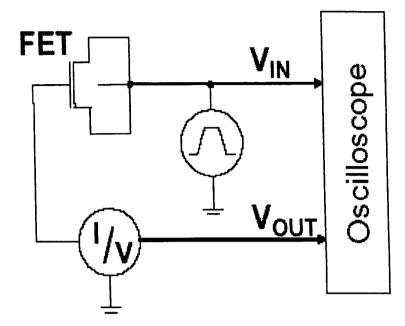

Fig.2.4 Schematic setup used to obtain pulsed C-V characteristics. The voltage pulse applied to the source, drain and substrate  $(V_{IN})$  is recorded using a digital oscilloscope together with the output voltage  $(V_{OUT})$  of the current-voltage amplifier.[Ker03A]

In this pulsed CV technique (Fig.2.4) the ramp rates can vary from ~ 0.1V/s to >10 kV/s and as a result the corresponding displacement current is several orders of magnitude higher than in the conventional quasi static C-V measurement. The displacement current is converted into a voltage trace using a current-voltage amplifier and recorded with a digital oscilloscope. The voltage ramp with fixed ramp rate is provided at the edges of a pulse. From the voltage trace the C-V characteristic can be extracted using the equation 2.1 [Ker03A]

$$C(V_{IN}) = \frac{V_{OUT} - V_{OFFSET}}{Z_{AMP} \cdot dV/dt}$$

(2.1)

Where dV/dt is the voltage ramp,  $V_{OFFSET}$  is the offset voltage of the current-voltage amplifier and  $Z_{AMP}$  the current-voltage gain. The input ( $V_{IN}$ ) and output ( $V_{OUT}$ )

#### 2.2 TIMES RESOLVED TECHNIQUES

voltage correspond to the terminals of the circuit as illustrated in the schematic measurement setup shown in Fig. 2.4.

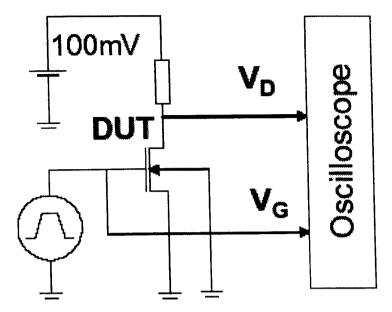

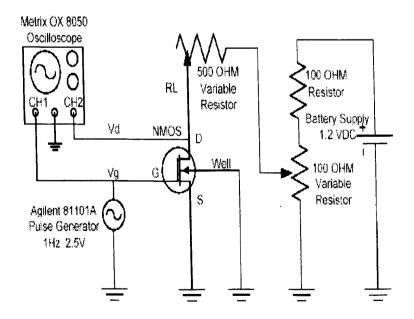

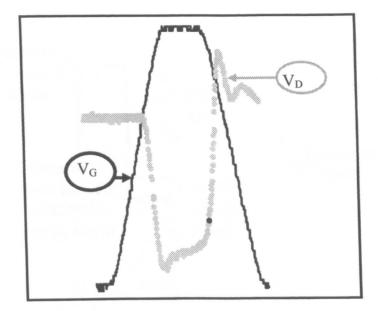

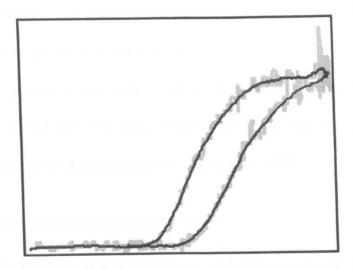

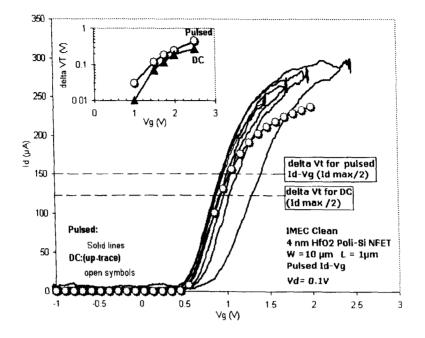

### 2.2.2 Pulsed Ip~VG

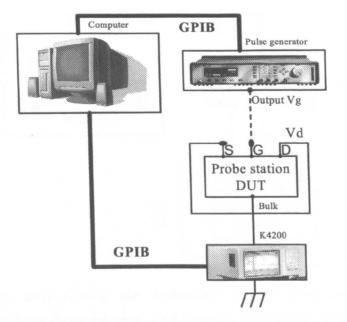

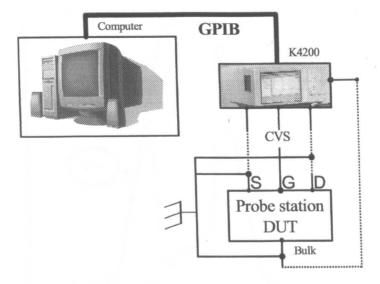

The pulsed  $I_{D}$ -V<sub>G</sub> measurement technique uses a pulse generator to provide a pulse with sloped edges. During the pulse edge, the current that flows through the transistor is monitored. Using a sampling oscilloscope, both the pulse bias and transistor current are recorded, which allows for the determination of the  $I_{D}$ -V<sub>G</sub> characteristics. The technique allows for determination of the V<sub>T</sub> immediately after application of a pulse by capturing the  $I_{D}$ -V<sub>G</sub> during the returning edge of the stress pulse. This short read delay time is essential for determining the fast initial charge loss in charge trapping devices. Details of the instruments and technical overview is given in the section 2.7.The set-up for pulsed  $I_{D}$ -V<sub>G</sub> measurements is obtained by a slight modification of the set-up for pulsed CV. Figure 2.5 shows the schematic of the set up and Figure 2.6 the V<sub>G</sub>-t and V<sub>D</sub>-t traces recorded by the oscilloscope.

The major advantage of this technique over the pulsed C-V method is the reduced sensitivity to the parasitic gate leakage current. Unless the  $I_D \sim V_G$  characteristic is distorted by the leakage current, this procedure can be used to monitor  $V_T$  shifts in the  $\mu$ s time range. [Ker03], [Cart04]

Fig.2.5 Schematic of setup used for pulsed  $I_D \sim V_G$  measurements. The FET is used in an inverter circuit with a resistive load ( $R_L$ ). From the voltage - time traces ( $V_G$  (t),  $V_D$  (t)) the  $I_D \sim V_G$  characteristic is extracted.

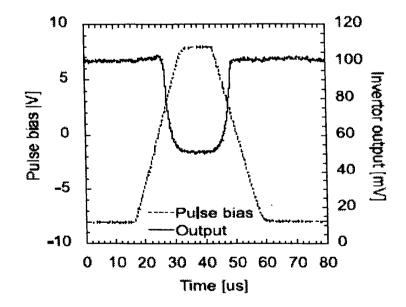

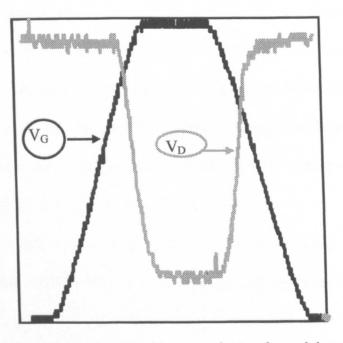

Fig.2.6 The  $V_{G}$ -t and  $V_{D}$ -t traces recorded by the oscilloscope.

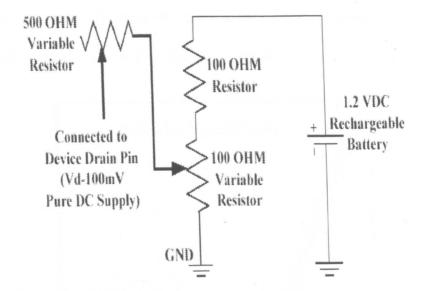

In the setup in Fig 2.5, the MOSFET is used in an inverter circuit with a resistive load ( $R_L$ ). A small DC bias is applied to the resistor, which acts together with the channel resistor as a voltage divider. The  $I_D \sim V_G$  characteristic is obtained by applying a trapezoidal (triangular) pulse to the gate and recording the drain voltage using a digital oscilloscope as shown in Fig 2.6. From the measured voltage traces the  $I_D \sim V_G$ characteristic can be constructed using the Eq. 2.2

$$I_{\rm D} = \frac{100 \text{mV}}{\text{V}_{\rm D}} \left( \frac{100 \text{mV} - \text{V}_{\rm D}}{\text{R}_{\rm L}} \right)$$

(2.2)

where  $V_D$  is the measured drain voltage and  $R_L$  the resistive load of the inverter **[Ker03]**. Due to the use of a voltage divider the drain voltage dynamically changes during the measurement. However, this effect can simply be eliminated by normalizing the extracted drain current to a constant drain voltage, which is given by the term  $100 \text{mV}/V_D$  in Eq. 2.2.

Fig.2.7 Schematic drawing of measurement setup used for pulsed  $I_D \sim V_G$  experiment in the  $\mu s$  range slightly different to the one presented in literature and in Fig.2.5.

It is noted that this normalization is only correct, when the MOSFET is operated in the linear regime, which limits the range for the DC bias applied to the resistor **[Ker03B]**, **[Cart04]**. The derivation of Eq. (2.2) is given in section 2.3.1. When replacing the resistor with a current-voltage amplifier connected to the source terminal this problem can be circumvented and a constant bias can directly be applied to the drain terminal of the device.

In the work presented in chapters 3 and 5, the pulsed  $I_D \sim V_G$  was modified to the schematic setup shown in Fig. 2.7 by adding a voltage divider to apply a small DC bias (100mV) to the drain instead of using a power supply. This change is explained in more details in section 2.6.

### 2.3 FORMULAE FOR PULSED ID~VG TECHNIQUE

#### 2.3.1 Normalization of drain current

For the conventional DC measurement, the drain bias,  $V_D$ , is fixed at the supply voltage,  $V_D=V_{DD}$ . The I<sub>D</sub> equation is:

$$I_{D} = \frac{C_{OX} \mu_{n} W}{L} \left[ (V_{G} - V_{T}) V_{DD} - \frac{1}{2} V_{DD}^{2} \right] \approx \beta (V_{G} - V_{T}) V_{DD}$$

(2.3)

where

$$\beta = \frac{C_{OX} \ \mu_n W}{L} \tag{2.4}$$

For Pulsed  $I_D \sim V_G$ , the existence of the resistor,  $R_L$ , connected to the drain in Figs. 2.5 and 2.7 results in  $V_D < V_{DD}$ , when the MOSFET is switched on. The measured drain current,  $I_{Dm}$ , is:

$$I_{Dm} = \frac{V_{DD} - V_{D}}{R_{L}}$$

(2.5)

and

#### 2.2 TIMES RESOLVED TECHNIQUES

33

$$I_{Dm} = \beta (V_G - V_T) V_D$$

<sup>(2.6)</sup>

To find the drain current at a  $V_{DD}$ , the measured drain current,  $I_{Dm}$ , must be normalized. From Eq.(2.3), one has,

$$\beta \left( V_G - V_T \right) = \frac{I_D}{V_{DD}}$$

(2.7)

Substituting Eqs.(2.5) and (2.7) into the left and right hand side of Eq. (2.6), one can obtain,

$$I_{D} = \frac{V_{DD}}{V_{D}} \left( \frac{V_{DD} - V_{D}}{R_{L}} \right)$$

(2.8)

Typically,  $V_{DD}$  is set at 100mV and Eq. (2.8) is the same as Eq. (2.2).

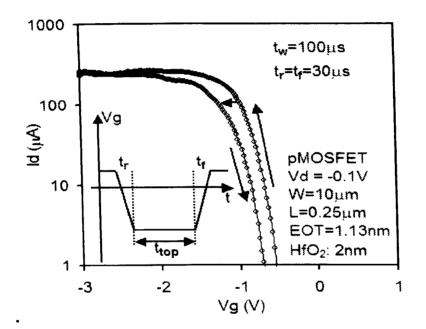

### 2.3.2 Typical test pulse and $I_{\rm D}\text{--}V_{\rm G}$

In this section the typical test gate pulse and the resultant  $I_D$ -V<sub>G</sub> will be presented. They are used to calculate the capture cross section in chapter 3. As mentioned earlier, to extract the capture cross section, detrapping should be suppressed. This requires using the pulsed  $I_D$ ~V<sub>G</sub> technique.

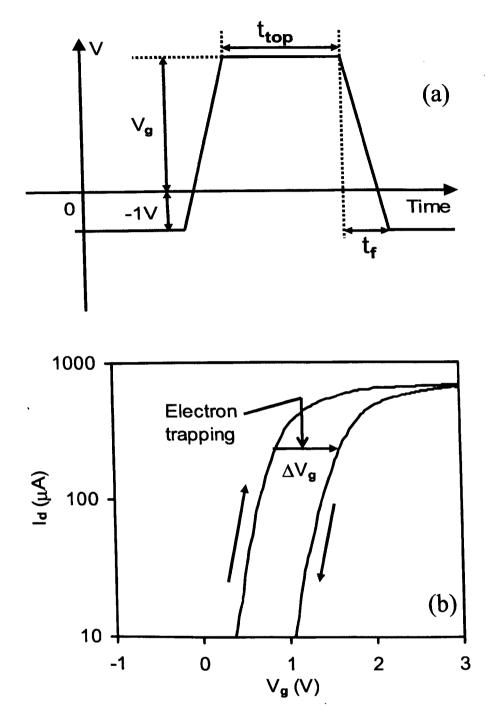

Fig.2.8a shows the typical pulse applied to the gate. A -1V was first applied for a sufficiently long time (~1sec) to 'reset' the sample by emptying traps through detrapping. During the rising edge of the pulse, drain current was monitored to give the  $I_D \sim V_G$  curve on the left in Fig.2.8b. Traps were filled with electrons during the period of 't<sub>top</sub>'. The negative trapped charges lead to a positive shift of the  $I_D \sim V_G$  during the falling edge of the pulse, as shown by the curve on the right in Fig.2.8b. The trapping level is measured from this shift,  $\Delta V_G$ . The measurement time is within the falling period,  $t_f$ , and their impacts on the result will be evaluated in chapter 3 section 3.4.4.

Fig.2.8 The pulse applied to the gate (a) and the pulsed transfer characteristics (b). A -1V was first applied to the gate to empty any trapped electrons. During the rising edge of the pulse, trapping is negligible and the corresponding  $I_D \sim V_G$  is the left curve in (b). Traps were filled during the period of  $t_{top}$ . This leads to a shift of gate bias,  $\Delta V_G$ , when the  $I_D \sim V_G$  was measured again during the falling edge of the pulse. The delay between trap filling and measurement is less than the falling time,  $t_f$

#### 2.3.3 Calculation of the electron fluency

To evaluate the capture cross section of electron traps, one must know the number of electrons injected from the substrate into the gate dielectric. The formulae used in Chapter 3, Eq.(3.1), is

$$N_{im} = J_{gm} \times t_{top}/q + \Delta V_G \times C_{ox}/q.$$

(3.1)

There has been some confusion on whether the  $2^{nd}$  term should be included in the above formulae. In this section, details will be given on how this equation is derived.

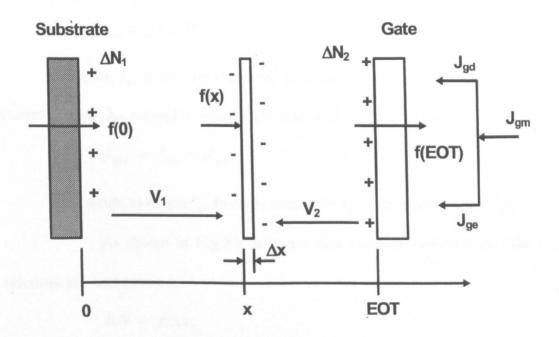

Since Eq.(3.1) is applicable for both a single layer and a stack of dielectrics, to simplify the derivation, the dielectric stack is considered as a single layer of  $SiO_2$  with a thickness of EOT. As illustrated in Fig.2.9.

Fig.2.9 A schematic illustrations of electron injection, trapping, and the relevant current components used for calculating electron fluency.

If we define f(x) as the number of electrons passing through a unit area per unit time at a distance of 'x' from the substrate/dielectric interface, the electron conservation equation is,

$$\frac{\partial f}{\partial x} = -\frac{\partial \rho}{\partial t}$$

where  $\rho$  is the number of trapped electrons per unit volume. An integration against 'x' leads to,

$$f(0) = f(EOT) + \int_{0}^{EOT} \frac{\partial \rho}{\partial t} dx.$$

(2.9)

The second term on the right hand side represents the loss of electrons through trapping in dielectric. By definition,  $N_{im}$  is related to f(0) through,

$$N_{im} = \int_{0}^{t} f(0) dt .$$

(2.10)

The current density caused by electron flowing through the gate/dielectric interface,  $J_{ge}$ , is related to f(EOT) by,

$$J_{ge} = qf(EOT). \tag{2.11}$$

However,  $J_{ge}$  is not the measured gate current density  $J_{gm}$ , since displacement current density,  $J_{gd}$ , caused by charge trapping, also contributes to  $J_{gm}$ ,

$$J_{gm} = J_{ge} + J_{gd} . (2.12)$$

As a result, to obtain  $J_{ge}$  from the measured  $J_{gm}$ , one must evaluate  $J_{gd}$ .

As shown in Fig.2.9, within a thin layer of dielectric,  $\Delta x$ , the trapped electrons per unit area are,

$$\Delta N = \rho \Delta x \,. \tag{2.13}$$

The  $\Delta N$  induces a positive charge of  $\Delta N_1$  at the substrate interface and  $\Delta N_2$  at the gate interface with,

$$\Delta N = \Delta N_1 + \Delta N_2 \,. \tag{2.14}$$

The corresponding potential drop between the substrate and the layer at 'x' is,

$$V_1 = \frac{q\Delta N_1 x}{\varepsilon_0 \varepsilon_{SiO2}},\tag{2.15}$$

### 2.3 FORMULAE FOR PULSED $I_{\rm D} \sim V_{\rm G}$ Technique 37

and similarly,

$$V_2 = \frac{q\Delta N_2 (EOT - x)}{\varepsilon_0 \varepsilon_{SiO2}}.$$

(2.16)

Since the test is carried out with a constant voltage over the dielectric, it requires,

$$V_1 = V_2$$

. (2.17)

Solving Eq. (2.14-2.17), we have,

$$\Delta N_{2} = \frac{x}{EOT} \Delta N$$

$$= \frac{x}{EOT} \rho \Delta x. \qquad (2.18)$$

Integrating Eq. (2.18), the total trapping induced positive charges on the gate is,

$$N_g = \int_0^{EOT} \frac{x}{EOT} \rho dx . \qquad (2.19)$$

The displacement current is,

•

$$J_{gd} = q \frac{\partial N_g}{\partial t}$$

=  $q \frac{\partial}{\partial t} \left( \int_{0}^{EOT} \frac{x}{EOT} \rho dx \right).$  (2.20)

By using Eqs. (2.11), (2.12) and (2.20), the f(EOT) can now be evaluated through,

$$f(EOT) = \frac{1}{q} (J_{gm} - J_{gd})$$

$$= \frac{J_{gm}}{q} - \frac{\partial}{\partial t} (\int_{0}^{EOT} \frac{x}{EOT} \rho dx).$$

(2.21)

From Eq. (2.9), we have,

$$f(0) = f(EOT) + \int_{0}^{EOT} \frac{\partial \rho}{\partial t} dx$$

$$= \frac{J_{gm}}{q} - \frac{\partial}{\partial t} \left( \int_{0}^{EOT} \frac{x}{EOT} \rho dx \right) + \int_{0}^{EOT} \frac{\partial \rho}{\partial t} dx$$

$$= \frac{J_{gm}}{q} + \frac{\partial}{\partial t} \left[ \int_{0}^{EOT} (1 - \frac{x}{EOT}) \rho dx \right].$$

(2.22)

Using Eq. (2.10), the electron fluency at the substrate/dielectric interface is,

$$N_{im} = \int_{0}^{t} f(0) dt$$

=  $\frac{1}{q} \int_{0}^{t} J_{gm} dt + \int_{0}^{EOT} (1 - \frac{x}{EOT}) \rho dx$ . (2.23)

For a fixed drain current, the trapping induced gate voltage shift is,

$$\Delta V_g = \frac{q}{C_{ox}} \int_{0}^{EOT} (1 - \frac{x}{EOT}) \rho dx . \qquad (2.24)$$

Combining Eqs. (2.23) and (2.24), we have,

$$N_{im} = \frac{1}{q} \int_{0}^{t} J_{gm} dt + \frac{\Delta V_g C_{ox}}{q}.$$

(2.25)

If one assumes  $J_{gm}$  is a constant over a period of  $t_{top}$ , Eq. (2.25) becomes the Eq.(3.1),

$$N_{im} = J_{gm} \times t_{top}/q + \Delta V_g \times C_{ox}/q.$$

(3.1)

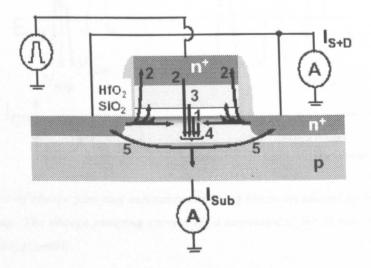

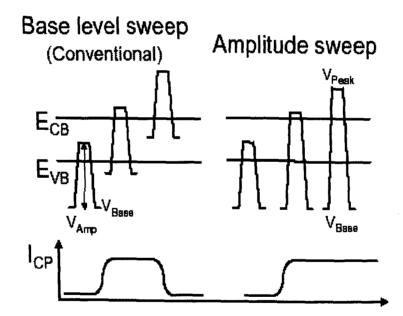

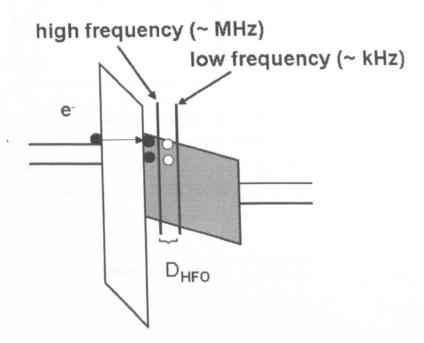

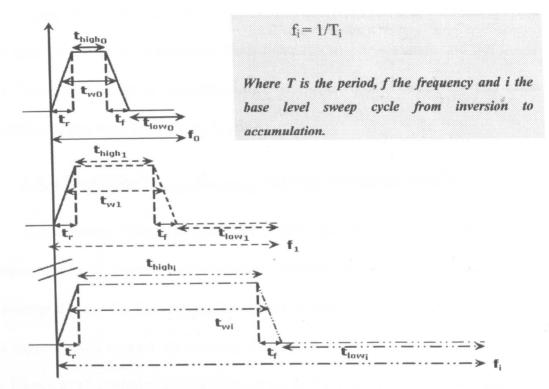

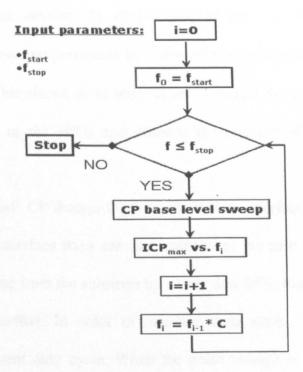

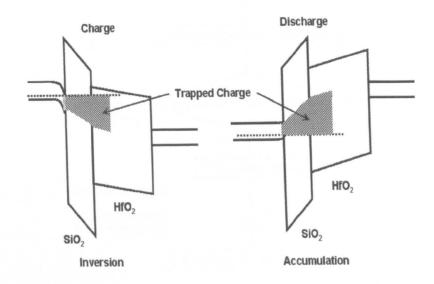

# 2.4 CHARGE PUMPING (CP)

Charge pumping (CP) is a transient effect in MOS devices. It represents the transfer of charge from the source and drain terminals to the bulk by transient pulses at the terminals. A DC component of the terminal currents can be measured. In this section conventional and advanced use of the charge-pumping are presented. Moreover, an introduction on the conventional charge pumping is given. The applicability of the

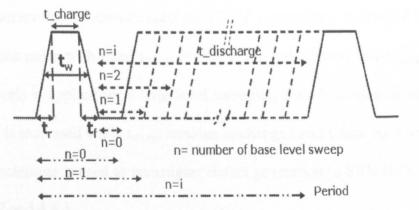

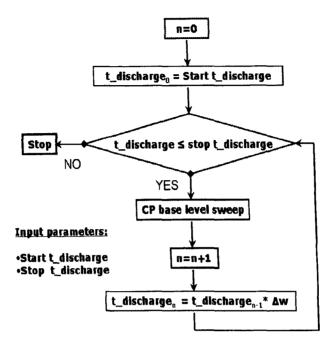

conventional CP combine with the Variable Frequency Charge-Pumping (VFCP) is introduced. Finally we develop the technique of the variable frequency charge pumping by independently controlling the pulse low and high level timings. This technique is called as Variable  $T_{charge}$ - $T_{discharge}$  Charge Pumping (VT<sup>2</sup>CP). In chapter 4, VFCP and VT<sup>2</sup>CP are used to analyze the degradation of MOS devices due to defect generation in SiO<sub>2</sub> and HfO<sub>2</sub> layers.

## 2.4.1 Introduction

The charge-pumping effect in MOS devices has been first reported by J.S.Brugler and P.G.A.Jespers in 1969 [**Brug69**] and by A.Goetzberger and E.H.Nicollian [Goet70]. They have measured a DC component of the bulk current when periodic voltage pulses are applied to the gate in the circuit. This current was in the opposite direction and much larger than the leakage current of the reversely biased source and drain junctions. It was proportional to the pulse frequency and the gate area. This current is called the charge-pumping current  $I_{CP}$

Neglecting the junction leakage current, the DC component of the bulk current is caused by two effects (for n-channel MOSFETs):

1. By varying the gate pulse sufficiently so that the condition at the interface changes from inversion to accumulation, traps at the interface (and some bulk traps) are successively filled by electrons and holes. This produces a positive net bulk hole current and a negative net source/drain electron current. The effect originates due to the longer emission times for traps compared to the duration of the gate-pulse rise and fall times. The charge-pumping current due to this effect contains information on the traps in MOSFETs.

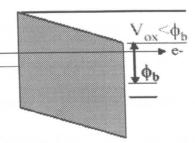

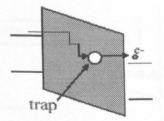

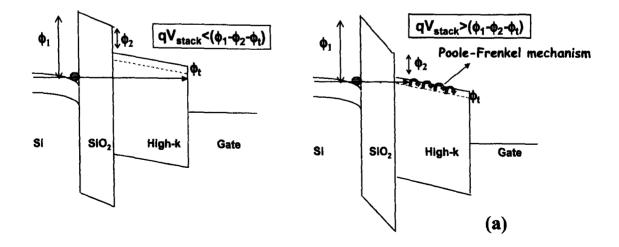

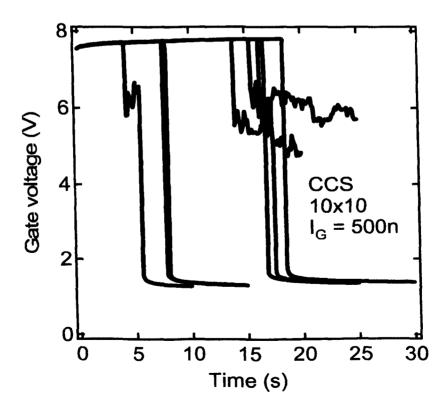

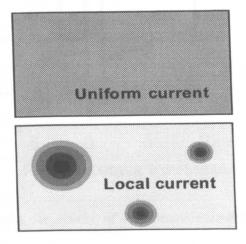

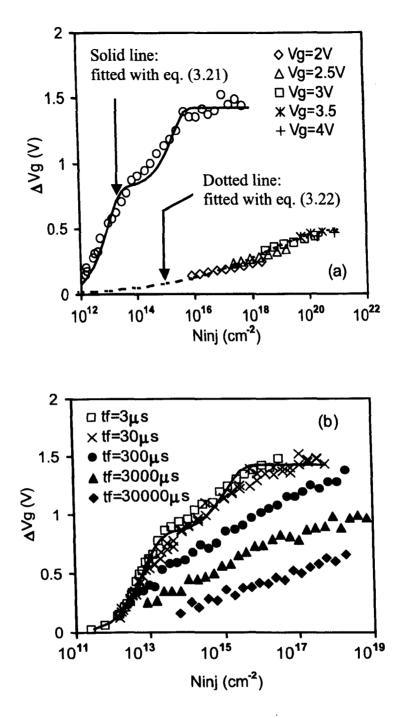

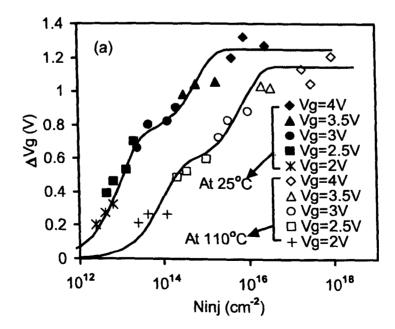

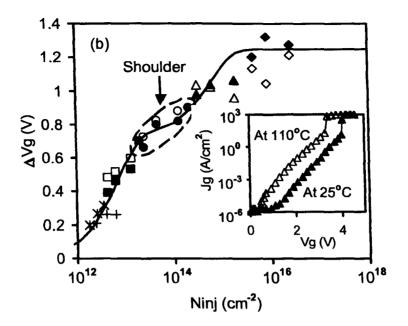

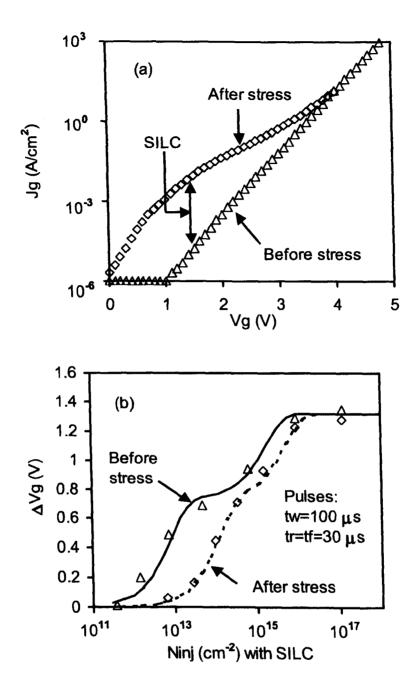

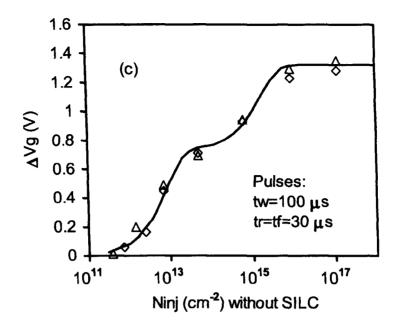

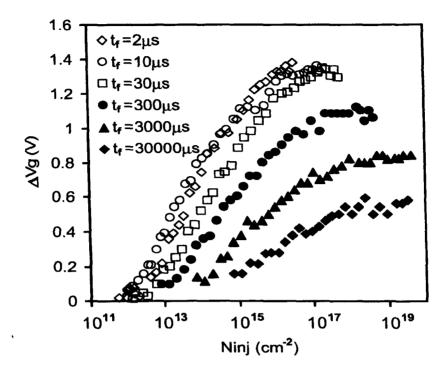

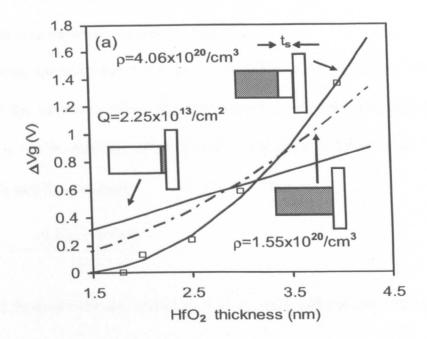

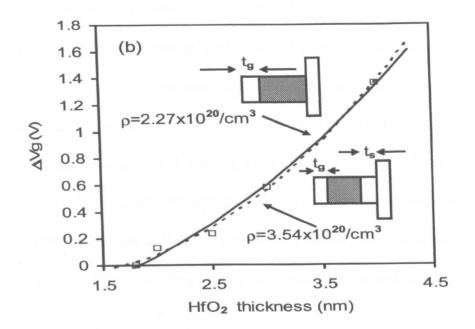

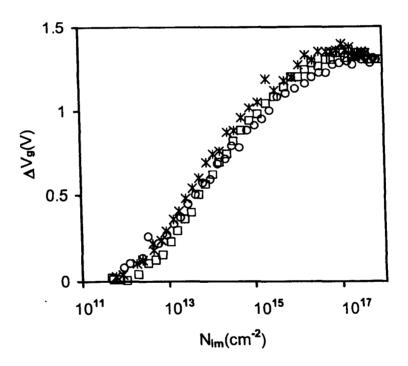

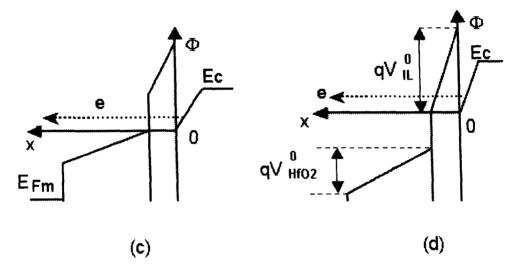

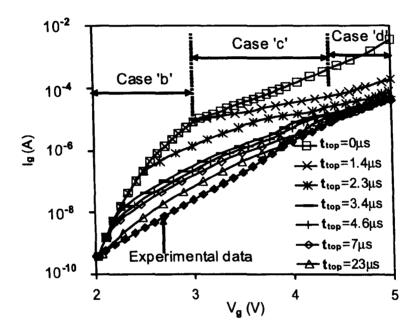

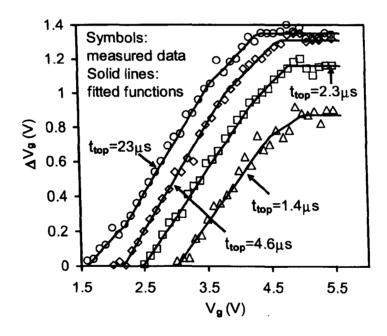

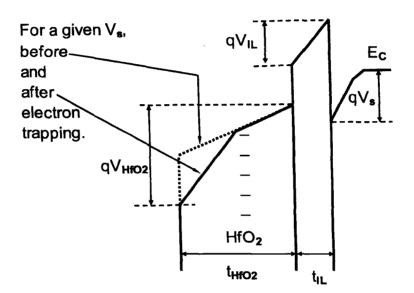

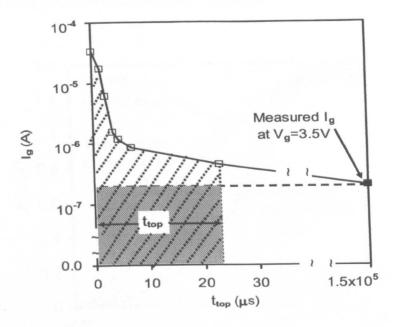

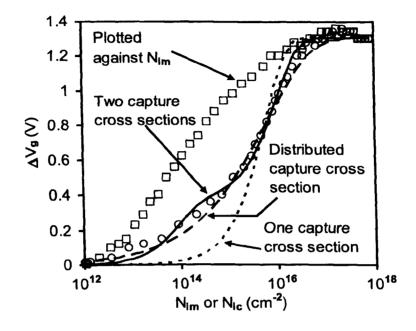

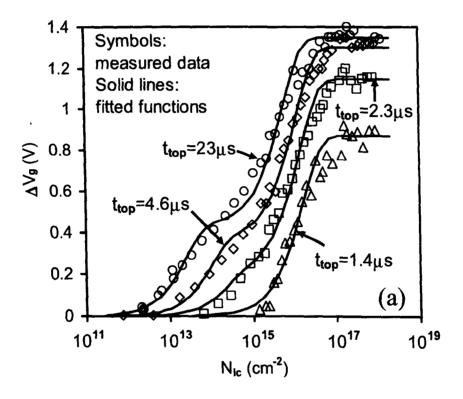

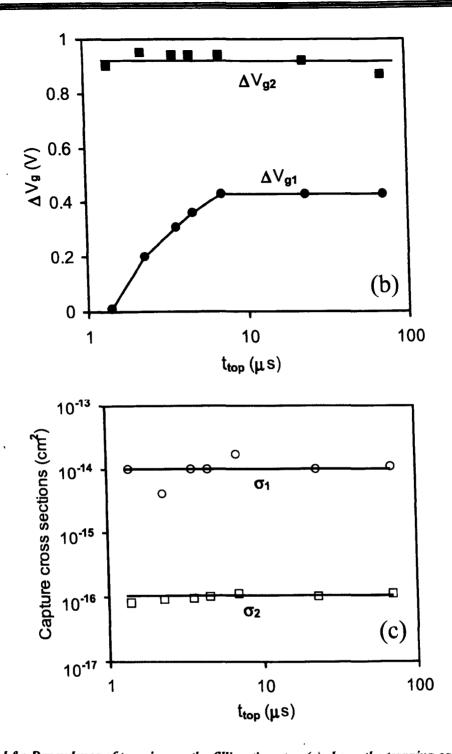

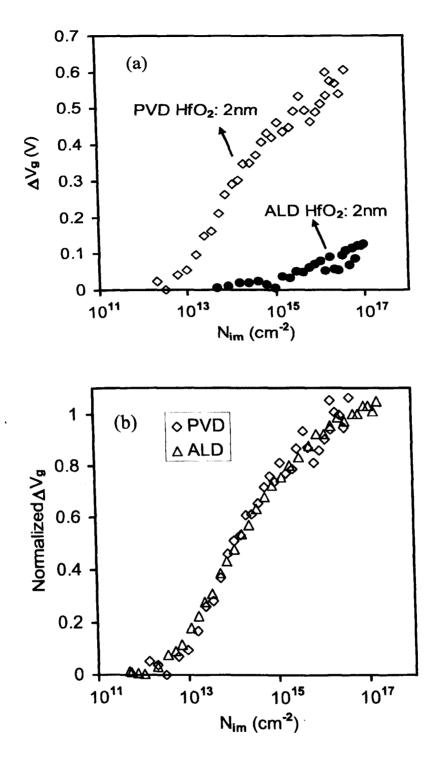

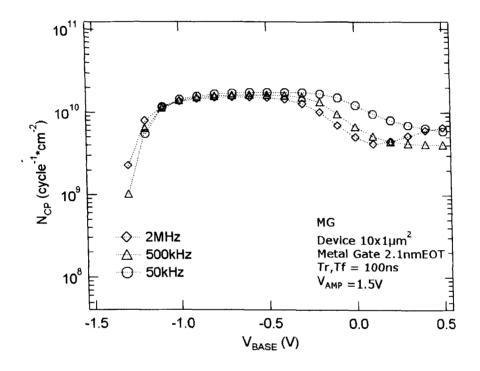

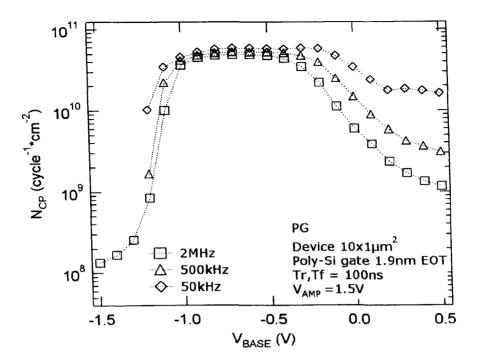

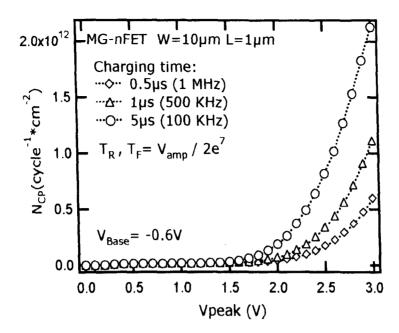

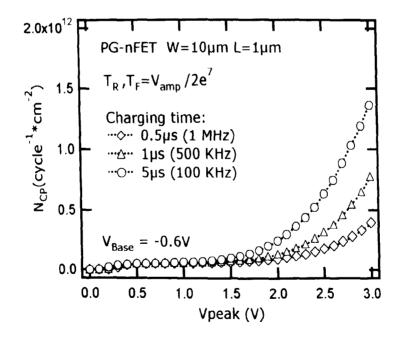

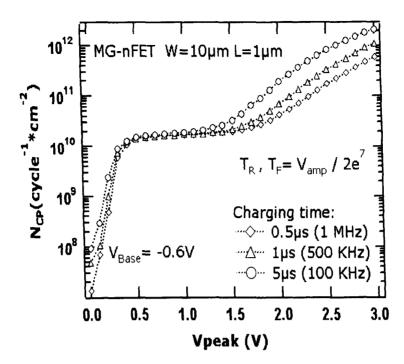

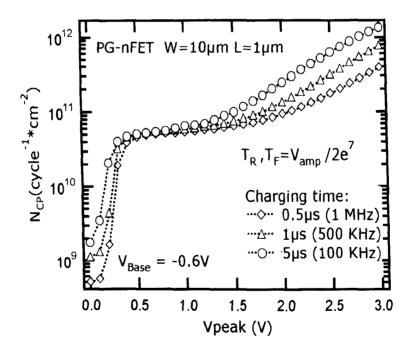

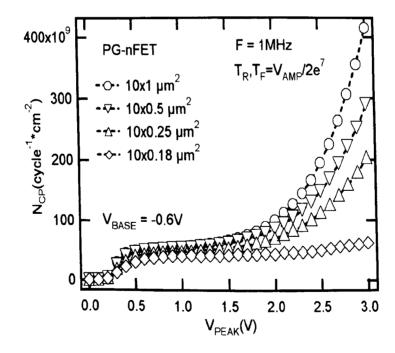

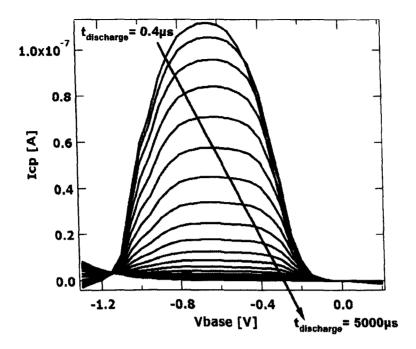

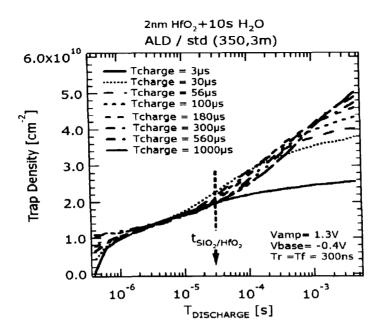

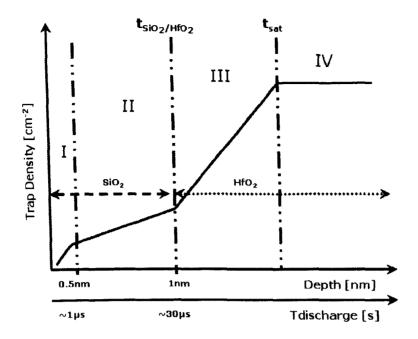

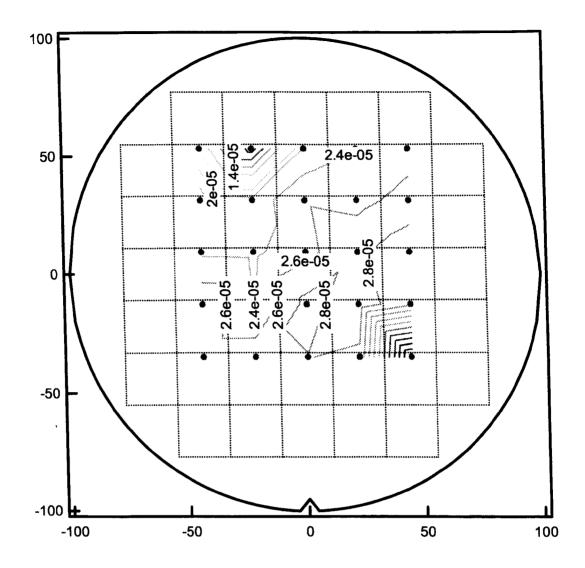

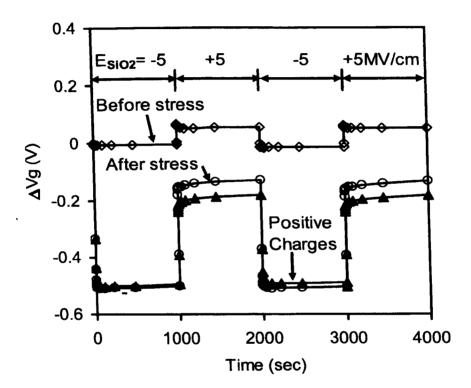

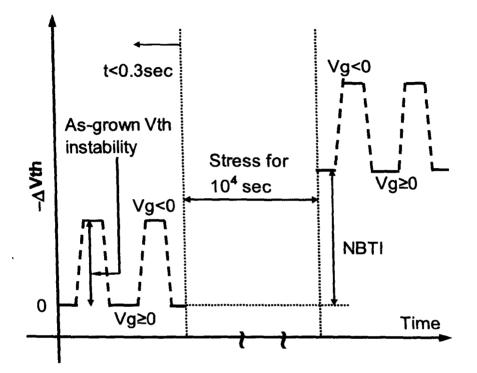

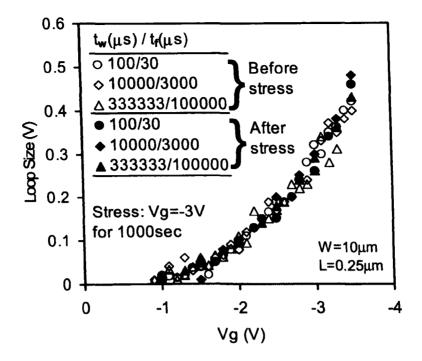

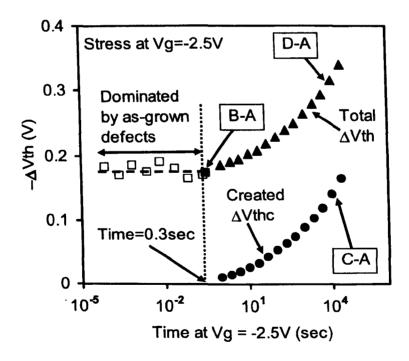

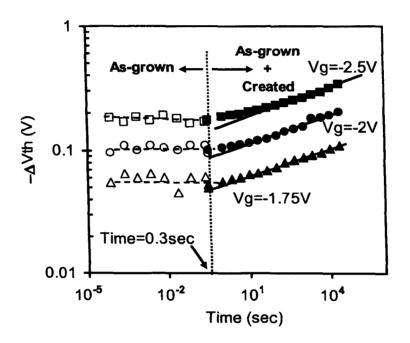

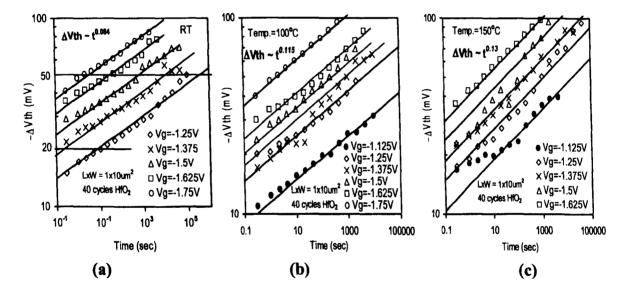

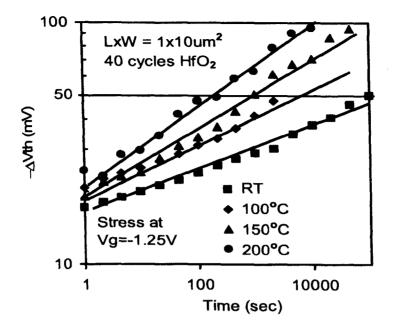

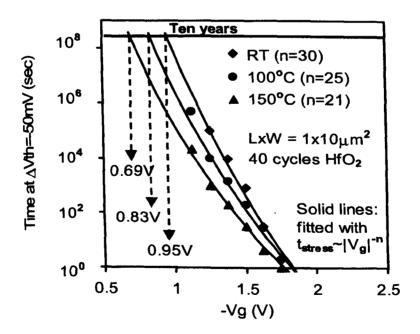

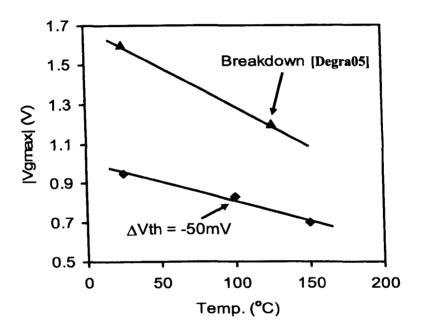

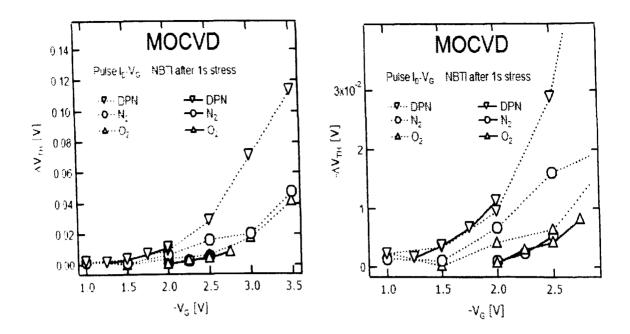

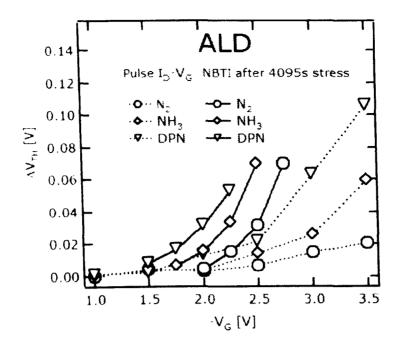

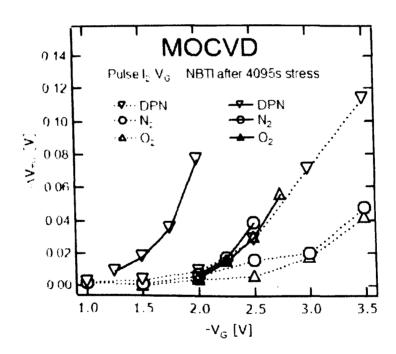

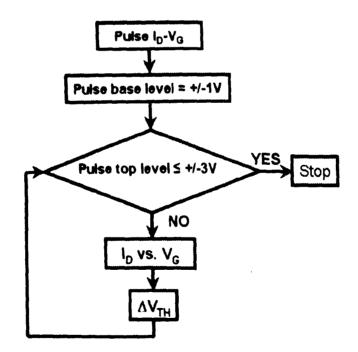

2. For slow turn-off of MOSFETs (long fall time of the gate pulse) electrons in the channel have sufficient time to arrive at the source and drain junctions. The inversion layer vanishes before the accumulation occurs at the interface. However, for fast turn-off, when the fall time of the gate pulse is shorter than the time necessary to remove the inversion layer, a significant amount of electrons remain at the interface when the hole accumulation takes place. These electrons are either recombined by holes or transferred to the bulk, which both produce a positive net bulk current of holes and electrons, respectively. The charge-pumping current due to this fast-switching effect does not contain any information on the traps in the device.