# RELIABILITY CHARACTERISATION OF III-NITRIDES BASED DEVICES FOR TECHNOLOGY DEVELOPMENT

### **STEVEN JOHN DUFFY**

A thesis submitted in partial fulfilment of the requirements of Liverpool John Moores University for the degree of Doctor of Philosophy

December 2018

## ACKNOWLEDGEMENTS

The road towards completing this Thesis has been long and stressful but most importantly, it has made me value my time and the people around me more than anything could. I have the utmost respect for the people that have assisted me throughout this journey, whether it be academically or personally. Without these people I would not have made it as far as I have.

Firstly, my sincerest gratitude goes to my supervisor Dr. Brahim Benbakhti. His support throughout this Ph.D has been invaluable. The encouragement he has given me during the 'highs' and moral support through the 'lows' has brought me to truly feel confident in my profession. Beyond being my supervisor, he has truly cared about my wellbeing from the beginning. For this, I cannot thank him enough and will never forget his assistance.

Secondly, I would like to thank my second supervisor Prof. Wei Zhang. During our meetings he has provided so much insight into our project and has always been there to lend a hand whenever it was needed. I fully respect and appreciate his academic professionalism.

I would also like to thank the teams of collaborators: Dr. Karol Kalna from Swansea University and his team from Nanoelectronic Devices Computational Group; Dr. Ali Soltani from University of Lille and his team from Institute of Electronics, Microelectronics and Nanotechnology (IEMN); and Dr. Edward Wasige from University of Glasgow and his team from Micro- and Nanotechnology Group. In addition, I greatly appreciate the time given by Dr. Edward Wasige and Prof. David Harvey to read and examine my Thesis.

A special thanks goes to my family and friends for their moral support and patience whilst I explained my ideas to them, even if they did not understand a word I was saying. This has helped me more than you know. Last, but certainly not least, a big thank you to Shannon, who has been there for me during the majority of my Ph.D. I am truly grateful for how much you have motivated and encouraged me throughout this time.

### ABSTRACT

III-nitrides based devices are considered as outstanding options for a range of extremely relevant applications. These devices can significantly improve the efficiency of high-power switching appliations. They are predicted to dominate applications in the low carbon economy. In recent years, these devices have been steadily improved and each year new record performances have been reported.

Regardless of the superior performance of III-nitrides based devices, and particularly AlGaN/GaN high electron mobility transistors (HEMTs), achieving reliability at the same time as the high performance that the device boasts is a factor that is holding back widespread commercial and industrial development. Recoverable degradation (e.g. current collapse and on-resistance) and unrecoverable degradation (e.g. access resistance of contacts, and gate leakage current) persist to be limiting reliability factors.

The mechanisms contributing towards performance and reliability degradation of AlGaN/GaN HEMTs, namely self-heating, charge trapping and strain, are required to be minimised; an important step before large-scale deployment can be attained. The strong coupling of these degradation mechanisms, under normal device operation, makes the quantitative contribution of each mechanism indistinct due to the lack of standard characterisation techniques.

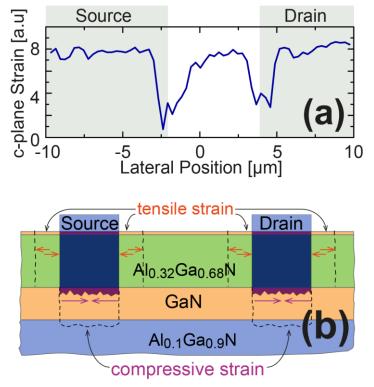

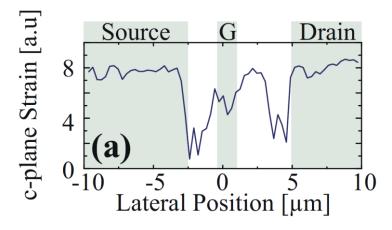

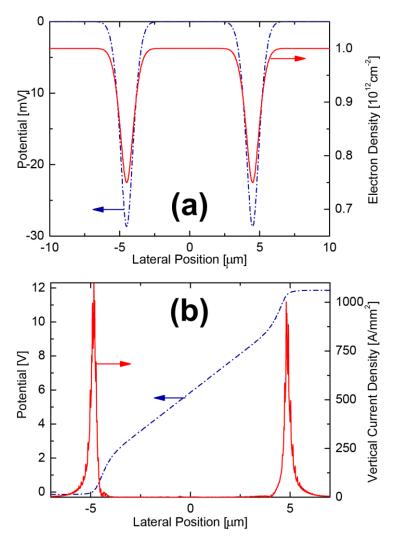

In this Thesis, the impact of the source/drain (S/D) and gate terminals of an AlGaN/GaN HEMT on its thermal management was investigated. Using Infrascope measurements, a substantial increase in temperature and resistance at the inner ends of the S/D contacts was observed. High-resolution X-ray diffraction technique combined with drift-diffusion (DD) simulations showed that strain reduction at the vicinity of S/D contacts is the origin of temperature rise. The strain reduction was also observed below the metal gate. Through electro-thermal simulations, the electrical stress on Ohmic contacts was shown to reduce the strain; leading to the inverse/converse piezoelectric effect.

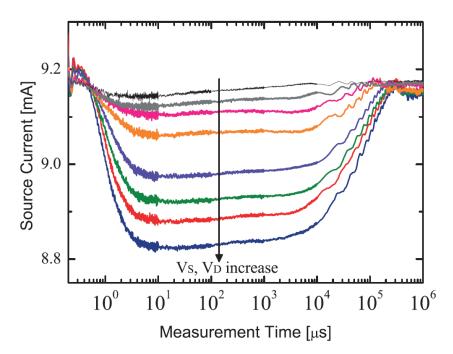

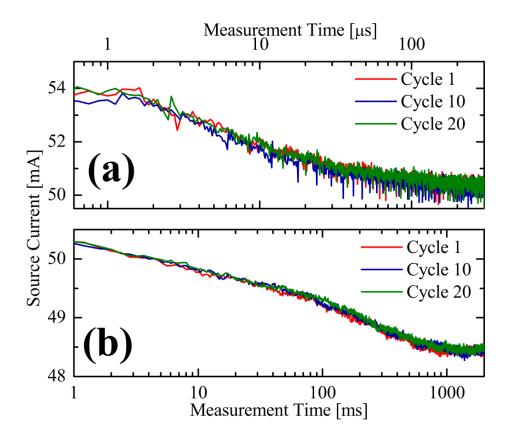

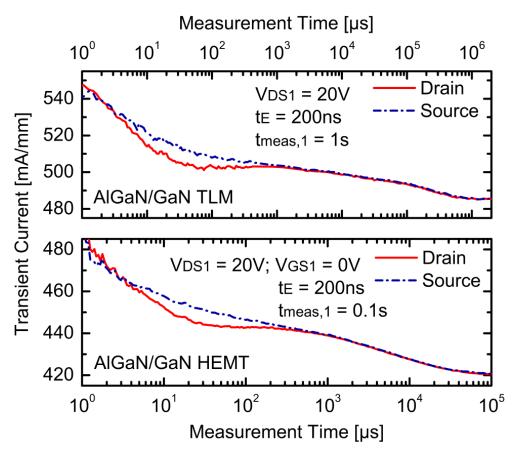

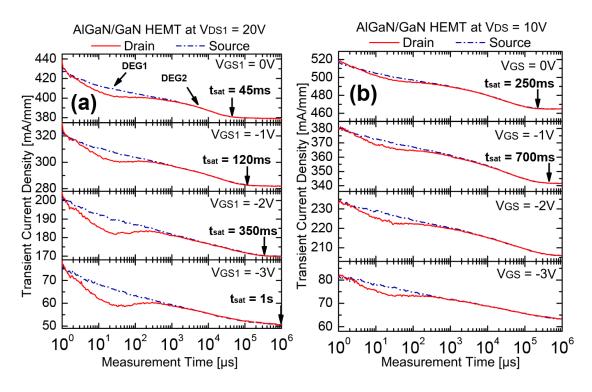

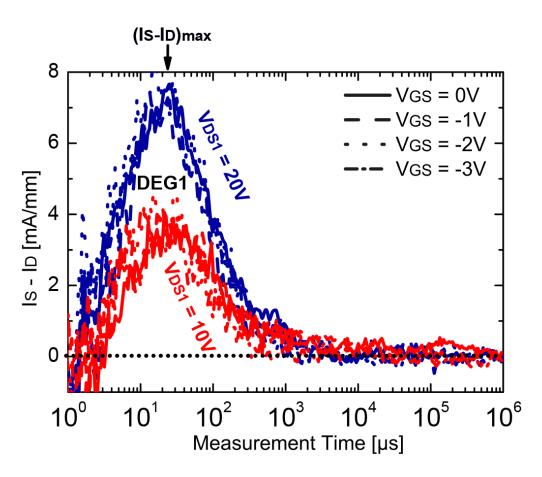

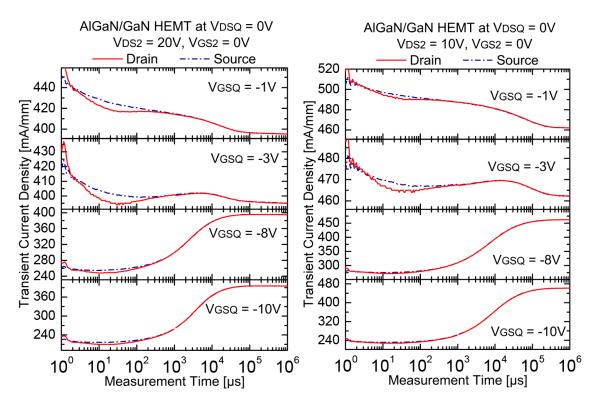

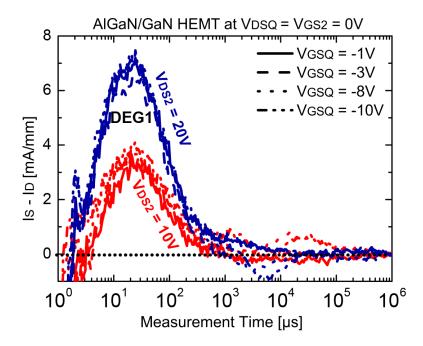

A new parametric technique was developed to decouple the mechanisms constituting device degradation in AlGaN/GaN HEMTs under normal device operation, namely self-heating and charge trapping. Both source (I<sub>S</sub>) and drain (I<sub>D</sub>) transient currents were used under various biasing conditions to analyse charge trapping behaviour. Two types of charge trapping mechanisms have been identified: (i) bulk trapping occurring on a time scale of < 1 ms, followed by (ii) surface trapping and redistribution > 1 ms. Through monitoring the difference between  $I_S$  and  $I_D$ , bulk trapping time constant is shown to be independent of  $V_{DS}$  and  $V_{GS}$ . Also,  $V_{GS}$  is found to have no effect on the bulk trap density. Surface trapping is found to have a much greater impact on slow degradation when compared to self-heating and bulk trapping. At a short time scale (< 1 ms), the RF performance is restricted by both bulk trapping and self-heating effects. At a longer time scale (> 1 ms), the dynamic ON resistance degradation is limited mainly by surface trapping accumulation and redistribution.

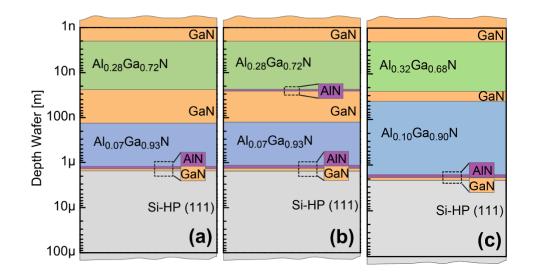

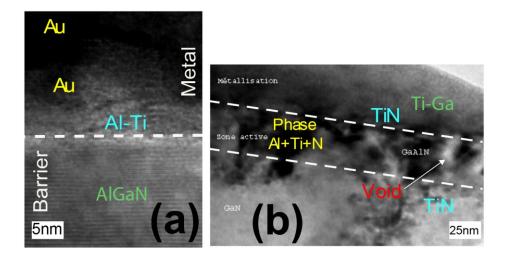

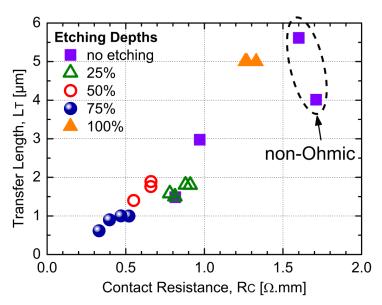

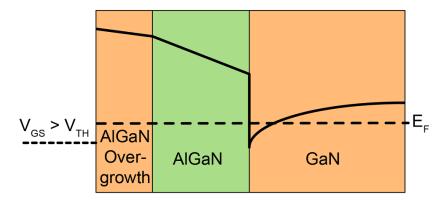

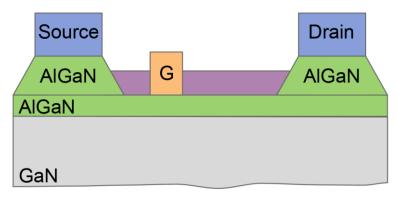

Using the understanding of the degradation mechanism behaviour and origins, optimisations to the Ohmic and Schottky contacts as well as a new AlGaN/GaN HEMT architecture were proposed. In an attempt to improve the thermal management of S/D contacts, an Ohmic contact recess process is proposed to reduce the access resistance and enhance DC/RF performance of AlGaN/GaN HEMTs with a high Al concentration. A contact resistance ( $R_c$ ) of ~0.3  $\Omega$ .mm was achieved via optimal recess conditions. Small  $R_c$  was found to lead to a higher current density at the inner edges of the contact, which resulted in a large increase of channel temperature beneath the S/D contacts. A highly n-doped AlGaN overgrowth layer was proposed to reduce the current density, and thus channel temperature at the Ohmic contacts. Titanium Nitride (TiN) Schottky processing was implemented to minimise the observed strain reduction beneath the gate metal. The optimal Schottky contact is obtained for TiN thicknesses of < 10 nm, which preserves the strain within the AlGaN barrier layer. As a result, Schottky barrier of 1.06 eV, a leakage current of 6 nA and improved linearity of 1.6 was achieved. In addition, C - V and I - V characterisations revealed very low trapping density within the optimised device. Lastly, a new device architecture was proposed to increase the 2dimentional electron gas (2DEG) density and mobility, without compromising the enhancements of our proposed S/D and gate optimisations. This structure consists of (i) step-graded AlGaN barrier layer to increase strain and (ii) AlN spacer layer.

# **CONTENTS**

| ACKNOWLEDGEMENTS | i     |

|------------------|-------|

|                  |       |

|                  |       |

| Abstract         | •• 11 |

| LIST OF FIGURES    | ix    |

|--------------------|-------|

| LIST OF TABLES     | xix   |

| ABBREVIATIONS      | XX    |

| PHYSICAL CONSTANTS | xxiii |

| SYMBOLS            | xxiv  |

| 1. INTRODUCTION                              | 1  |

|----------------------------------------------|----|

| 1.1. BACKGROUND                              | 2  |

| 1.1.1. History of GaN Technology             | 2  |

| 1.1.2. Why GaN Technology?                   | 4  |

| 1.1.3. GaN Applications and Market           | 6  |

| 1.1.4. Figures of Merit                      | 7  |

| 1.2. RATIONALE                               | 9  |

| 1.3. RESEARCH AIM AND OBJECTIVES             | 9  |

| 1.4. Organisation                            | 10 |

| 1.5. ORIGINAL CONTRIBUTION TO RESEARCH FIELD |    |

| 2. AlGa | aN/GaN-BASED DEVICE FUNDAMENTALS &            |    |

|---------|-----------------------------------------------|----|

| CHARAC  | CTERISATION TECHNIQUES                        | 14 |

| 2.1. PH | IYSICAL PROPERTIES OF III-N MATERIALS         | 16 |

| 2.1.1.  | Crystal Structure                             | 16 |

| 2.1.2.  | Material Properties                           | 17 |

| 2.1.3.  | Polarisation                                  | 23 |

| 2.2. Al | GaN/GaN-BASED DEVICE STRUCTURE                | 26 |

| 2.2.1.  | 2-Dimentional Electron Gas (2DEG) Formation   | 26 |

| 2.2.2.  | High Electron Mobility Transistor (HEMT)      |    |

| 2.2.3.  | Substrate Choice                              |    |

| 2.2.4.  | AlGaN/GaN HEMTs State of the Art              |    |

| 2.2.5.  | Metallisation of Device Contacts              |    |

| 2.2.6.  | Advantages & Disadvantages of AlGaN/GaN HEMTs | 43 |

| 2.3. No | ON-INVASIVE CHARACTERISATION TECHNIQUES       | 47 |

| 2.3.1.  | Infrared (IR)                                 | 48 |

| 2.3.2.  | Micro-Raman (µ-Raman)                         | 48 |

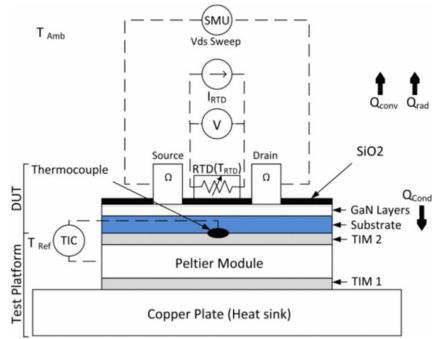

| 2.3.3.  | μ-Resistance Thermal Detector (μ-RTD)         | 49 |

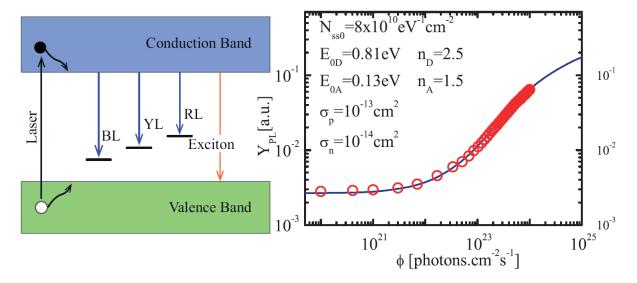

| 2.3.4.  | Photoluminescence (PL)                        | 50 |

| 2.3.5.  | X-Ray Diffraction (XRD)                       | 51 |

| 2.3.6.  | Electrical Characterisation                   |    |

| 2.3.7.  | Characterisation Technique Comparison         | 54 |

| 2.4. Di | EVELOPMENT CHALLENGES                         |    |

| <b>3.</b> STRAIN IMPACT ON SELF-HEATING IN AIGaN/G            |            |

|---------------------------------------------------------------|------------|

| HEMTs                                                         |            |

| 3.1. STRUCTURE OF INVESTIGATED DEVICES                        |            |

| 3.2. STRAIN-REDUCTION INDUCED RISE IN CHANNEL TEMPERATURE     | E AT OHMIC |

| CONTACTS                                                      | 60         |

| 3.2.1. Experimental Procedure                                 | 60         |

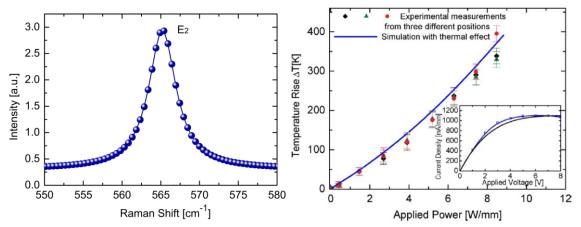

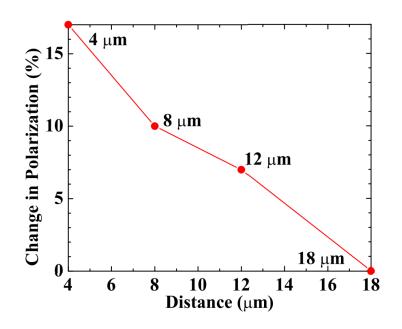

| 3.2.2. Temperature distribution in AlGaN/GaN TLMs             | 63         |

| 3.2.3. AlGaN/GaN HEMT                                         | 70         |

| 3.3. RELATIONSHIP BETWEEN DEVICE SIZE AND POLARISATION IN AI  | GaN/GaN-   |

| BASED DEVICES                                                 | 75         |

| 3.3.1. I - V Simulation Methodology                           | 76         |

| 3.3.2. Electro-thermal Simulation and Calibration Methodology | 77         |

| 3.3.3. The Role of Self-Heating and Polarisation              | 81         |

| 3.4. SUMMARY                                                  |            |

#### 4. A PARAMETRIC TECHNIQUE FOR TRAP

#### CHARACTERISATION IN AlGaN/GaN-BASED DEVICES.....88

| 4.1. | DE   | GRADATION OF CURRENT MISCONCEPTIONS | 89 |

|------|------|-------------------------------------|----|

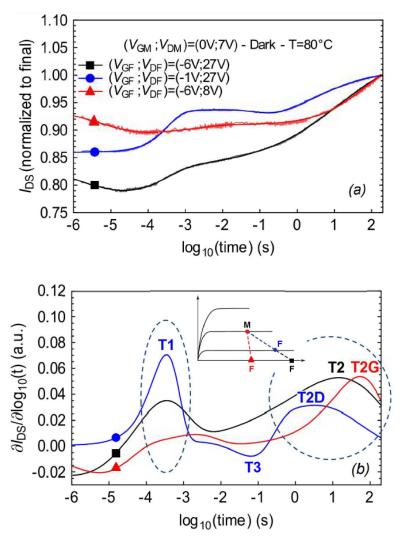

| 4.2. | Sei  | LF-HEATING MODEL                    | 91 |

| 4.3. | EL   | ECTROSTATIC TRAPPING                | 93 |

| 4.4. | DE   | VICE AND INSTRUMENTS                | 94 |

| 4.4  | 4.1. | Device Performance                  | 94 |

| 4.4  | 4.2. | Device Reset Conditions             | 96 |

| 4.5. Tr. | ANSIENT CURRENT DEGRADATION               | 98  |

|----------|-------------------------------------------|-----|

| 4.5.1.   | Experimental Methodology                  | 98  |

| 4.5.2.   | Bulk Trapping                             |     |

| 4.5.3.   | Surface Trapping                          |     |

| 4.6. Sei | LF-HEATING & CHARGE TRAPPING MECHANISMS   |     |

| 4.6.1.   | Experimental Methodology                  |     |

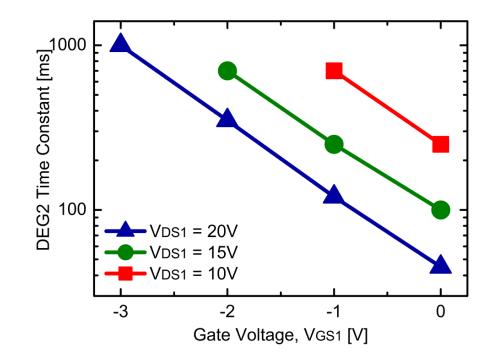

| 4.6.2.   | Primary Slow Degradation (DEG2) Mechanism | 107 |

| 4.6.3.   | Bulk Trapping vs. Surface Trapping        | 109 |

| 4.7. Su  | MMARY                                     |     |

#### 5. OHMIC/SCHOTTKY CONTACT OPTIMISATION AND

| DEVICE  | ENGINEERING11                                                 | 2 |

|---------|---------------------------------------------------------------|---|

| 5.1. DE | vice Structure                                                | 3 |

| 5.2. Of | IMIC CONTACT OPTIMISATION FOR ACCESS RESISTANCE LOWERING . 11 | 4 |

| 5.2.1.  | Ohmic Contact Optimisation for AlGaN/GaN HEMTs 11             | 5 |

| 5.2.2.  | Contact Overgrowth for Self-Heating Reduction12               | 6 |

| 5.3. Sc | HOTTKY CONTACT OPTIMISATION FOR GATE LEAKAGE REDUCTION 12     | 7 |

| 5.3.1.  | Current Schottky Contact Technology12                         | 9 |

| 5.3.2.  | TiN Gate Technology13                                         | 0 |

| 5.3.3.  | Device Performance                                            | 2 |

| 5.3.4.  | TiN Diffusion                                                 | 7 |

| 5.4. St | EP-GRADED AIGaN BARRIER WITH AIN SPACER AND InGaN CHANNEL     |   |

| STRUCTU | RE                                                     | 139 |

|---------|--------------------------------------------------------|-----|

| 5.4.1.  | Device Structures                                      | 139 |

| 5.4.2.  | Simulation Methodology                                 | 141 |

| 5.4.3.  | Process Design Considerations                          | 142 |

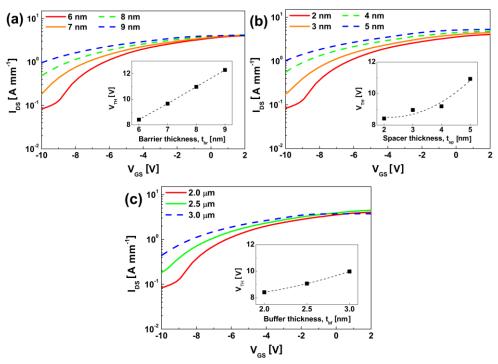

| 5.4.4.  | Impact of Architectural Geometry on Device Performance | 148 |

| 5.5. Su | MMARY                                                  | 150 |

| 6. Co | NCLUSION                                             |  |

|-------|------------------------------------------------------|--|

| 6.1.  | CONCLUSION                                           |  |

| 6.2.  | FUTURE WORKS                                         |  |

| 6.2.  | 1. Decoupling of Bulk Trapping and Self-Heating      |  |

| 6.2.2 | 2. Thermal Management of Strain-Induced Self-Heating |  |

| LIST OF PUBLICATIONS & CONFERENCES | LIST OF PUBLICATIONS & CONFERENCES | 159 |

|------------------------------------|------------------------------------|-----|

|------------------------------------|------------------------------------|-----|

| 7. | <b>REFERENCES</b> | 16 | 1 | - |

|----|-------------------|----|---|---|

|----|-------------------|----|---|---|

| A. APPENDIX                                    |  |

|------------------------------------------------|--|

| A.1. PROBING STATION AND MEASUREMENT FRAMEWORK |  |

| A.1.1. Summit 12000-AP Probing Station         |  |

| A.1.2. Keithley 4200A-SCS Parametric Analyser  |  |

| A.2. INSTRUMENT CALIBRATION                    |  |

# LIST OF FIGURES

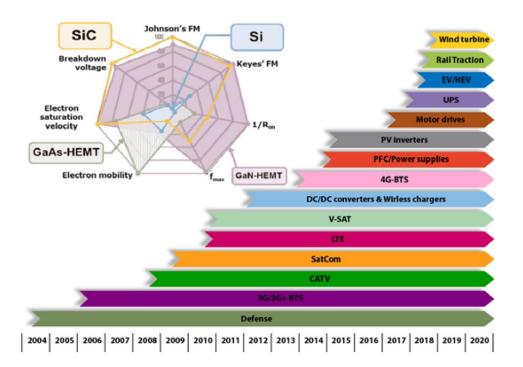

| Figure 1.1: III-Nitrides device applications roadmap (short, mid and long-term growth driver).                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The inset shows a comparison of GaN, 4H-SiC, Si and GaAs high-power RF                                                                                                                    |

| transistors [57]7                                                                                                                                                                         |

|                                                                                                                                                                                           |

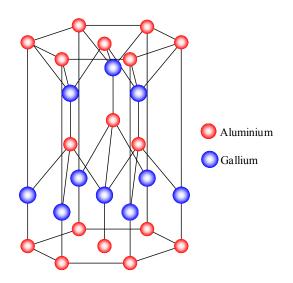

| Figure 2.1: Crystal structure of GaN in Wurtzite form [67]17                                                                                                                              |

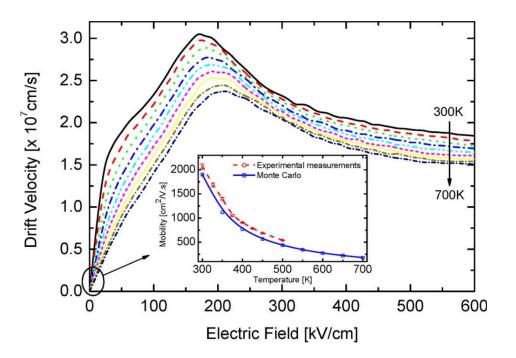

| Figure 2.2: Electron drift velocity versus electric field in GaN for different lattice temperatures                                                                                       |

| (from 300 to 700 K by a step of 50 K). The inset compares measured (dashed line) low field                                                                                                |

| electron mobility of GaN as a function of the lattice temperature with Monte Carlo simulations                                                                                            |

| (solid line)                                                                                                                                                                              |

|                                                                                                                                                                                           |

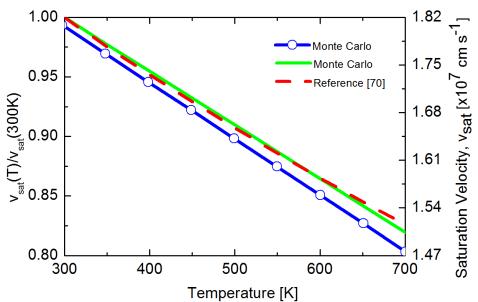

| Figure 2.3: Saturation velocity of GaN versus lattice temperature. Comparison between the                                                                                                 |

| results of [70] (dash line) and the Monte Carlo data (solid line)19                                                                                                                       |

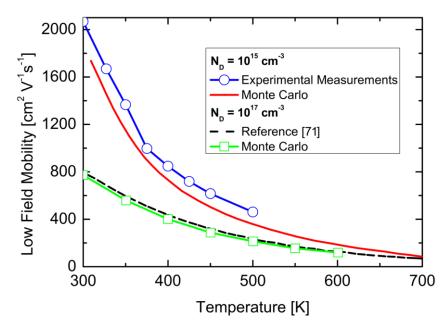

| Figure 2.4: Low field mobility of GaN versus lattice temperature. Measured (circles) and                                                                                                  |

| Monte Carlo data at $N_D = 10^{15}$ cm <sup>-3</sup> (solid line) and $N_D = 10^{17}$ cm <sup>-3</sup> (dashed line)20                                                                    |

|                                                                                                                                                                                           |

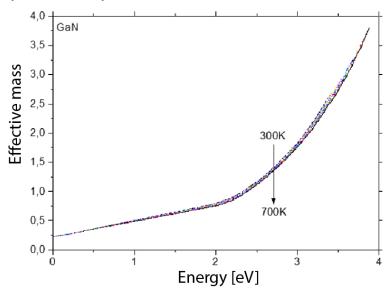

| Figure 2.5: Effective mass as a function of electron energy at different lattice temperatures                                                                                             |

| (from 300 K to 700 K by step of 50 K)                                                                                                                                                     |

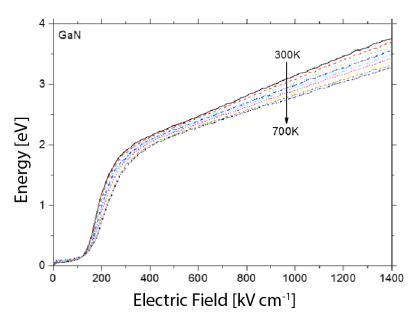

| Figure 2.6: Energy – electric field characteristics at different lattice temperatures (from 300 K                                                                                         |

| to 700 K by step of 50 K)21                                                                                                                                                               |

|                                                                                                                                                                                           |

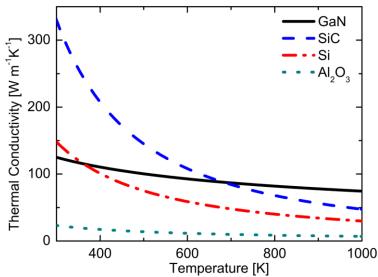

| Figure 2.7: Model of thermal conductivity – temperature characteristics of various substrates $(C_2)$ Si SiC Al O ) using model of Equation (2.2) and thermal conductivities at 200 K and |

| (GaN, Si, SiC, Al <sub>2</sub> O <sub>3</sub> ) using model of Equation (2.3) and thermal conductivities at 300 K and                                                                     |

| fitting parameters from Table 2.1                                                                                                                                                         |

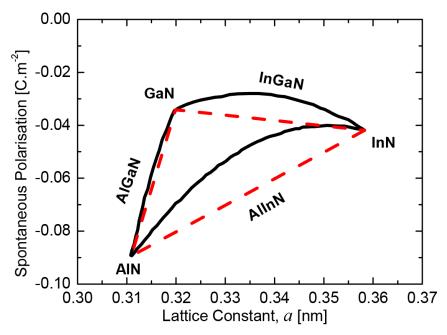

| Figure 2.8: Spontaneous polarisation with respect to lattice constant of multiple compounds.                                                                                              |

| The dashed red lines show linear Vegard-like interpolation, solid black lines show the                                                                                                    |

| approximation to second order in disordered ternary nitride alloys                                                                                                                        |

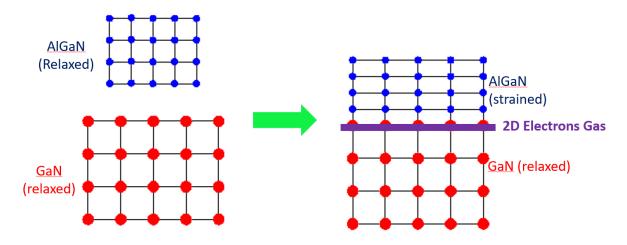

| Figure 2.9: Illustration of how AlGaN is strained upon growth on GaN to form 2DEG27                                                                                                       |

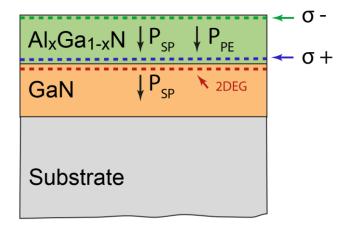

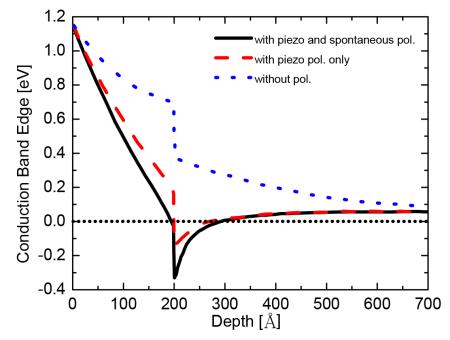

Figure 2.10: Spontaneous and piezoelectric polarisation as well as charge that produces a 2DEG

| in a typical AlGaN/GaN HEMT27                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.11: AlGaN/GaN energy band diagram demonstrating effects of $P_{SP}$ and $P_{PE}$ on conduction energy band [82]                                                                                                                                                                                                                   |

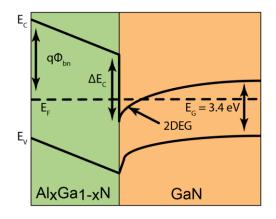

| Figure 2.12: Band structure of $Al_xGa_{1-x}N/GaN$ heterostructure showing 2DEG formation at the $Al_xGa_{1-x}N/GaN$ heterojunction as a result of quantum well formation                                                                                                                                                                  |

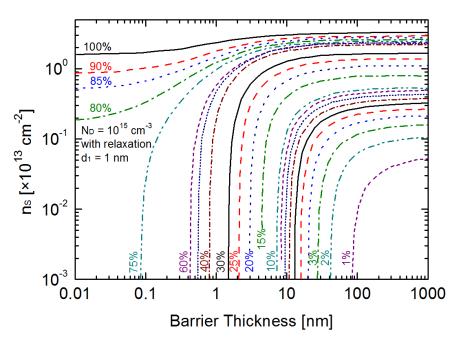

| Figure 2.13: 2DEG sheet density relationship with AlGaN mole fraction                                                                                                                                                                                                                                                                      |

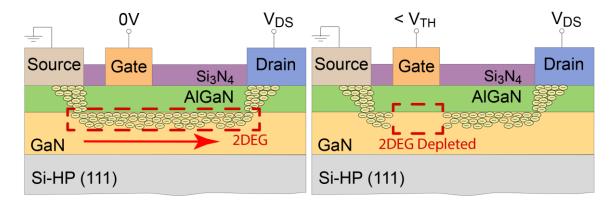

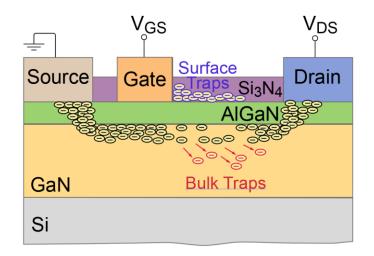

| Figure 2.14: Illustration of GaN-based HEMT with AlGaN/GaN heterostructure and $Si_3N_4$ passivation when the device is in (a) ON-state, and (b) OFF-state                                                                                                                                                                                 |

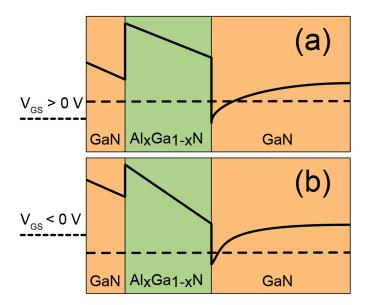

| Figure 2.15: Influence of the gate voltage on the energy band structure: a) $V_{GS} > V_{TH}$<br>and b) $V_{GS} < V_{TH}$                                                                                                                                                                                                                  |

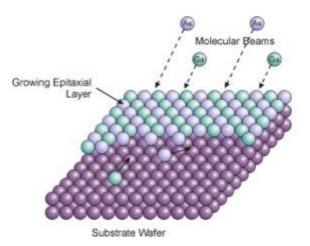

| Figure 2.16: Molecular Beam Epitaxy layer-by-layer growth on substrate process                                                                                                                                                                                                                                                             |

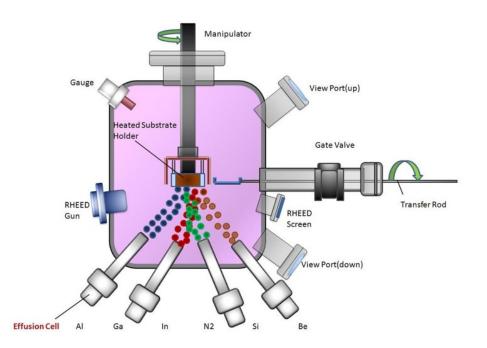

| Figure 2.17: Molecular Beam Epitaxy (MBE) instruments used for growing AlGaN/GaN-based devices                                                                                                                                                                                                                                             |

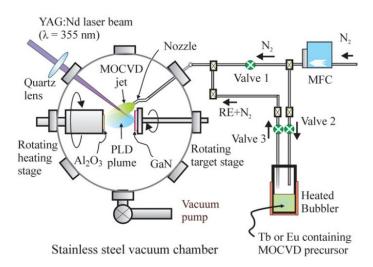

| Figure 2.18: Schematic diagram of the MOCVD deposition system [26]35                                                                                                                                                                                                                                                                       |

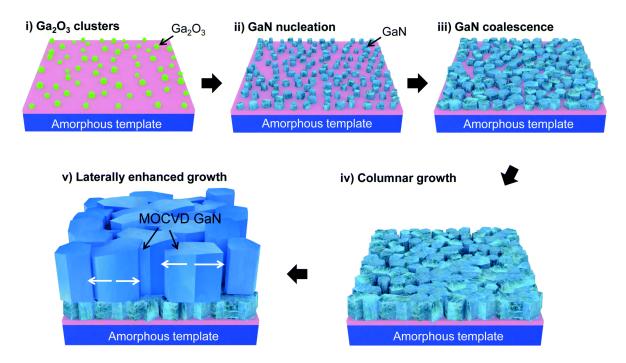

| Figure 2.19: MOCVD illustration showing how reactants are deposited onto the substrate to form layers of semiconductor compounds [88]                                                                                                                                                                                                      |

| Figure 2.20: Benchmarking of state-of-the-art AlGaN/GaN HEMTs on Si and SiC, using power saturation vs. frequency, showing the superiority of AlGaN/GaN HEMTs on SiC                                                                                                                                                                       |

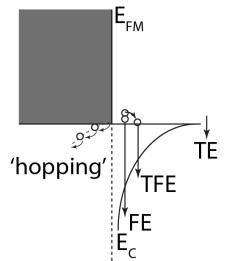

| Figure 2.21: Illustration of charge carrier transport mechanisms for (i) TE, (ii) FE, (iii) TFE, and (iv) emission by 'hopping'; where $E_{FM}$ is the metal Fermi level40                                                                                                                                                                 |

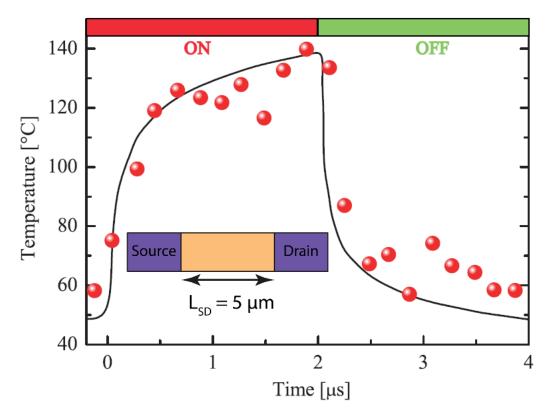

| Figure 2.22: Self-heating/cooling-down characteristics for (i) experimental measurements<br>using a $W = 150 \ \mu\text{m}$ , $L_{SD} = 5 \ \mu\text{m}$ AlGaN/GaN TLM, and (ii) simulation data for equivalent<br>device [124]; $V_{DS} = 20 \ \text{V}$ . Self-heating/cooling-down characteristics are shown to be near-<br>symmetrical |

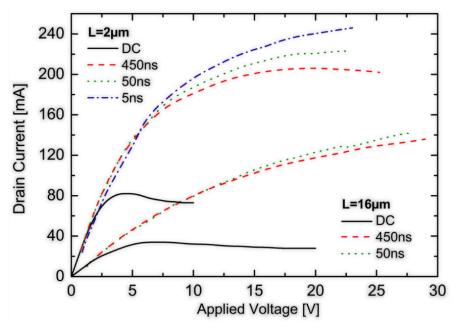

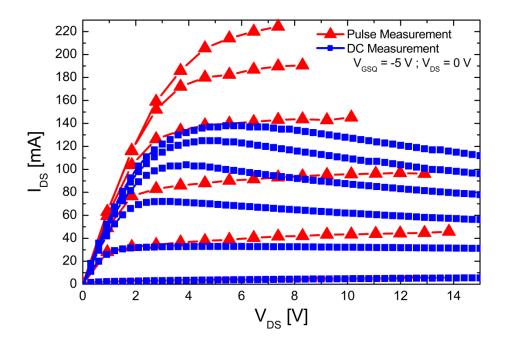

| Figure 2.23: I <sub>DS</sub> – V <sub>DS</sub> characteristics for devices of various length measured under DC and pulse measurements with varying pulse widths                                                                                                                                                                            |

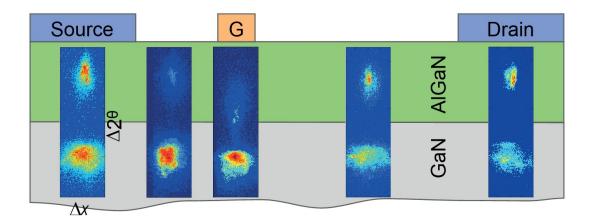

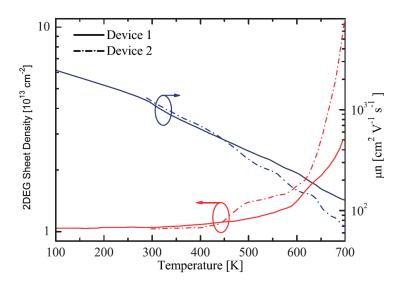

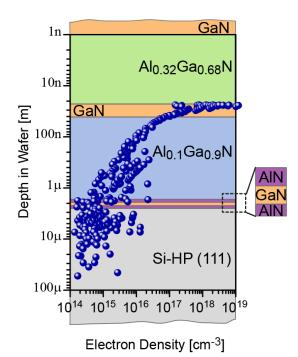

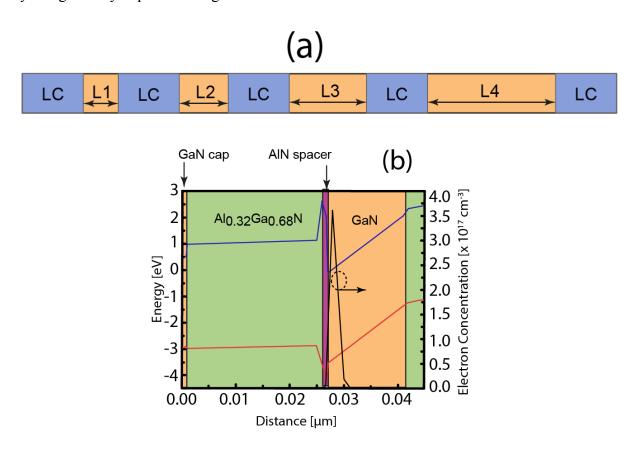

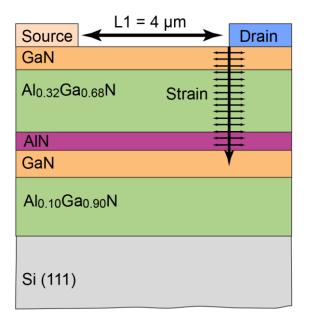

Figure 3.1: AlGaN/GaN-based device structure and measured electron density profile of the investigated wafer,  $GaN(1 \text{ nm})/Al_{0.32}Ga_{0.68}N(25 \text{ nm})/GaN(15 \text{ nm})/Al_{0.10}Ga_{0.90}N(1.7 \mu\text{m})/NL/HP-Si(111)$ , where NL are nucleation layers that consist of AlN(40 nm)/GaN(250 nm)/AlN(250 nm).

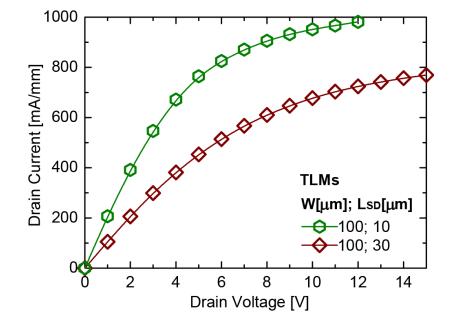

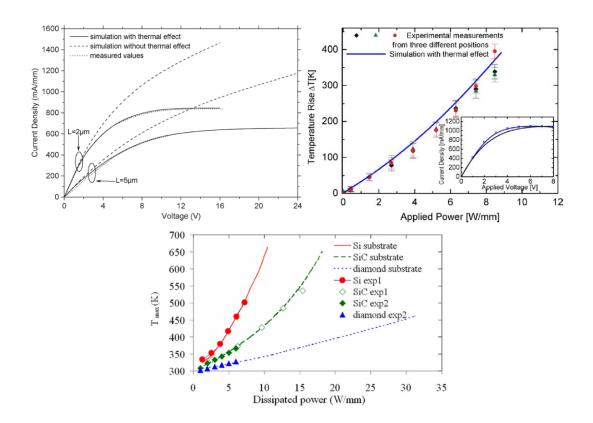

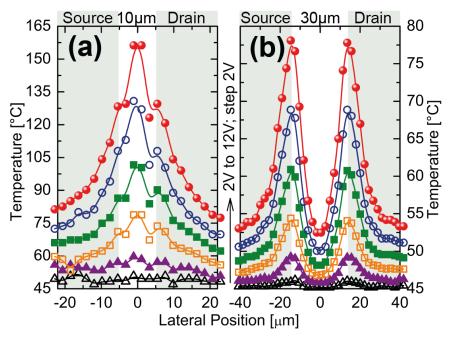

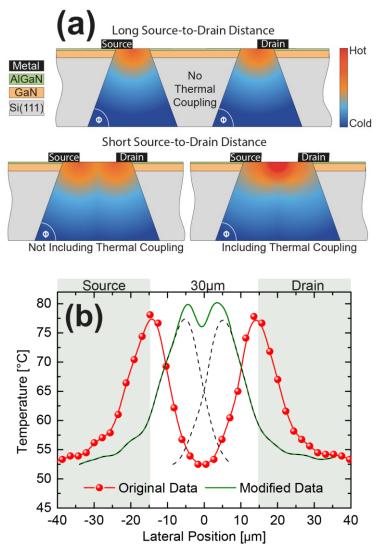

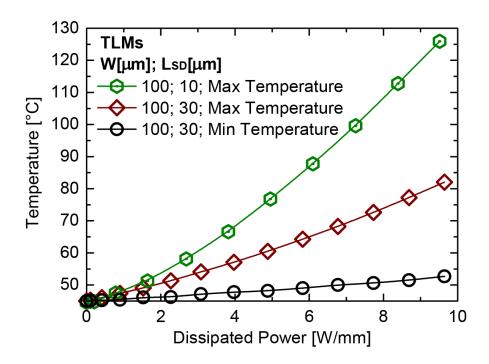

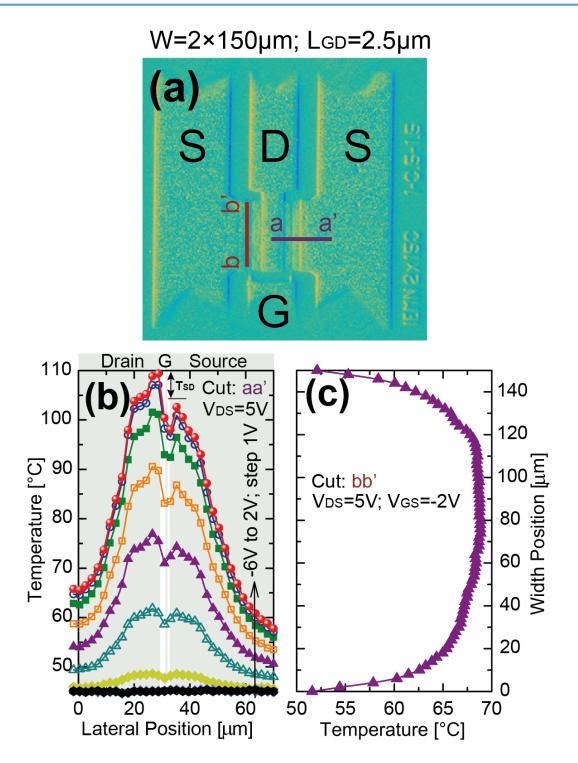

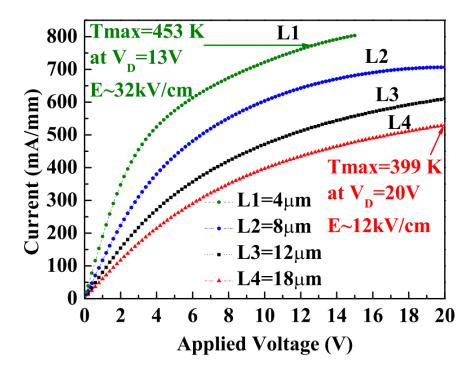

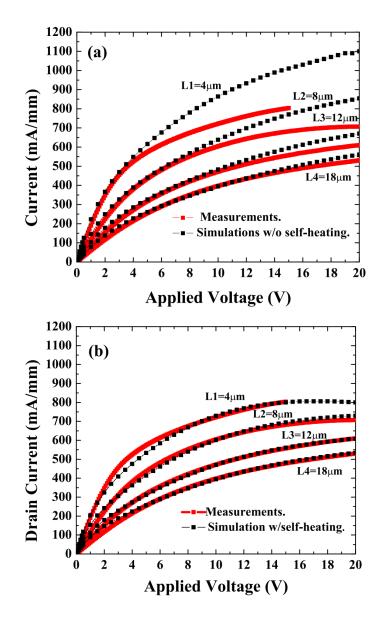

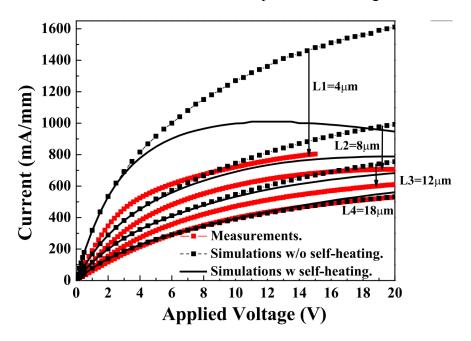

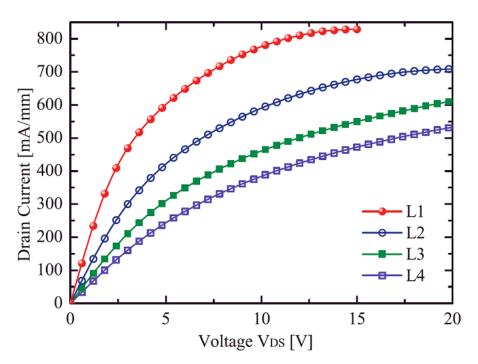

Figure 3.3: I - V characteristics and operating temperatures for different device structures

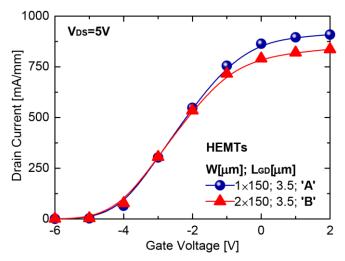

Figure 3.11: Measured  $I_D - V_G$  characteristics of single and two-finger gate AlGaN/GaN

| HEMTs at $V_{DS} = 5$ V. The | device dimensions | are: $L_{SG} = 1.0 \ \mu m, \ L_G =$ | = 0.5 μm, |

|------------------------------|-------------------|--------------------------------------|-----------|

| $L_{GD} = 3.5 \ \mu m$       |                   |                                      | 70        |

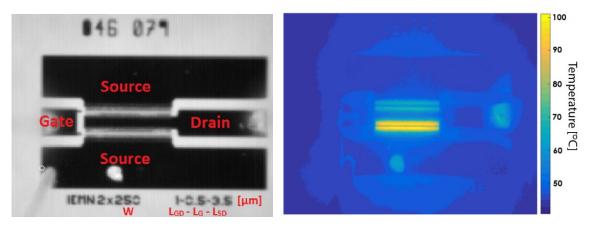

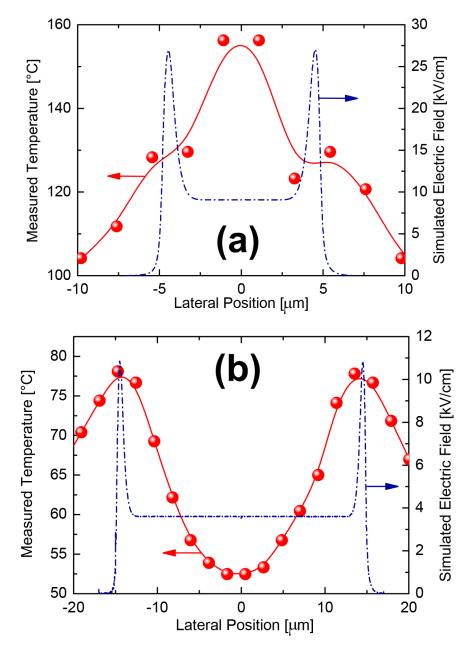

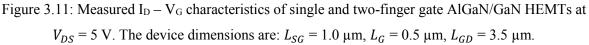

Figure 3.12: (a) Layout of two-finger gate AlGaN/GaN HEMTs. (b) Measured temperature profiles at  $V_{DS} = 5$  V and at different gate voltages (-6 V to 2 V; step 1 V) along the lateral position (Cut: aa'). (c) Temperature distribution at  $V_{DS} = 5$  V and  $V_{GS} = -2$  V along the width position (Cut: bb'). The device dimensions are:  $L_{SG} = 1.0 \ \mu\text{m}$ ,  $L_G = 0.5 \ \mu\text{m}$ ,  $L_{GD} = 2.5 \ \mu\text{m}$ ...72

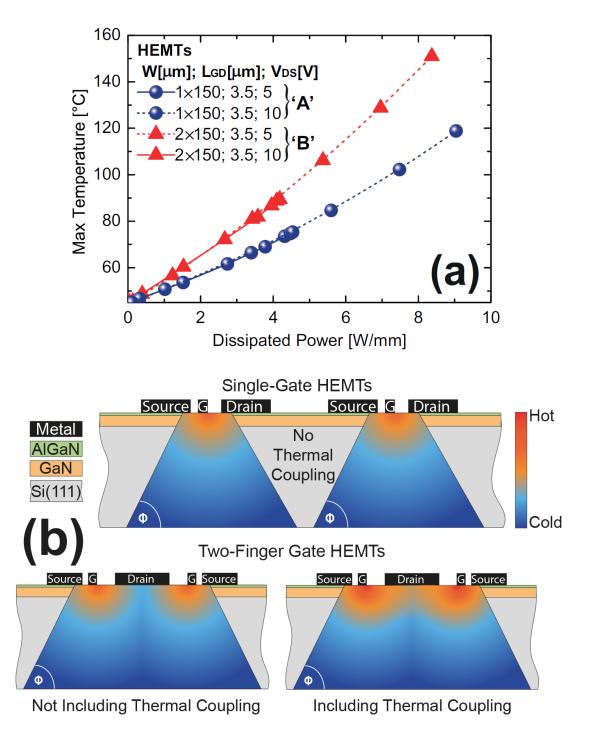

| Figure 3.13: (a) Evolution of the maximum channel temperature versus the dissipated power          |

|----------------------------------------------------------------------------------------------------|

| density of single and two-finger gate AlGaN/GaN HEMTs ('A': $W = 1 \times 150 \mu m$ ; and 'B': W  |

| = 2 × 150 µm. The device dimensions are: $L_{SG}$ = 1.0 µm, $L_G$ = 0.5 µm, $L_{GD}$ = 3.5 µm. (b) |

| Illustration of the heat spreading angle in single and two-finger gate AlGaN/GaN HEMTs73           |

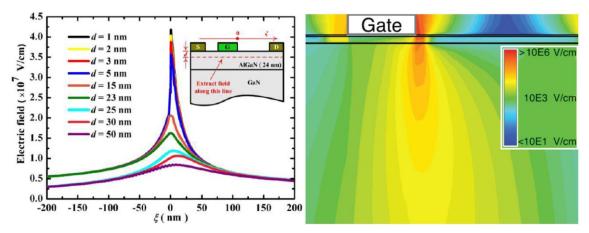

Figure 3.15: Numerical simulation of electric field distribution in an AlGaN/GaN HEMT. ..74

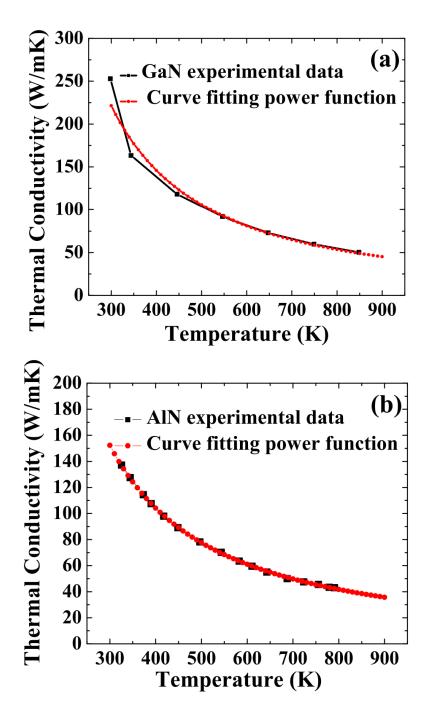

Figure 3.20: Thermal conductivity as a function of temperature compared with a fitting power function for (a) GaN [174] and (b) AlN [175]......81

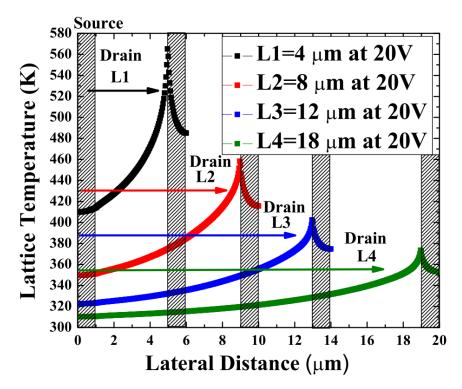

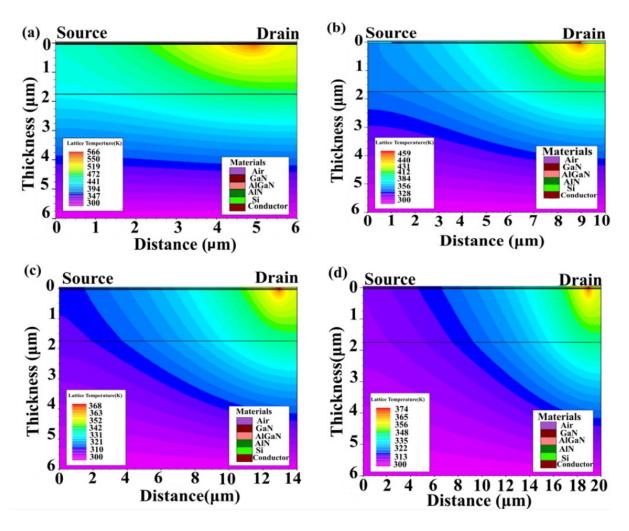

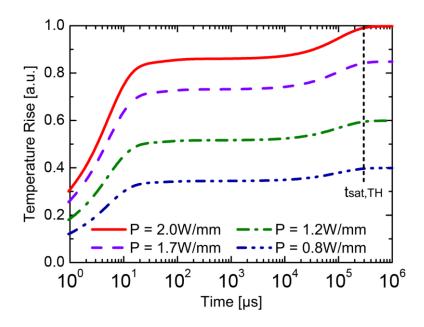

Figure 3.21: Lattice temperature profiles in the 2DEG along the channel for different source-

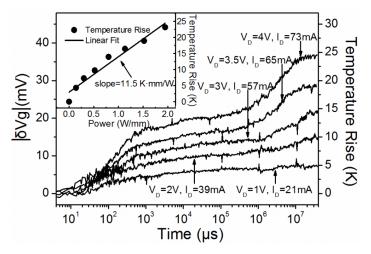

Figure 4.2: Transient temperature rise curves of the device under different electrical bias conditions. (inset) relationship between temperature rise and power density [194]......91

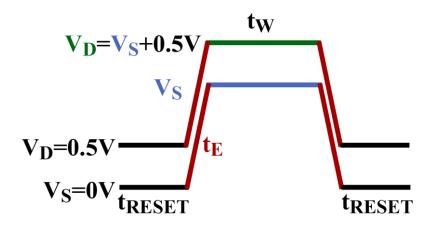

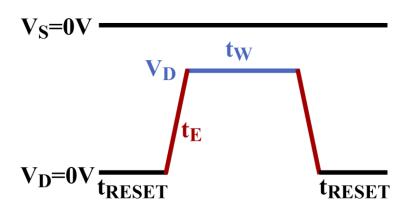

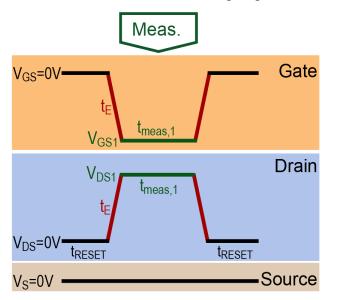

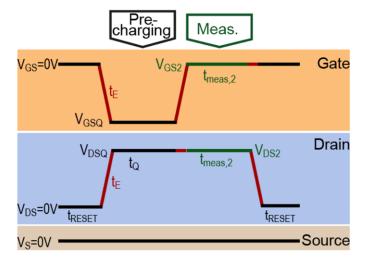

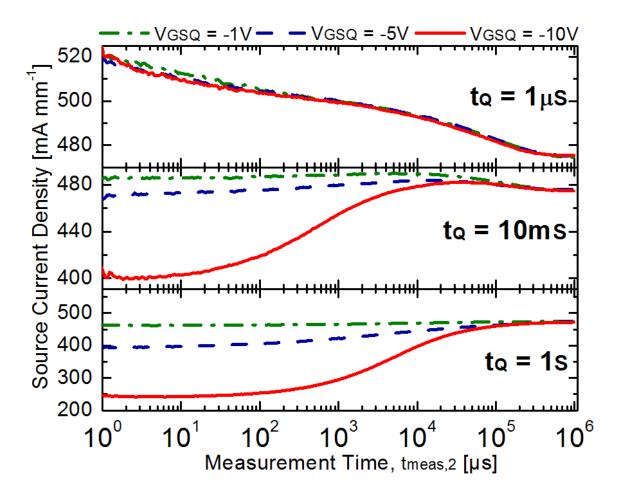

Figure 4.15: Pulse waveforms used for  $I_S$  and  $I_D$  transient measurements where surface and bulk traps are pre-charged during the pre-charging condition at  $V_{DSQ}$  and  $V_{GSQ}$  for a time  $t_Q$ . Transient current measurements are then taken at  $V_{DS2}$  and  $V_{GS2}$  for a time  $t_{meas,2}$ ......106

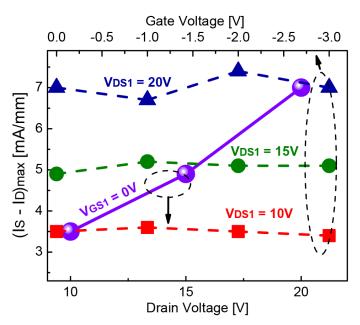

Figure 4.18:  $I_S$  and  $I_D$  difference  $(I_S - I_D)$  versus the measurement time at  $V_{DS2} = 20$  V and 10 V for different gate voltages ( $V_{GS2} = -1$  V, -3 V, -8 V, and -10 V). When compared with Figure 4.12, this validates that no charge carriers are trapped in the bulk during pre-charging. ...... 110

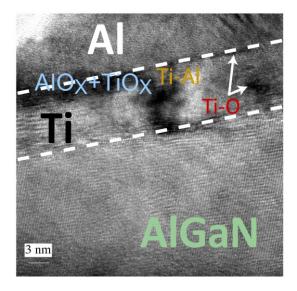

Figure 5.2: HRTEM images from University of Lille of Ohmic contacts at the Ti/Al<sub>0.28</sub>Ga<sub>0.72</sub>N interface after rapid thermal annealing, forming an alloy compositions at (a) 750 °C and (b) 900 °C.

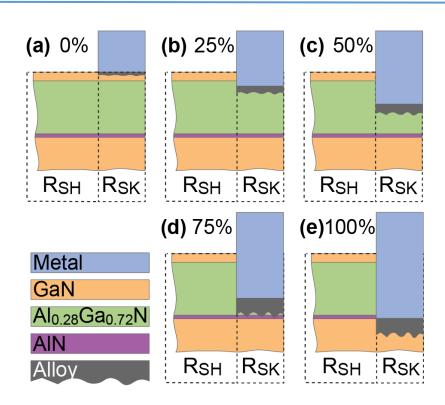

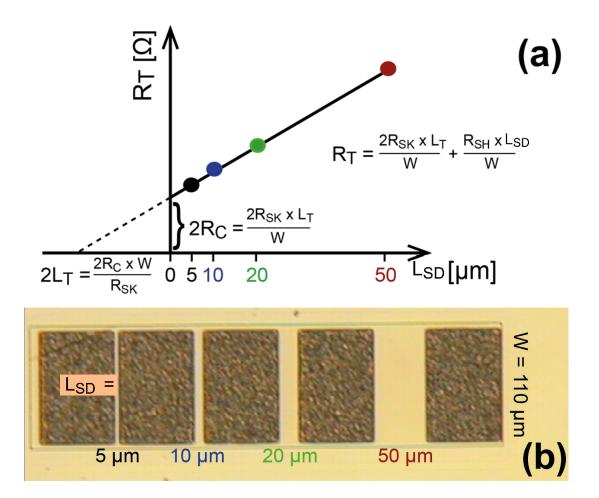

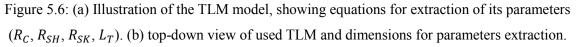

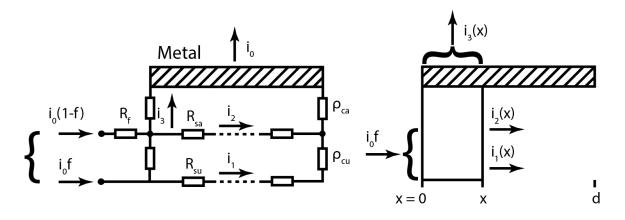

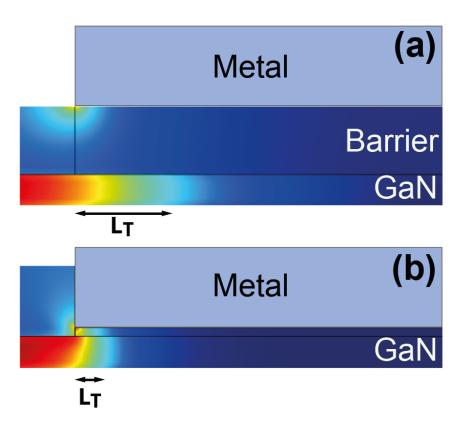

Figure 5.4: Illustration of alloy thickness under different etching depths. Greater quantity of Al beneath the metal results in less alloy thickness (a) 0%, (b) 25%, (c) 50%, (d) 75% and (e) 100% (not to scale).  $R_{SK}$  is the sheet resistance beneath the metal contact and  $R_{SH}$  is the sheet resistance outside of the contact area. 118

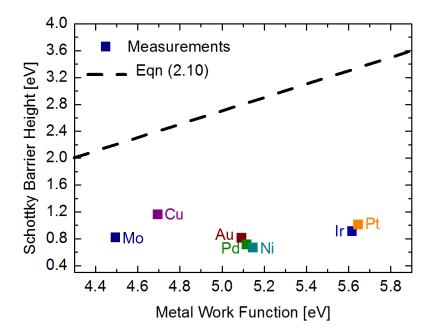

Figure 5.14: Relationship between Schottky barrier height and work function for various metals that are deposited on AlGaN layer obtained via I - V. No clear correlation is shown compared

| to theoretical results from Eqn (2.10) where $x_{Al_{0.3}Ga_{0.7}N} = 2.3 \text{ kJ mol}^{-1}$                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

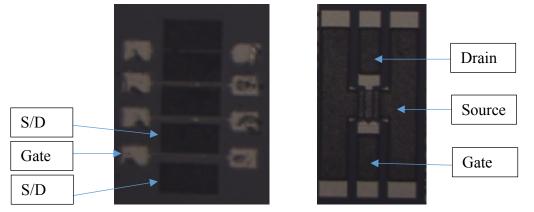

| Figure 5.15: Overview of AlGaN/GaN G-TLM (left) and HEMT (right)130                                                                                                                                                                                                                                          |

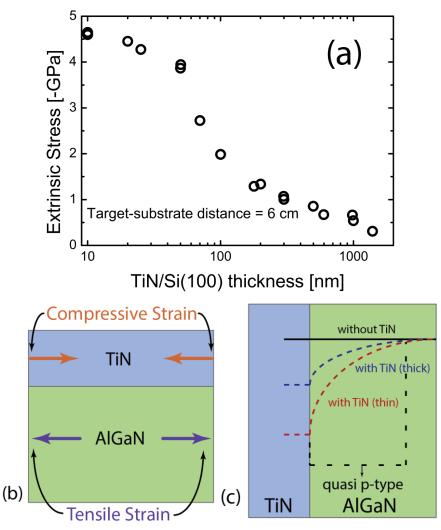

| Figure 5.16: (a) Impact of TiN thickness on extrinsic stress within TiN layer, (b) types of strain occurring within TiN and AlGaN layers, (c) strain gradient within AlGaN layer with thinner TiN layer that generates quasi p-type dopants                                                                  |

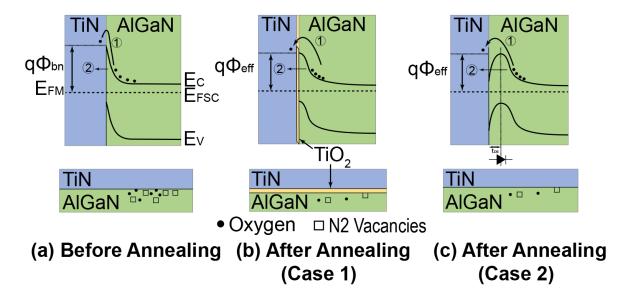

| Figure 5.17: Conduction mechanism of TiN Schottky contact on $Al_{0.32}Ga_{0.68}N/GaN$ HEMT (a) before annealing, (b) after annealing with TiO <sub>2</sub> layer, and (c) after annealing without TiO <sub>2</sub> layer, where $t_{DR}$ is the depletion region thickness Error! Bookmark not defined.     |

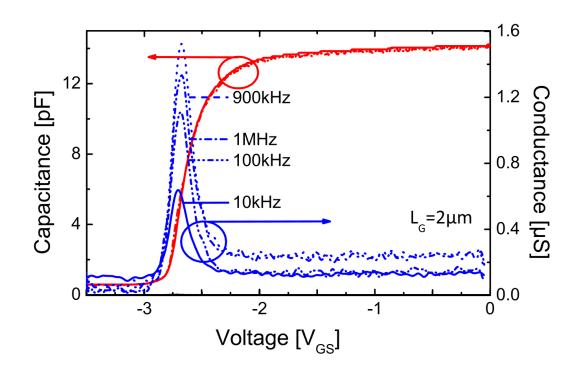

| Figure 5.18: Post-annealing C – V and G – V characteristics of AlGaN/GaN HEMT with new TiN Schottky contact metallisation and TiN thickness of 5 nm as a function of frequency from 10 kHz to 1 MHz                                                                                                          |

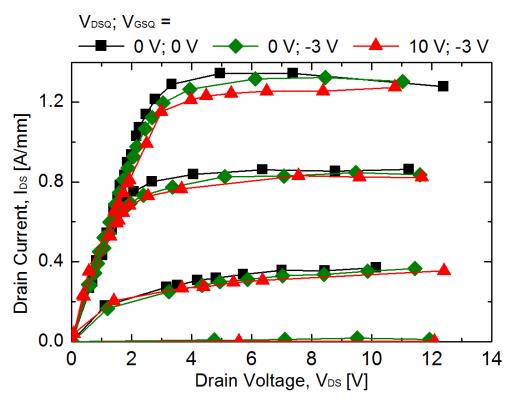

| Figure 5.19: Post-annealing I <sub>DS</sub> – V <sub>DS</sub> characteristics of AlGaN/GaN HEMT with new TiN         Schottky contact metallisation.       135                                                                                                                                               |

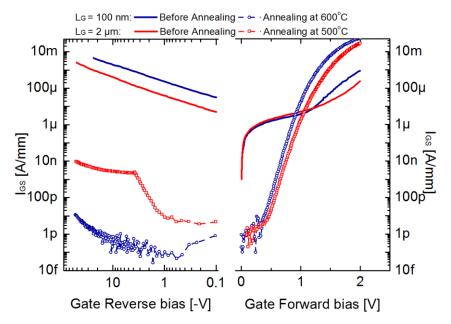

| Figure 5.20: $I_{GS} - V_{GS}$ measurement for different annealing temperature and gate length for TiN/Au Schottky contact and $W = 100 \ \mu m [227], [228]136$                                                                                                                                             |

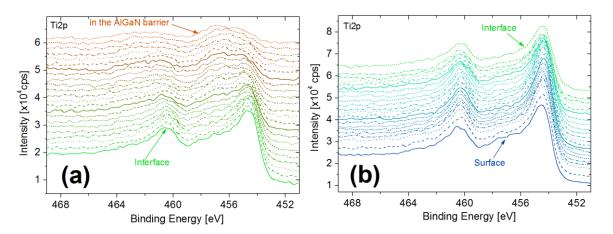

| Figure 5.21: Ti2p spectrum in the (a) AlGaN barrier layer and (b) TiN layer137                                                                                                                                                                                                                               |

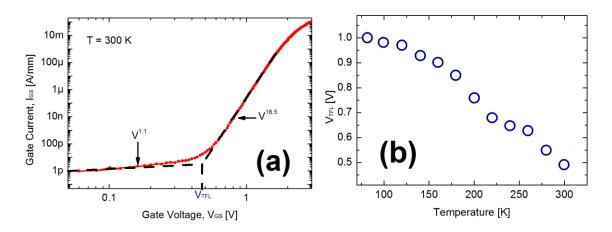

| Figure 5.22: (a) $I_{DS} - V_{GS}$ characteristics, showing a rectifying behaviour with two mechanisms of current increase as a result of quasi-P/N junction of TiN/AlGaN. (b) Reduction of $V_{TFL}$ with increased temperature, showing that these mechanisms impact the $I_{GS} - V_{GS}$ characteristics |

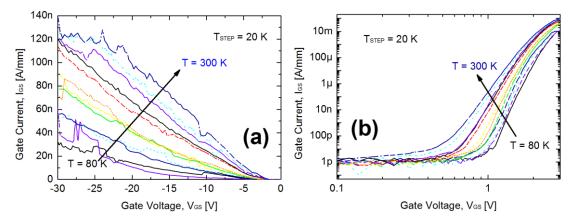

| Figure 5.23: Raw data of (a) reverse current and (b) forward current under various temperatures                                                                                                                                                                                                              |

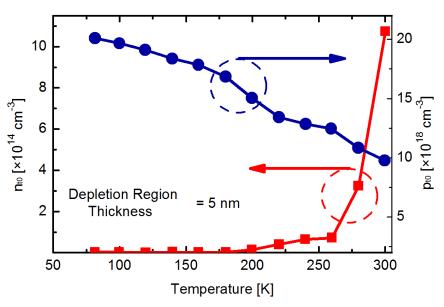

| Figure 5.24: Extracted n and p concentration using the model given in [229] with Figure 5.22(b) whilst assuming a depletion layer of 5 nm, showing Schottky diode characteristic                                                                                                                             |

Figure 5.25: Schematic diagram of simulated GaN-based HEMT showing (a) conventional AlGaN/GaN HEMT; (b) step-graded AlGaN barrier layer – Structure 1; (c) AlN spacer layer – Structure 2; (d) InGaN channel layer – Structure 3. For conventional AlGaN/GaN HEMT: x =

| 0.25; for Structure 1 – 3: $x_1 = 0.2$ , $x_2 = 0.35$ , $x_3 = 0.5$                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

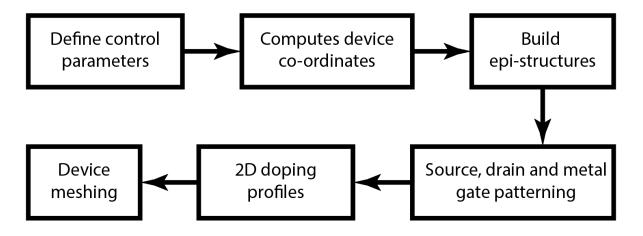

| Figure 5.26: Simulated structure formation flow for GaN-based HFET design142                                                                                                                                                                                                                                                                                        |

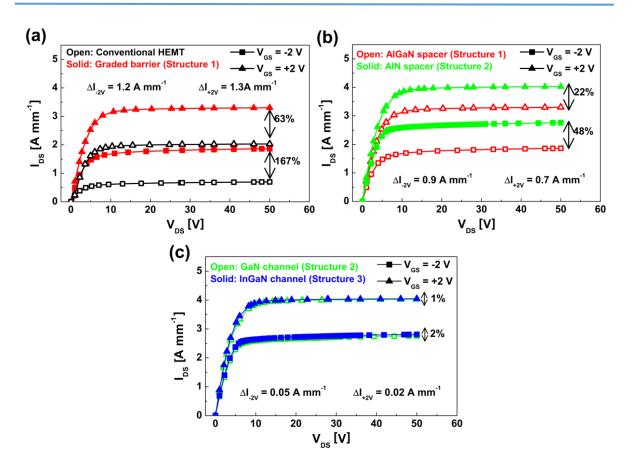

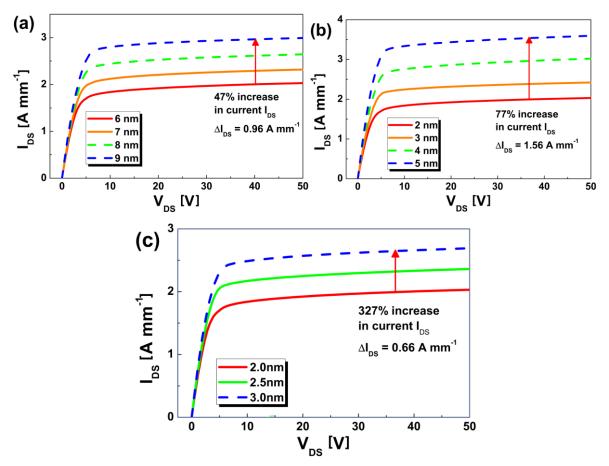

| Figure 5.27: $I_{DS} - V_{DS}$ characteristics at $V_{GS} = \pm 2 V$ for (a) conventional and step-graded AlGaN barrier HEMT (Structure 1); (b) AlN spacer HEMT (Structure 2); and (c) InGaN channel HEMT (Structure 3)                                                                                                                                             |

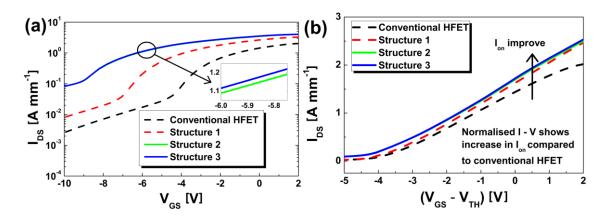

| Figure 5.28: (a) $I_{DS} - V_{GS}$ characteristics at $V_{DS} = 36$ V in logarithmic scale and (b) normalised $I_{DS}$ versus ( $V_{GS} - V_{TH}$ ) curves for all structures                                                                                                                                                                                       |

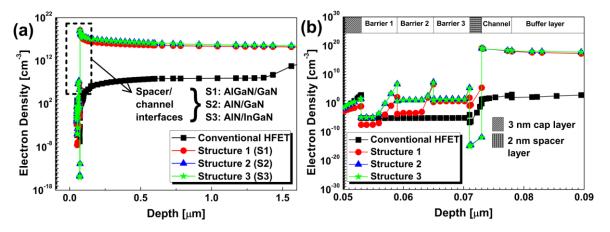

| Figure 5.29: (a) Depth profile for electron density for conventional AlGaN/GaN HEMT and Structures 1-3. (b) Closer visual focusing on the density at the interfaces from the depth of 50 nm and 90 nm                                                                                                                                                               |

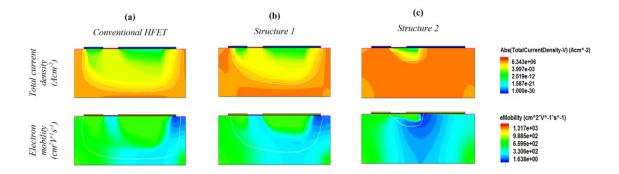

| Figure 5.30: Current density and electron mobility distribution for (a) conventional AlGaN/GaN HEMT; (b) Structure 1; and (c) Structure 2145                                                                                                                                                                                                                        |

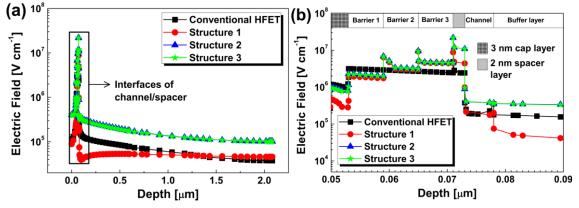

| Figure 5.31: (a) Depth profile of electric field for conventional AlGaN/GaN HEMT and Structures 1-3. (b) Closer visual focusing on the field at the interfaces from the depth of 50 nm and 90 nm                                                                                                                                                                    |

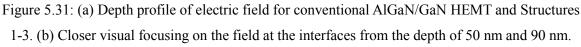

| Figure 5.32: (a) Depth profile of electron velocity for conventional AlGaN/GaN HEMT and Structures 1-3. (b) Closer visual focusing on the field at the interfaces from the depth of 50 nm and 90 nm                                                                                                                                                                 |

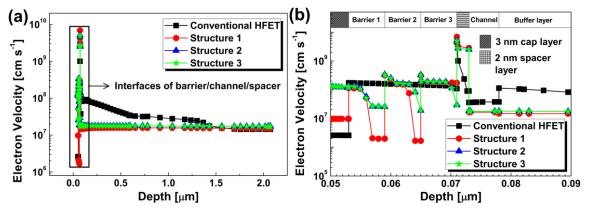

| Figure 5.33: Transfer characteristics at $V_{DS}$ = 36 V for various (a) barrier thickness, $t_{br}$ ; (b) spacer thickness, $t_{sp}$ ; and (c) buffer thickness, $t_{bf}$ of the final structure (Structure 3). Inset: extracted $V_{TH}$ and its trend compared with results of [243] and [244] with respect to $t_{br}$ , $t_{sp}$ , and $t_{bf}$ , respectively |

| Figure 5.34: Output characteristics at $V_{GS} = 2$ V for various (a) $t_{br}$ ; (b) $t_{sp}$ ; and (c) $t_{bf}$ of the final structure (Structure 3)                                                                                                                                                                                                               |

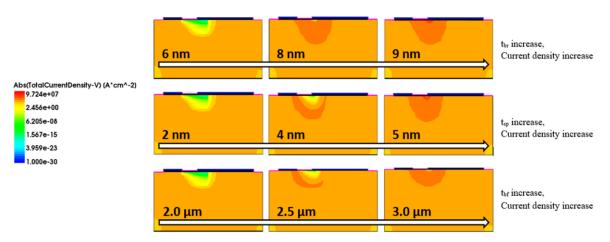

| Figure 5.35: Current density distributions at $V_{DS} = 36$ V for varying $t_{br}$ , $t_{sp}$ , and $t_{bf}$ in Structure 3                                                                                                                                                                                                                                         |

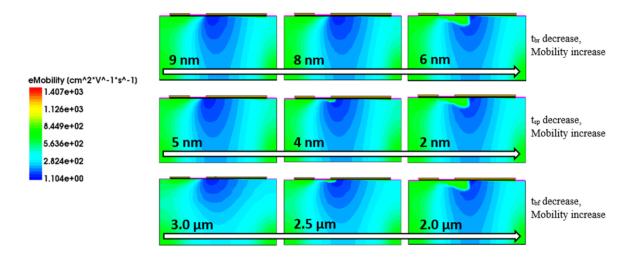

| Figure 5.36: Electron mobility distributions at $V_{DS} = 36$ V for varying $t_{br}$ , $t_{sp}$ , and $t_{bf}$ ;                                                                                                                                                                                                                                                    |

| Structure 315 | 50 |

|---------------|----|

|---------------|----|

| Figure A.2: Summit 12000-AP probing station using the Velox <sup>TM</sup> control software, Cascade                         |

|-----------------------------------------------------------------------------------------------------------------------------|

| DCM-210 micro-positioners and Cascade 154-001 radial probing needles                                                        |

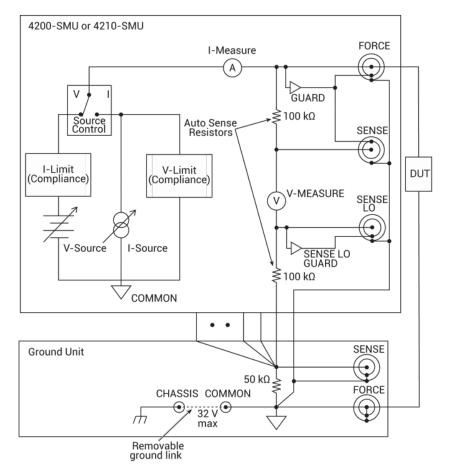

| Figure A.3: Basic block diagram of SMU source-measure configuration                                                         |

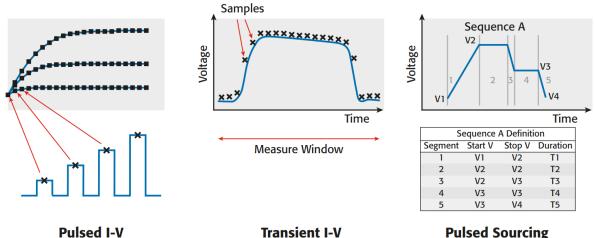

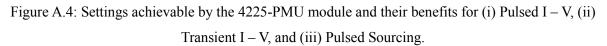

| Figure A.4: Settings achievable by the 4225-PMU module and their benefits for (i) Pulsed I –                                |

| V, (ii) Transient I – V, and (iii) Pulsed Sourcing                                                                          |

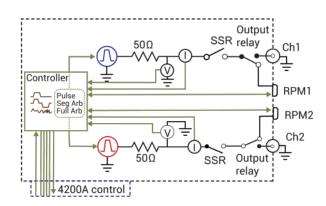

| Figure A.5: Block diagram of the 4225-PMU control system showing the connections between                                    |

| the Keithley 4200A-SCS and 4225-RPM                                                                                         |

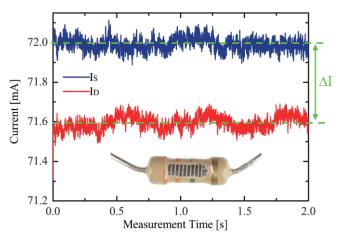

| Figure A.6: Transient $I_S$ and $I_D$ of a 180 $\Omega$ resistor at 13 V, showing the $I_S$ , $I_D$ offset, $\Delta I$ , is |

| persistently 0.4 mA                                                                                                         |

# LIST OF TABLES

| Table 1.1: A comparison of the material properties of GaN and other competitors in the semiconductor industry.         5                    |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Table 1.2: A comparison of the various Figures of Merit (FOM) for GaN and other         semiconductor competitors [26].                     |

| Table 2.1: Thermal conductivity at 300 K and fitting parameters for each substrate used to measure thermal conductivity behaviour.       23 |

| Table 2.2: Structural parameters for AIN and GaN                                                                                            |

| Table 2.3: Spontaneous polarisation parameters for AlN and GaN    24                                                                        |

| Table 2.4: A comparison of the relevant material properties of substrates typically used in         AlGaN/GaN based devices.       37       |

| Table 3.1: The fitting coefficients for GaN and AlN used in the relation (3.2). Note that the                                               |

| coefficient $\alpha_{\lambda}$ has units of W/mK while $\beta_{\lambda}$ is unitless                                                        |

| Table 4.1: Parametric values applied to RC Thermal Model                                                                                    |

| Table 5.1: The impact of annealing and passivation on Schottky barrier height, linearity and                                                |

| gate leakage for TiN thicknesses of 2.5 nm and 5 nm at $L_G = 2 \mu m$                                                                      |

| Table 5.2: The impact of annealing and passivation on Schottky barrier height, linearity and                                                |

| gate leakage for TiN thicknesses of 10 nm and 20 nm at $L_G = 2 \mu m$                                                                      |

| Table 5.3: The impact of annealing and passivation on Schottky barrier height, linearity and                                                |

| gate leakage for TiN thicknesses of 40 nm and 60 nm at $L_G = 2 \mu m.$                                                                     |

| Table 5.4: Parameters used for the simulation of devices.    141                                                                            |

| Table 5.5: Simulated results of DC characteristics for each device structure                                                                |

## **ABBREVIATIONS**

| μ-RTD                          | Micro-resistance thermal detector       |

|--------------------------------|-----------------------------------------|

| 2D                             | Two-dimensional                         |

| 2DEG                           | Two-dimensional electron gas            |

| ADC                            | Analog-to-digital converter             |

| Al                             | Aluminium                               |

| Al <sub>2</sub> O <sub>3</sub> | Sapphire                                |

| AlGaAs                         | Aluminium gallium arsenide              |

| AIN                            | Aluminium nitride                       |

| Ar                             | Argon                                   |

| Au                             | Gold                                    |

| В                              | Magnetic field                          |

| BE                             | Binding energy                          |

| BHFFOM                         | Baliga's high-frequency figure of merit |

| BL                             | Blue luminescence                       |

| CCD                            | Charge-coupled device                   |

| Cu                             | Copper                                  |

| DC                             | Direct current                          |

| DD                             | Drift-diffusion                         |

| DEG1                           | Fast degradation period                 |

| DEG2                           | Slow degradation period                 |

| DLTS                           | Deep-level transient spectroscopy       |

| DUT                            | Device under test                       |

| Ε                              | Electric field                          |

| EDS                            | Energy dispersive spectroscopy          |

| ET                             | Electro-thermal                         |

| FE                             | Field emission                          |

| FIB                            | Focus ion beam                          |

| FOM                            | Figure of merit                         |

| FWHM                           | Full width at half maximum              |

| Ga                             | Gallium                                 |

|                                |                                         |

| GaAs             | Gallium arsenide                                  |

|------------------|---------------------------------------------------|

| GaN              | Gallium nitride                                   |

| G-TLM            | Gate transmission line model                      |

| H <sub>2</sub> O | Water                                             |

| HEMT             | High electron mobility transistor                 |

| HF               | High frequency                                    |

| HNO <sub>2</sub> | Nitrous acid                                      |

| HP               | High purity                                       |

| HRTEM            | High-resolution transmission electron microscopy  |

| HR-XRD           | High-resolution x-ray diffraction                 |

| HVPE             | Hydride vapour phase epitaxy                      |

| IC               | Integrated circuit                                |

| III-N            | Group III-nitrides                                |

| I-limit          | Current limit                                     |

| InN              | Indium nitride                                    |

| IR               | Infrared                                          |

| JFOM             | Johnson's figure of merit                         |

| KFOM             | Keyes' figure of merit                            |

| LED              | Light emitting diode                              |

| MBE              | Molecular beam epitaxy                            |

| MESFET           | Metal-semiconductor field-effect transistor       |

| MIS              | Metal/interface layer/semiconductor               |

| MMIC             | Monolithic microwave integrated circuit           |

| Мо               | Molybdenum                                        |

| MOCVD            | Metal organic chemical vapour deposition          |

| MODFET           | Modulation-doped field-effect transistor          |

| MOSFET           | Metal-oxide-semiconductor field-effect transistor |

| MOVPE            | Metal-organic vapour-phase epitaxy                |

| MS               | Metal/semiconductor                               |

| Ν                | Nitrogen                                          |

| NH <sub>3</sub>  | Ammonia                                           |

| Ni               | Nickel                                            |

| <b>O</b> 2       | Oxygen                                            |

|                  |                                                   |

| PA CNTRL         | Preamp control                    |

|------------------|-----------------------------------|

| PL               | Photoluminescence                 |

| PMU              | Pulse measure unit                |

| Pt               | Platinum                          |

| RF               | Radio frequency                   |

| RL               | Red luminescence                  |

| RPM              | Remote pulse measure unit         |

| RTA              | Rapid thermal annealing           |

| S/D              | Source/drain                      |

| SAR              | Successive approximation register |

| SEM              | Scanning electron microscopy      |

| Si               | Silicon                           |

| SiC              | Silicon carbide                   |

| SiN              | Silicon nitride                   |

| SiO <sub>2</sub> | Silicon dioxide                   |

| SMU              | Source measure unit               |

| SRH              | Schottky-read-hall                |

| TCAD             | Technology computer-aided design  |

| ТЕ               | Thermionic emission               |

| TFE              | Thermionic field emission         |

| Ti               | Titanium                          |

| TLM              | Transmission line model           |

| TLTLM            | Tri-layer transmission line model |

| UV               | Ultra-violet                      |

| V-limit          | Voltage limit                     |

| XPS              | X-ray photoelectron spectroscopy  |

| XRD              | X-ray diffraction                 |

| YL               | Yellow luminescence               |

|                  |                                   |

# **PHYSICAL CONSTANTS**

| c  | Speed of light     | $(3 \times 10^8 \text{ m s}^{-1})$                                   |

|----|--------------------|----------------------------------------------------------------------|

| h  | Planck's constant  | $(6.626 \times 10^{-34} \text{ m}^2 \text{kg s}^{-1})$               |

| kв | Boltzmann constant | $(1.381 \times 10^{-23} \text{ m}^2 \text{kg s}^{-2} \text{K}^{-1})$ |

| q  | Charge of electron | $(1.602 \times 10^{-19} \text{ C})$                                  |

# Symbols

| а                                 | Basal plane edge length                                                                                 |

|-----------------------------------|---------------------------------------------------------------------------------------------------------|

| $a_{bf}$                          | in-plane lattice constant of the buffer                                                                 |

| a <sub>sub</sub>                  | in-plane lattice constant of the substrate                                                              |

| <b>A</b> *                        | Effective richardson constant                                                                           |

| $A_n$                             | Model parameter specific to semiconductor material used                                                 |

| b                                 | Bowing parameter                                                                                        |

| <i>c</i> <sub>0</sub>             | Ideal unit height of crystal cell                                                                       |

| C <sub>13</sub> , C <sub>33</sub> | Elastic constant                                                                                        |

| <i>C</i> <sub><i>H</i></sub>      | Heat capacitance per unit volume                                                                        |

| C <sub>TH</sub>                   | Thermal capacitance                                                                                     |

| d                                 | Distance between devices                                                                                |

| <i>E</i> <sub>00</sub>            | Characteristic energy related to the transmission probability of the carrier through a Schottky barrier |

| E <sub>C</sub>                    | Conduction band energy                                                                                  |

| $E_{BD}$                          | Breakdown electric field                                                                                |

| E <sub>crit</sub>                 | Critical electric field                                                                                 |

| $E_F$                             | Fermi level                                                                                             |

| E <sub>FM</sub>                   | Metal Fermi level                                                                                       |

| $E_g$                             | Bandgap                                                                                                 |

| $E_T$                             | Trap energy                                                                                             |

| E <sub>TC</sub>                   | Carbon trap energy                                                                                      |

| $\boldsymbol{E}_{TI}$             | Iron trap energy                                                                                        |

| $E_V$                             | Valence band energy                                                                                     |

| f                                 | Current division factor                                                                                 |

| f <sub>max</sub>                  | Maximum oscillating frequency                                                                           |

| $f_T$                             | Gain cut-off frequency                                                                                  |

| G                                 | Conductance                                                                                             |

| G <sub>c</sub>                    | Carrier generation rate                                                                                 |

| $G_m$                             | Extrinsic transconductance                                                                              |

| Н                                 | Heat generation                                                                                         |

| Ι                                 | Current                                                                                                 |

|                                   |                                                                                                         |

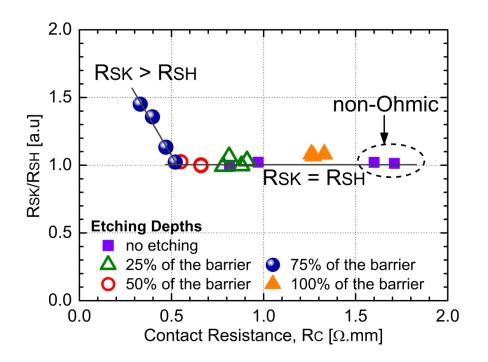

| <i>i</i> <sub>1</sub>             | Lateral current distribution at the alloy/AlGaN interface                                       |

|-----------------------------------|-------------------------------------------------------------------------------------------------|

| <i>i</i> <sub>2</sub>             | Lateral current distribution at the metal/alloy interface                                       |

| <b>i</b> <sub>3</sub>             | Current collected by the metal layer of the contact                                             |

| I <sub>DS</sub>                   | Drain-source current                                                                            |

| <b>I</b> <sub>leakage</sub>       | Gate leakage current                                                                            |

| I <sub>OFF</sub>                  | OFF-state current                                                                               |

| I <sub>ON</sub>                   | ON-state current                                                                                |

| I <sub>RTD</sub>                  | Current through µ-resistance thermal detector                                                   |

| <b>j</b> <sub>n</sub>             | Current density of electrons                                                                    |

| j <sub>p</sub>                    | Current density of holes                                                                        |

| L                                 | Distance between ohmic contacts                                                                 |

| L <sub>G</sub>                    | Gate contact length                                                                             |

| L <sub>GD</sub>                   | Gate-to-drain distance                                                                          |

| L <sub>SD</sub>                   | Source-to-drain distance                                                                        |

| L <sub>SG</sub>                   | Source-to-gate distance                                                                         |

| $L_T$                             | Transfer length                                                                                 |

| $m_e^*$                           | Electron effective mass                                                                         |

| n                                 | Electron concentration                                                                          |

| N <sub>crit</sub>                 | Doping concentration when the mobility reaches the average value of $\mu_{max}$ and $\mu_{min}$ |

| N <sub>B</sub>                    | Impurity density concentration                                                                  |

| N <sub>D</sub>                    | Donor concentration                                                                             |

| $n_s$                             | Electron sheet density                                                                          |

| p                                 | Hole concentration                                                                              |

| Р                                 | Power density                                                                                   |

| <b>P</b> <sub>DISS</sub>          | Dissipated Power                                                                                |

| $p_g$                             | Arbitrary band-gap energy parameter                                                             |

| $\boldsymbol{P}_{\boldsymbol{n}}$ | Thermoelectric power of electron                                                                |

| $P_p$                             | Thermoelectric power of hole                                                                    |

| $\boldsymbol{P}_{PE}$             | Piezoelectric polarisation                                                                      |

| P <sub>SP</sub>                   | Spontaneous polarisation                                                                        |

| r                                 | Strain relaxation                                                                               |

| R                                 | Bulk recombination rate of carriers                                                             |

|                                   |                                                                                                 |

| $R_{\Box}$              | Sheet resistance                                        |

|-------------------------|---------------------------------------------------------|

| R <sub>C</sub>          | Ohmic contact resistance                                |

| $R_f$                   | Resistance of the alloy sidewall of the Ohmic contact   |

| <b>R</b> <sub>OFF</sub> | OFF-state resistance                                    |

| R <sub>ON</sub>         | ON-state resistance                                     |

| $R_{sa}$                | Sheet resistance of the metal/alloy interface           |

| R <sub>SH</sub>         | Sheet resistance outside of the Ohmic contact area      |

| R <sub>SK</sub>         | Sheet resistance beneath the metal of the Ohmic contact |

| R <sub>su</sub>         | Sheet resistance of the alloy/semiconductor interface   |

| $R_T$                   | Total resistance                                        |

| R <sub>TH</sub>         | Thermal resistance                                      |

| S                       | Metal contact area                                      |

| t                       | Time                                                    |

| $t_{br}$                | Thickness of step-graded barrier layer                  |

| t <sub>bf</sub>         | Thickness of buffer layer                               |

| $t_E$                   | Pulse edge time                                         |

| t <sub>t</sub>          | Wafer thickness                                         |

| t <sub>D</sub>          | Alloy depth                                             |

| t <sub>sp</sub>         | Thickness of spacer layer                               |

| $t_W$                   | Pulse width                                             |

| Τ                       | Temperature                                             |

| T <sub>CH</sub>         | Channel temperature                                     |

| T <sub>L</sub>          | Local lattice temperature                               |

| V <sub>BD</sub>         | Breakdown voltage                                       |

| V <sub>D</sub>          | Drain voltage                                           |

| V <sub>DF</sub>         | OFF-state drain voltage                                 |

| V <sub>DM</sub>         | ON-state drain voltage                                  |

| V <sub>DS</sub>         | Drain-source voltage                                    |

| V <sub>GF</sub>         | OFF-state gate voltage                                  |

| V <sub>GM</sub>         | ON-state gate voltage                                   |

| V <sub>H</sub>          | Hall voltage                                            |

| <i>V</i> <sub>m</sub>   | Metal voltage                                           |

| V <sub>S</sub>          | Source voltage                                          |

|                         |                                                         |

| $v_{sat}$                                  | Saturation velocity                                              |

|--------------------------------------------|------------------------------------------------------------------|

| V <sub>SC</sub>                            | Semiconductor voltage                                            |

| V <sub>TH</sub>                            | Threshold voltage                                                |

| W                                          | Metal contact width                                              |

| WF                                         | Metal work function                                              |

| x                                          | Aluminium concentration percentage                               |

| x <sub>AlGaN</sub>                         | Electron affinity of AlGaN                                       |

| α                                          | Lattice constant of semiconductor material                       |

| $lpha_g$ , $oldsymbol{eta}_g$              | Empirical constant for GaN                                       |

| $\alpha_{\lambda}, \beta_{\lambda}$        | Fitting coefficient                                              |

| β,γ,δ                                      | Temperature dependent coefficient                                |

| ΔΤ                                         | Temperature rise                                                 |

| 8                                          | Strain within semiconductor material                             |

| ${m {m arepsilon}}_{13}, {m m m eta}_{33}$ | Piezoelectric coefficient                                        |

| ${m arepsilon}_r$                          | Semiconductor dielectric constant                                |

| η                                          | Ideality factor of Schottky contact                              |

| λ                                          | Thermal conductivity                                             |

| μ                                          | Electron mobility                                                |

| ρ                                          | Resistivity of semiconductor material                            |

| $ ho_c$                                    | Specific contact resistivity                                     |

| $ ho_{ca}$                                 | Specific contact resistance of the metal/alloy interface         |

| $\rho_{cu}$                                | Specific contact resistance of the alloy/semiconductor interface |

| $\sigma V_g$                               | Schottky gate voltage                                            |

| $	au_i$                                    | Thermal time constant                                            |

| $\Phi_{bn}$                                | Schottky barrier height                                          |

| $\Phi_{MG}$                                | Metal work-function                                              |

| $\Phi_n$                                   | Quasi-fermi level of electron                                    |

| $\mathbf{\Phi}_p$                          | Quasi-fermi level of hole                                        |

|                                            |                                                                  |

### CHAPTER 1

## INTRODUCTION

| 1.1.          | BAC  | KGROUND                              | 2  |

|---------------|------|--------------------------------------|----|

| 1.1           | .1.  | History of GaN Technology            | 2  |

| 1.1           | .2.  | Why GaN Technology?                  | 4  |

| 1.1           | .3.  | GaN Applications and Market          | 6  |

| 1.1           | .4.  | Figures of Merit                     | 7  |

| 1. <b>2</b> . | Rati | ONALE                                | 9  |

| 1.3.          | Rese | ARCH AIM AND OBJECTIVES              | 9  |

| 1.4.          | Org  | ANISATION                            | .0 |

| 1.5.          | Oric | GINAL CONTRIBUTION TO RESEARCH FIELD | .2 |

Since the fabrication of the first silicon (Si) device in 1958 by Gibbons' Stanford laboratory [1], Si-based devices have been, by far, the most widely used technology in the semiconductor industry. The Si metal-oxide-semiconductor field effect transistor (MOSFET) has been the primary driver for the growth of the industry. However, Si MOSFETs have reached their limit in terms of power density, mobility and efficiency [2]–[8]. Also, scaling of these devices will reach its theoretical limit in the coming years as a result of the intrinsic material properties such as: (i) low breakdown voltage, (ii) low saturation velocity, (iii) low inversion layer mobility, and (iv) high device resistance [9]. To account for these limitations, several new semiconductor materials have been developed to accommodate the increasing need for devices that can provide higher output power at higher operating voltages and higher operating frequencies. In particular, III-nitride semiconductors such as gallium nitride (GaN) have gained significant attention in accommodating this need due to their superior material properties.

#### 1.1. Background

To begin our investigation into III-N-based devices, we firstly advanced our knowledge in the development of GaN technology since its discovery; this includes the use of GaN technology applications and market. The importance of GaN in these applications has been shown through a comparison with other competing semiconductor materials using a range of Figures of Merit (FOMs).

#### 1.1.1. History of GaN Technology

Since the discovery of Gallium (Ga) in 1897, the use cases of the newly found material were minimal. The introduction to the most widely used Ga compound in application today was not developed until 1930, where the first synthesis of GaN was produced [10]. Interest in the new compound did not reach any significance until 1938, where a technique was to powder GaN, producing small needles and platelets in order to investigate its crystal structure and lattice constant [11]. Successful and notable research into the development of GaN from this point did not arise until 1969, when the first deposition of GaN was produced using Hydride Vapour Phase Epitaxy (HVPE) [12]. Soon after, in 1971, the first GaN light emitting diode (LED) was fabricated [13]. This is the beginning of a large growth in the GaN market in industrial applications. The reason this development was so crucial to the market is that GaN is one of

few semiconductor materials that is capable of emitting blue light. This development is important as the optical applications of GaN are the driving force of the GaN market, even today.

The idea of a high-electron mobility transistor (HEMT) was introduced in 1980 with the aluminium gallium arsenide-on-gallium arsenide (AlGaAs/GaAs) HEMT [14]. The novelty of this structure is that two materials of different bandgaps are incorporated into the device structure to form a channel as opposed to the structure of an inversion layer device. This new structure introduced the idea of dopant injection prevention in the semiconductor material that would cause device damage, thereby reducing device mobility and reliability. It was only in 1991 that GaN technology caught up with this newly discovered structure. Here, the rapid progression in the development of GaN began when the first normally-ON AlGaN/GaN HEMT was produced via metal organic chemical vapour deposition (MOCVD) [15]. A crucial property to GaN's success today was also discovered in 1991 from this structure as a result of the technological improvements towards wafer production under high temperature. A high electron density channel at the AlGaN/GaN interface, known as the two-dimensional electron gas (2DEG) was also discovered in 1991. From this point on, rapid progression and interest was gained by academic research and industry in the development of GaN. A notable milestone was achieved in the GaN industry in 2000, when AlGaN/GaN HEMT technology was successfully grown on Si substrates via MOCVD [16]. The first normally-OFF GaN based modulationdoped field-effect transistor (MODFET) was fabricated in 1995 [17], although, the first patent involving normally-OFF GaN-based devices was not submitted until 2001 [18].

More recent developments came in 2007, when Toshiba developed a new GaN HEMT that operates at Ku-band (12 GHz to 18 GHz) that achieved 65.4 W at 14.5 GHz [19]. This technology was to add an n-GaN cap layer to an AlGaN/GaN HEMT grown on silicon carbide (SiC). Transphorm established the first qualified 600 V GaN-on-SiC device in 2009 and 600 V GaN-on-Si in 2010 [20]. Also in 2010, the first commercially available GaN power device was introduced by International Rectifier. At this point, a highly sophisticated, ultra fast monolithic microwave integrated circuit (MMIC), matched to a multi-switch monolithic GaN-based power device, was produced, doubling the switching speed of state-of-the-art silicon-based integrated power stage devices [21]. This was the highest operating voltage observed for GaN HEMTs at

the time. From then, adoption of GaN-based technology exponentially increased as GaN became a viable solution for more applications. Soon after, in 2012, a merge in operations between Fujitsu Semiconductor and Transphorm occurred. From then on, many new applications were introduced into the market with the new 600 V GaN device platform such as the world's first photovoltaic power conditioner, ultra-small AC adapters, highly efficient motion control, high-density power supplies for personal computers, servers and telecoms equipment, and many more [22].

#### 1.1.2. Why GaN Technology?

GaN is a material that is used in the production of many semiconductor applications that are later described. The technology has demonstrated that it is significantly more capable than the commonly used Si devices for a range of applications. The limitation of Moore's Law for Si devices prevents the increase of power capabilities of Si [23]. Therefore, GaN is the new emerging technology that can overcome the power and frequency limitations of Si. With its ability to conduct a much higher density of electrons at higher velocity, all at a low production cost, GaN-based devices are increasing its value in the semiconductor industry [24], [25]. The following presents a current list of exceptional properties that are responsible for the success of GaN technology:

• A large breakdown field is achieved from the large bandgap of GaN, which is particularly useful for high power applications. The relationship between the critical field,  $E_{crit}$ , and bandgap,  $E_g$ , is given by [26]:

$$E_{crit} = 1.02 \times 10^7 \sqrt{\frac{q}{\varepsilon_r}} N_B^{1/8} E_g^{3/4}$$

(1.1)

Where q is the charge of an electron,  $\varepsilon_r$  is the permittivity of GaN,  $N_B$  is the impurity density concentration.

• The high electron saturation velocity of GaN,  $v_{sat} \approx 1.7 \times 10^7$  cm s<sup>-1</sup> at 300 K, is a particularly desired parameter for high frequency applications. This is a temperature dependent parameter that is enhanced considerably in AlGaN/GaN HEMTs, to be explained in Section 2.1.2. However, for bulk semiconductor materials,  $v_{sat}$  is calculated by:

$$v_{sat}(T_L) = \frac{v_{sat,300K}}{(1 - A_n) + A_n \cdot \left(\frac{T_L}{300}\right)}$$

(1.2)

where  $v_{sat,300K}$  is the electron saturation velocity at 300 K,  $A_n$  is a model parameter specific to the semiconductor material used, and  $T_L$  is the lattice temperature.

- GaN has the ability to operate under extreme temperatures (up to 700 °C) [27], [28] when formed into a HEMT structure. Along with their high-frequency and high-power capabilities, this is significantly beneficial for harsh environments.

- High quality GaN-based devices can be grown onto large diameter Si substrates. As a result, GaN production costs are considerably low and can be integrated onto many Si applications.

- GaN is a direct band gap material where no additional energy is required to recombine into excitons. This is particularly useful for oscillator, amplifier and photovoltaic applications. The bandgap of GaN (3.4 eV) allows for photons of around 450 nm wavelength (blue light) to be emitted upon recombination of electrons and holes [29], which allows GaN to be used as a blue LED. The bandgap is conveniently in the ultraviolet (UV) region which means that electrons in the GaN bulk excite to the conduction

| Property                                                                          | GaN<br>(AlGaN/GaN) | Si   | 4H-SiC | GaAs |

|-----------------------------------------------------------------------------------|--------------------|------|--------|------|

| Bandgap,<br><i>E</i> <sub>g</sub> (eV)                                            | 3.4                | 1.1  | 3.3    | 1.4  |

| Breakdown electric field,<br><i>E<sub>BD</sub></i> (MV cm <sup>-1</sup> )         | 2.0<br>(5.6)       | 0.3  | 3.0    | 0.4  |

| Electron mobility,<br>μ (cm <sup>2</sup> V <sup>-1</sup> .s <sup>-1</sup> )       | 900<br>(2000)      | 1400 | 700    | 8500 |

| Electron saturation velocity,<br>$v_{sat}$ (×10 <sup>7</sup> cm s <sup>-1</sup> ) | 1.5<br>(2.5)       | 1.0  | 2.0    | 2.0  |

| Thermal conductivity,<br>$\lambda$ (W cm <sup>-1</sup> .K <sup>-1</sup> )         | 1.5                | 1.5  | 5.0    | 0.5  |

| Dielectric constant, $\mathcal{E}_r$                                              | 8.9                | 11.7 | 10.0   | 12.9 |

Table 1.1: A comparison of the material properties of GaN and other competitors in the semiconductor industry.

5

band when exposed to UV light with >364 nm wavelength. This makes them exceptionally good as UV detectors.

In addition, a comparison of the fundamental material properties of Si, GaN, 4H hexagonal polytype Silicon Carbide (SiC), and GaAs is shown in [30], [31]. Although GaAs needs doping to operate as a device, the mobility provided is for undoped GaAs and, hence, is significantly larger than if it were doped. These properties allow GaN-based devices to operate under high temperature and high pressure environments where Si devices are incapable of functioning. To note, AlGaN/GaN-based devices have enhanced properties whereby  $\mu$  is increased to 2000 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> and  $v_{sat}$  is increased to 2.5 × 10<sup>7</sup> cm s<sup>-1</sup>.

#### 1.1.3. GaN Applications and Market