## LJMU Research Online

Manut, A, Gao, R, Zhang, JF, Ji, Z, Mehedi, M, Vigar, D, Asenov, A and Kaczer, B

Trigger-When-Charged: A technique for directly measuring RTN and BTIinduced threshold voltage fluctuation under use-Vdd

http://researchonline.ljmu.ac.uk/id/eprint/10019/

Article

**Citation** (please note it is advisable to refer to the publisher's version if you intend to cite from this work)

Manut, A, Gao, R, Zhang, JF, Ji, Z, Mehedi, M, Vigar, D, Asenov, A and Kaczer, B (2019) Trigger-When-Charged: A technique for directly measuring RTN and BTI-induced threshold voltage fluctuation under use-Vdd. IEEE Transactions on Electron Devices. 66 (3). pp. 1482-1488. ISSN 0018-9383

LJMU has developed LJMU Research Online for users to access the research output of the University more effectively. Copyright © and Moral Rights for the papers on this site are retained by the individual authors and/or other copyright owners. Users may download and/or print one copy of any article(s) in LJMU Research Online to facilitate their private study or for non-commercial research. You may not engage in further distribution of the material or use it for any profit-making activities or any commercial gain.

The version presented here may differ from the published version or from the version of the record. Please see the repository URL above for details on accessing the published version and note that access may require a subscription.

For more information please contact <a href="mailto:researchonline@ljmu.ac.uk">researchonline@ljmu.ac.uk</a>

http://researchonline.ljmu.ac.uk/

# Trigger-When-Charged: A technique for directly measuring RTN and BTI-induced threshold voltage fluctuation under use-Vdd

A. Manut, R. Gao, J. F. Zhang, Z. Ji, M. Mehedi, W. Zhang, D. Vigar, A. Asenov, and B. Kaczer

Abstract — Low power circuits are important for many applications, such as IoT. Device variations and fluctuations are challenging their design. Random telegraph noise (RTN) is an important source of fluctuation. To verify a design by simulation, one needs assessing the impact of fluctuation in both driving current,  $\Delta Id$ , and threshold voltage,  $\Delta V$ th. Many early works, however, only measured RTN-induced AId. AVth was not directly measured because of two difficulties: its average value is low and it is highly dynamic. Early works often estimated  $\Delta V$ th from  $\Delta Id/gm(Vg=Vdd)$ , where gm is trans-conductance, without giving its accuracy. The objective of this work is to develop a new Trigger-When-Charged (TWC) technique for directly measuring the RTN-induced  $\Delta V$ th. By triggering the measurement only when a trap is charged, measurement accuracy is substantially improved. It is found that there is a poor correlation between  $\Delta Id/gm(Vg=Vdd)$  and the directly measured  $\Delta V$ th(Vg=Vth). The former is twice of the latter on average. The origin for this difference is analyzed. For the first time, the TWC is applied to evaluate device-to-device variations of the directly measured RTN-induced  $\Delta V$ th without selecting devices.

Index terms: Random telegraph noise (RTN), Fluctuations, Yield, Within-a-device-fluctuation, Jitters, Positive charges, NBTI.

#### I. INTRODUCTION

A s CMOS nodes scale down, the fluctuations induced by random charge-discharge of traps scale up. Smaller devices have larger statistical spread because of fewer traps per device and the larger impact of a single charge on them [1,2]. The increased number of devices per chip also leads to larger statistical spread [1,2] and high data transmission rate requires tight control of fluctuations [3]. Fluctuations have become a major concern for circuit design and have attracted many attentions recently [4-20]. It has been reported that current fluctuation in some fresh devices can be over the typical device lifetime criterion of 10% [5].

Fluctuations are commonly observed as the random telegraph noise (RTN) in the drain current,  $\Delta Id$ , under a given

gate bias, Vg, and early works [5-13] have focused on them.  $\Delta$ Id allows probing individual traps and an analysis of their mean capture and emission time dependence on Vg gives the trap energy and spatial locations [5, 6, 8, 10]. This has improved our understanding substantially. There are, however, little direct measurements of the RTN-induced fluctuation in threshold voltage,  $\Delta$ Vth. This is because its measurement is difficult: the charge-discharge of traps for RTN is highly dynamic and the average  $\Delta$ Vth is typically low. As a result, the RTN-induced  $\Delta$ Vth often was either not given [5,11] or estimated from dividing  $\Delta$ Id by trans-conductance, i.e.  $\Delta$ Vth $\approx\Delta$ Id/gm(Vdd) [6-10]. The accuracy of the  $\Delta$ Vth evaluated in this way was not given in these works [6-10].

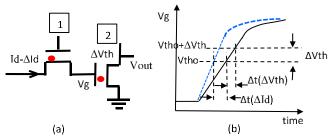

To model the impact of RTN on the margin of SRAM [15] and the timing error [14], one needs both  $\Delta Id$  and  $\Delta Vth$ . For example, RTN in the pass transistor 1 in Fig. 1a can reduce the driving current by  $\Delta Id$  and slow down the Vg rise of transistor 2 in reaching its threshold voltage, Vtho, by  $\Delta t(\Delta Id)$ . RTN in the transistor 2 can increase its Vth by  $\Delta Vth$  and results in a further delay,  $\Delta t(\Delta Vth)$ . There is a need to obtain both accurate  $\Delta Id$  and  $\Delta Vth$ , therefore.

Fig. 1. A schematic illustration of the impact of  $\Delta Id$  and  $\Delta V$ th on timing: (a) circuits and (b) waveform. Vout switches when Vg $\approx$ Vth, which is delayed by a lower charging current, Id- $\Delta Id$ , supplied through the transistor 1 and a higher Vth=Vth0+ $\Delta$ Vth of the transistor 2.

The objective of this work is to develop a new Trigger-When-Charged (TWC) technique for directly measuring the RTN-induced  $\Delta$ Vth. By ensuring that the measurement is taken when traps are charged, the accuracy is substantially improved. It is found that the  $\Delta$ Id/gm(Vdd) correlates poorly with the directly measured  $\Delta$ Vth and the former doubles the latter on

Manuscript received MMM DDD, YYYY. This work was supported by the Engineering and Physical Science Research Council of UK under the grant no. EP/L010607/1. The review of this paper was arranged by Editor Z. Çelik-Butler (Corresponding author: R. Gao and J. F. Zhang)

A. Manut, R. Gao, J. F. Zhang, Z. Ji, M. Mehedi, W. Zhang, are with the Department of Electronics and Electrical Engineering, John Moores University, Liverpool L3 3AF, UK. A.Manut now is with Faculty of Electrical Engineering, Universiti Teknologi MARA Selangor, 40450 Shah Alam, Malaysia.

D. Vigar is with Qualcomm Technologies International Ltd., Cambridge CB4 0WZ, U.K.

A. Asenov is with the Department of Electronics and Electrical Engineering, University of Glasgow, Glasgow, G12 8QQ, U.K.

B. Kaczer is with Imec, B-3001 Leuven, Belgium.

average. The discrepancy originates partly from the device-todevice variation (DDV) of relative local current density beneath a trap at Vg=Vth [16-19] and partly from the charge-induced mobility degradation [20].

Some deeply scaled devices have analyzable RTN signals in terms of extracting mean capture/emission time [11], while others can have a complex within-a-device-fluctuation [12]. The latter was deselected in some early works [10,13,16,17], making the real DDV of fluctuation unobtainable. The TWC developed in this work is applicable to devices with or without analyzable RTN signals and it will be used to evaluate the DDV.

### II. DEVICES AND MEASUREMENT TECHNIQUE

#### A. Devices

The MOSFETs used in this work were fabricated by a 28 nm commercial CMOS process with a use Vdd of 0.9 V. They have a metal gate and a high-k dielectric stack with an equivalent oxide thickness of 1.2 nm. The channel width and length are 135 nm and 27 nm, respectively. For comparison purpose, large devices of  $3 \times 1 \ \mu m$  were also used, which has insignificant DDV. All tests were performed at 125 °C.

#### B.TWC technique

Difficulties with standard measure-stress-measure methods: For ageing-induced  $\Delta$ Vth under stresses such as negative bias temperature instability (NBTI) [21,22] and hot carriers [23,24], the degradation is commonly measured at preset time. This is acceptable, as the Vg-acceleration used in the stress generally leads to a large-enough  $\Delta$ Vth that is measurable and deterministic at a preset time. There are, however, two difficulties in applying this method to deeply scaled devices under use-Vdd, where  $\Delta$ Vth mainly exhibits as Random Telegraph Noise (RTN). First, there are only a few active traps and the average  $\Delta$ Vth is typically low. Second, chargedischarge of these traps are highly dynamic: they are often neutral at the preset time for measurement, as shown by the red circle symbols in Fig. 2, and would be missed by the measurement.

One way to avoid these difficulties is selecting devices that only have one trap, which induces a high enough  $\Delta V$ th (e.g. 20 mV) and its emission time is long enough (e.g. >1 sec) for completing the measurement [16,17]. This has improved our understanding of the interaction between a trap and the current. Such devices, however, are rare (e.g. ~10% [16]) and the required device selection precludes obtaining real DDV. The present work develops a new technique that removes the device selection and is applicable to all devices, so that the real DDV can be extracted.

<u>Test procedure of TWC technique:</u> Fig. 2a gives the Vg waveform. After recording the reference Id-Vg on a fresh device, the test starts by a 'stabilization' period of 40 sec under Vg=Vdd=-0.9 V. If there are any traps at deep energy level in a device, they will be filled during this period [25].  $\Delta$ Id under

Vg=-0.9 V is then monitored for a period, e.g. 100 sec, as marked by 'Id monitor' in Fig. 2a. A sampling rate of 1 M/sec was used [26]. The trapping-induced up-envelope (UE) of  $\Delta$ Id is obtained.

To measure the trapping-induced  $\Delta V$ th, one must ensure that the measurement was taken when the traps are charged. This is achieved by setting the trigger level of the oscilloscope and the pulse generator for Vg just below the UE, as shown in Figs. 2a&b. Once triggered, the pulse Id-Vg (p-IV) is recorded in 3 µs to minimize discharge [25,26].

Although a sampling rate of 1 M/sec can be used to monitor  $\Delta$ Id under a fixed Vg=-0.9 V, it only gives 3 points in 3 µs and is too slow for the p-IV. To have sufficient number of points for p-IV, a higher rate of 100 M/sec is used. The p-IV was repeatedly measured for 50 times and their average is used to reduce the system noise to ~1 mV.

Fig. 2. The TWC technique. (a) Test procedure: After a stabilization period, the RTN-induced  $\Delta Id$  is monitored under Vg=Vdd and the upper envelope (UE) is determined. The trigger-level for subsequent p-IV (3  $\mu$ s) is then set just below UE to measure  $\Delta V$ th. 50 p-IVs were measured in (b) and their average is given in (c). The TWC p-IV captures the RTN-induced  $\Delta V$ th, while the traditional p-IV at pre-set time often misses the charge and is inapplicable. Both the TWC and traditional p-IVs were taken after the "stabilize" period.

$\Delta$ Vth is evaluated from the difference between the TWC p-IV and the reference p-IV. The reference p-IV was obtained also from the average of 50 p-IV with the same sweep rate, performed on fresh devices before filling the energetically deep traps by applying the waveform in Fig. 2a. When measuring these 50 p-IV, it is possible that a trap can be filled during the measurement. These outlier p-IVs were excluded from the reference p-IV. This ensures capturing the  $\Delta$ Vth induced by both RTN and energetically deep traps, if they are present. In case that one is interested in capturing RTN-induced  $\Delta V$ th only, the reference p-IV should be taken after filling the energetically deep traps. Fig. 2c demonstrates that a single trap induced  $\Delta V$ th of ~2 mV is successfully captured by the TWC technique, which often would be missed by the traditional p-IV recorded at a preset time, as illustrated by the red circles in Fig. 2b. The measured  $\Delta V$ th/ $\Delta Id$  ratio is used to convert  $\Delta Id$  to  $\Delta V$ th.

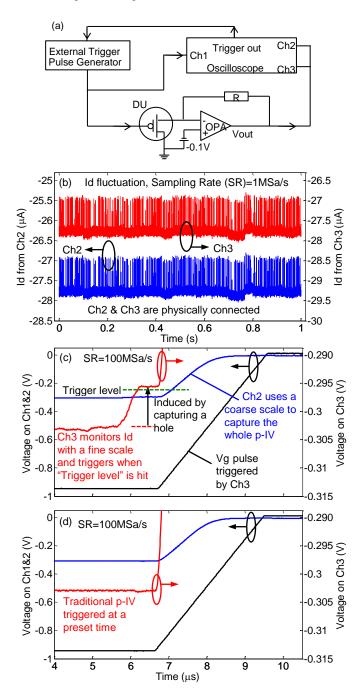

<u>Measurement setup</u>: As the main objective of this work is to develop a technique for measuring the RTN-induced  $\Delta V$ th under use Vdd, the detailed measurement setup is given in Fig. 3. Id under Vd=0.1 V was converted to a voltage, Vout, by a home-made operational amplifier circuit. During the 'Id monitor' phase in Fig. 2a, Vout was monitored by both channels 2 and 3 of an oscilloscope and one example is given in Fig. 3b.

In the following 'p-IV' phase of Fig. 2a, when Vout is above the 'trigger level' in Fig. 3c, the oscilloscope triggers and simultaneously sends out a signal to trigger the pulse generator for Vg. Both the pulse applied to the gate and the corresponding Vout are captured, as shown in Fig. 3c. Two channels are needed here: channel 3 is at a fine scale to ensure capturing the small Vout fluctuation with good accuracy and channel 2 is switched to a coarse scale to capture the whole p-IV. As a comparison, Fig. 3d shows an example triggered at a preset time that missed the trapped charge.

The UE in Fig. 2a can be caused by either a single trap or multiple traps. In the latter case, the UE results from the combined charges of multiple traps. This removes the need for selecting devices of a single trap and makes the method applicable to all devices.

The differences of this work from the typical BTI tests are that the p-IVs are only triggered when traps being charged and Vg-acceleration is not used here.

#### **III. RESULTS AND DISCUSSIONS**

#### A. A comparison between $\Delta Id/gm(Vdd)$ and $\Delta Vth(Vth)$

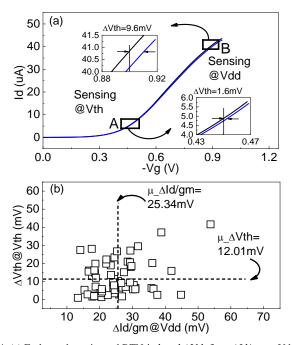

As mentioned in the introduction, early works [6-10] often estimated  $\Delta$ Vth by  $\Delta$ Id/gm(Vdd), where both  $\Delta$ Id and gm were obtained under Vg=Vdd. This is effectively measuring the shift of IV at Vg=Vdd, as marked by the point 'B' in Fig. 4a and the corresponding inset. The real  $\Delta$ Vth, however, should be evaluated from Vg=Vth at the point 'A' in Fig. 4a. In this work, Vth is extracted by extrapolating from the maximum gm point and Vth=-0.45 V in Fig. 4a. The shift in Vth,  $\Delta$ Vth, at a given sensing Vg is evaluated from  $\Delta$ Id/gm(Vgsense). We now compare the  $\Delta$ Vth evaluated at Vgsense=Vth ('A' in Fig. 4a) with that at Vgsense=Vdd ('B' in Fig. 4a).

Fig. 4b plots  $\Delta V$ th(Vth) against  $\Delta V$ th(Vdd)= $\Delta Id/gm(Vdd)$ measured on 63 devices. Both of them have a large DDV, but the correlation between them is poor. For similar  $\Delta Id/gm(Vdd)$ ,  $\Delta V$ th can spread from its minimum to its maximum approximately. As a result, errors are large if  $\Delta Id/gm(Vdd)$  is used as  $\Delta V$ th, so that it is essential to measure  $\Delta V$ th directly at Vg=Vth. Although both of them have maximum close to the typical device lifetime definition of 30~50 mV, the average  $\Delta Id/gm(Vdd)$  doubles that of  $\Delta V$ th, as shown by the two dashed lines in Fig. 4b. This is because many devices have  $\Delta V$ th(Vth) close to zero, but  $\Delta Id/gm(Vdd)$  are above 10 mV. The origin of the differences between these two will be analyzed next.

#### B. Effects of sensing Vg on $\Delta V$ th

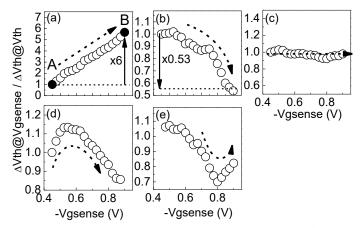

In Fig. 4a, the sensing Vg for  $\Delta$ Vth is -0.9 V for the point B and Vth=-0.45 V for the point A. Since the whole Id~Vg was measured, one can also extract the "apparent  $\Delta$ Vth" at other sensing Vg by using  $\Delta$ Id/gm(Vgsense). The "apparent  $\Delta$ Vth" here is referred to the  $\Delta$ Vth evaluated in this way under Vgsense $\neq$ Vth. Typical examples obtained from different devices are given in Figs. 5a-e.

Fig. 3. (a) Test configuration for the TWC measurement technique. A highspeed operational amplifier based circuit is used to convert Id to Vout that is connected to both channels 2 and 3. The "Trigger out" of the oscilloscope is

connected to the "External trigger in" of the pulse generator. (b) The Vout fluctuation is captured by both channels 2 and 3, as they are physically connected. (c) A screen-shot of the TWC p-IV measurement waveform. Channel 3 keeps its fine scale for accurate triggering, while channel 2 is switched to a coarse scale to capture the whole "TWC" p-IV. (d) A screen-shot of the traditional p-IV measurement at a preset time, where the trapped charge is missed.

The dependence of the apparent  $\Delta$ Vth on the sensing Vg has strong DDV, agreeing with that observed for single traps [16,17]. On one hand, Fig. 5a corresponds to Fig. 4a, where  $\Delta$ Vth increases monotonically with |Vg| and  $\Delta$ Vth at |Vg|=0.9 V is 6 times of the real  $\Delta$ Vth(Vth). On the other hand,  $\Delta$ Vth can also reduce by almost half over the same voltage range, as shown in Fig. 5b. There are also cases where (i)  $\Delta$ Vth is almost a constant (Fig. 5c); (ii)  $\Delta$ Vth increases initially and then reduces (Fig. 5d); and (iii)  $\Delta$ Vth decreases initially and then increases (Fig. 5e).

Fig. 4. (a) Early works estimated RTN-induced  $\Delta$ Vth from  $\Delta$ Id/gm at Vdd=0.9 V (Point 'B'), rather than directly measuring it at Vg=Vth (Point 'A'). The two insets are enlarged p-IV around the two points. The black p-IV is reference and the blue p-IV is the TWC p-IV. (b) The poor correlation between  $\Delta$ Id/gm at Vdd and  $\Delta$ Vth at Vg=Vth. Each point was taken from a different device. The dotted lines mark the mean values.

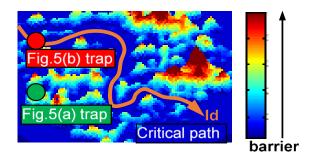

It is known that channel current can have a narrow percolation path near Vth and the impact of a charged trap on a deeply scaled device depends on the relative local current density beneath the trap [16-19]. This can explain the devicespecific dependence observed in Fig. 5. As schematically illustrated in Fig. 6, for the device in Fig. 5a, the trap is located far away from the current percolation path at Vth, so that it has little impact and  $\Delta$ Vth(Vth) is low. The many close-to-zero  $\Delta$ Vth(Vth) points in Fig. 4b indicates that this is often the case. As Vg increases, the current becomes more evenly spread and its relative density under this trap rises, leading to the increase of  $\Delta$ Vth with Vg. As there is current flowing beneath each trap at Vdd, there is no close-to-zero apparent  $\Delta$ Vth in Fig. 4b, when evaluated by  $\Delta$ Id/gm(Vdd).

For the device in Fig. 5b, however, the trapped charge is on top of the current percolation path at Vth, resulting in a large  $\Delta$ Vth at Vth. As Vg increases, the current path is widened, so that the impact of the same charge on the device reduces and the  $\Delta$ Vth decreases with |Vg| in Fig. 5b. Similarly, the relative current density under the trap in Fig. 5c changes little with Vg and  $\Delta$ Vth is insensitive to Vg. The dependence of relative current density under a trap on Vg may not be monotonic, which can explain the behavior in Figs. 5d&e. For instance, in Fig. 5d, it may increase initially and then decrease. Alternatively, when there are multiple traps, some can behave like Fig. 5a and some like Fig. 5b. A combination of them can give the complex dependence in Figs. 5d&e.

Fig. 5. Examples of the device specific dependence of the apparent  $\Delta V$ th on the sensing Vg, Vgsense. (a)-(e) were obtained from five different devices. The apparent  $\Delta V$ th at a Vgsense was obtained from the shift of TWC p-IV from the reference at Vgsense. The  $\Delta V$ th is normalized against its value at Vgsense=Vth. As the lowest |Vgsense| is close to Vth, the data starts from ~1 in all devices.

Fig. 6. A schematic illustration of different impacts of traps at different locations on a device at threshold condition. The current can follow a percolation path under Vg=Vth. The trap in green corresponds to the device in Fig. 5a: it is away from the critical current path, so that it only has a small effect on the device at Vth. The trap in red corresponds to the device in Fig. 5b: it is on top of the current critical path and has a large effect on the device at Vth.

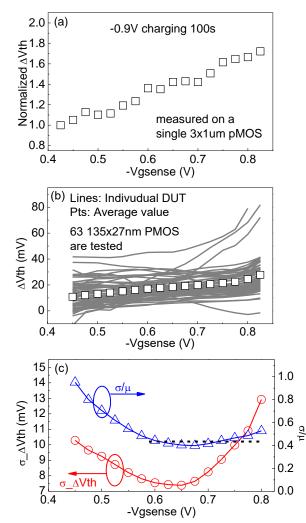

Although the deeply scaled device-specific dependence of  $\Delta$ Vth on sensing Vg can be explained by the interaction between the trap and the relative local current density beneath it, there is also a device independent  $\Delta$ Vth dependence on the sensing Vg. For a large  $3 \times 1 \mu m$  device where DDV is insignificant, Fig. 7a shows that  $\Delta$ Vth also increases with

|Vgsense|. On one hand, a more evenly distributed Id at higher |Vgsense| allows more traps making an effective impact. On the other hand, the charge induced Columbic scattering causes mobility degradation [27,28], which lead to  $\Delta Id(mobility)$ . When the apparent  $\Delta V$ th is evaluated from  $\Delta Id(measured)/gm$ , the  $\Delta Id(mobility)$  is treated as if it was caused by  $\Delta V$ th. In other words, the apparent  $\Delta V$ th=  $\Delta Id(measured)/gm$  includes the contribution from mobility degradation to  $\Delta Id$ . As the effect of mobility degradation increases with |Vgsense|, it contributes to the increase in the apparent  $\Delta V$ th for higher |Vgsense|.

#### C. Statistics

As there is hardly any information on the statistical properties of the directly measured RTN-induced  $\Delta$ Vth, especially in terms of its dependence on Vgsense, we report the DDV of this dependence here. Each line in Fig. 7b represents one device and the first impression is that the apparent  $\Delta$ Vth broadly increases for higher |Vgsense|. Although the  $\Delta$ Vth for some devices can reduce for higher |Vgsense| as shown in Fig. 5b, it is rare for a trap to be above a localized percolation path. As a result, the average (symbols in Fig. 7b) increases monotonically for higher |Vgsense|, which is partly driven by the mobility degradation.

Fig. 7. (a) The impact of sensing Vg on the apparent  $\Delta$ Vth of a large device of  $3 \times 1 \ \mu$ m. The deep level traps were filled under Vg=-0.9 V for 100 sec before

The standard deviation,  $\sigma$ , is plotted against Vgsense in Fig. 7c. It can be divided into two regions: as |Vgsense| increases,  $\sigma$  decreases first and then increases. The minimum point is around 0.65 V. To explore this further, the relative variation,  $\sigma/\mu$ , is also plotted in Fig. 7c. When |Vgsense|>0.65 V,  $\sigma/\mu$  only rises modestly, so that the higher  $\sigma$  is mainly caused by the higher  $\mu$ , as shown by the symbols in Fig. 7b. Below 0.65 V, however,  $\sigma$  increases and  $\mu$  decreases for lower |Vgsense|, resulting in a rising  $\sigma/\mu$ . When |Vgsense| lowers towards |Vth|, the current path becomes increasingly localized, leading to higher statistical variations, even though the trapped charges remain the same.

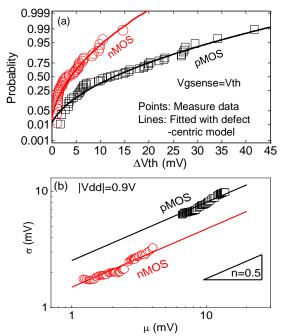

The cumulative distribution probability of  $\Delta V$ th is given in Fig. 8a and  $\sigma$  is plotted against  $\mu$  in Fig.8b for Vgsense=Vth. The RTN of nMOSFETs is smaller than that of pMOSFETs.  $\sigma$  follows  $\mu$  by a power law with an exponent of ~0.5, agreeing with the prediction of Defect-Centric model [2, 16, 29]. According to this model, the average  $\Delta V$ th induced by a trap,  $\eta$ , is,

$$\eta = \frac{\sigma^2}{2\mu}.$$

Using the fitted line in Fig. 8b,  $\eta\sim 3.2~mV$  is obtained for pMOSFETs. This  $\eta$  is  ${\sim}2{\times}q/Cox$  approximately, where q is one electron charge and Cox the gate oxide capacitance. This agrees well with the value reported for the recoverable component of NBTI of pFinFETs [16], although the test samples used here are planar pMOSFETs from a different supplier. The average number of traps, N, per device is,

$$N = \frac{\mu}{\eta}.$$

For pMOSFETs, a  $\mu \sim 12$  mV in Fig. 4b gives N  $\sim 4$ .

Fig. 8. (a) The cumulative distribution of  $\Delta$ Vth. The symbols are test data and the lines are fitted with the Defect-Centric model that assumes the number of traps per device following the Poisson's distribution and the  $\Delta$ Vth induced by a trap following

exponential distribution. (b) Standard deviation versus mean. Lines show that the data follow the prediction of Defect-Centric model well with a power exponent of 0.5. The different pairs of  $(\mu,\sigma)$  are obtained by varying the time window of "Id monitor" from 10  $\mu$ s to 100 sec in Fig. 2a.

For nMOSFETs, the corresponding values are  $\mu \sim 6.5 \text{ mV}$ ,  $\eta \sim 1.1 \text{ mV}$ , and N ~ 6. When compared with pMOSFETs, the lower RTN in nMOSFETs is caused by smaller  $\eta$ . Although there are more traps in nMOSFETs, they are in the high-k layer and further away from the conduction channel and induce a smaller  $\Delta V$ th [30].

#### IV. CONCLUSIONS

The conventional method of 'Measure-Stress-Measure' at preset time is inapplicable for the RTN-induced  $\Delta$ Vth, since the trap can be neutral when pulse IVs are taken. Early works estimate the RTN-induced  $\Delta$ Vth by  $\Delta$ Id/gm at Vg=Vdd and its accuracy is not known. In this paper, we propose a new TWC method for directly measuring the real  $\Delta$ Vth at Vg=Vth. By setting the trigger level close to the upper envelope of trapping-induced  $\Delta$ Id, it ensures that the pulse IV is taken when traps are charged.

Results show that there is no unique relationship between  $\Delta Id/gm$  at Vg=Vdd and the directly measured  $\Delta V$ th and their correlation is poor. The device-specific dependence of the apparent  $\Delta V$ th on the sensing Vg originates from the DDV of relative local current density under a trap at Vth. Moreover, on average,  $\Delta Id/gm(Vdd)$  doubles  $\Delta V$ th(Vth) and the charge-induced mobility degradation through Columbic scattering plays a role.

The TWC is applicable to devices with or without analyzable RTN signals. For the first time, it is used for assessing the statistical properties of the directly measured RTN-induced  $\Delta$ Vth. For the same trapped charges, it is found that  $\sigma$  has a minimum around |Vgsense|=0.65 V. The increase in  $\sigma$  when |Vg| lowers toward |Vth| is explained by an increased localization of current path. The DDV follows the Defect-Centric model. For the 135×27 nm devices used in this work, the average  $\Delta$ Vth induced per trap is ~3.2 mV for pMOSFETs and ~1.1 mV for nMOSFETs.

#### REFERENCES

- [1]. C. Prasad, M. Agostinelli, J. Hicks, S. Ramey, C. Auth, K. Mistry, S. Natarajan, P. Packan, I. Post, S. Bodapati, M. Giles, S. Gupta, S. Mudanai, K. Kuhn, "Bias Temperature Instability Variation on SiON/Poly, HK/MG and Trigate Architectures," in *Proc. Int. Rel. Phys. Symp.*, 2014, pp. 6A.5.1-6A.5.7, doi: 10.1109/IRPS.2014.6861101.

- [2]. B. Kaczer, T. Grasser, P. J. Roussel, J. Franco, R. Degraeve, L. A. Ragnarsson, E. Simoen, G. Groeseneken, and H. Reisinger, "Origin of NBTI variability in deeply scaled pFETs," in *Proc. Int. Rel. Phys. Symp.*, May 2010, pp. 26–32, doi: 10.1109/IRPS.2010.5488856.

- [3]. M. K. Li, "Jitter Challenges and Reduction Techniques at 10 Gb/s and Beyond," *IEEE Trans. Advanced Packaging*, vol. 32, no. 2, pp. 290-297, 2009, doi: 10.1109/TADVP.2009.2012432.

- [4]. J. Zou, R. Wang, N. Gong, R. Huang, X. Xu, J. Ou, C. Liu, J. Wang, J. Liu, J. Wu, S. Yu2 P. Ren, H. Wu, S. W. Lee, and Y. Wang, "New insights into AC RTN in scaled high-κ/metal-gate MOSFETs under digital circuit operations," in *Proc. Symp. Very Large Scale Integr. (VLSI) Technol.*, Jun. 2012, pp. 139–140, doi: 10.1109/VLSIT.2012.6242500.

- [5]. H. Miki, M. Yamaoka, N. Tega, Z. Ren, M. Kobayashi, C. P. D'Emic, Y. Zhu, D. J. Frank, M. A. Guillorn, D.-G. Park, W. Haensch, and K. Torii,

"Understanding Short-term BTI Behavior through Comprehensive Observation of Gate-voltage Dependence of RTN in Highly Scaled Highk / Metal-gate pFETs," in *Proc. Symp. Very Large Scale Integr. (VLSI) Technol.*, Jun. 2011, pp. 148–149.

- [6]. H. Miki, M. Yamaoka, D. J. Frank, K. Cheng5, D.-G. Park, E. Leobandung, and K. Torii, "Voltage and Temperature Dependence of Random Telegraph Noise in Highly Scaled HKMG ETSOI nFETs and its Impact on Logic Delay Uncertainty," in *Proc. Symp. Very Large Scale Integr. (VLSI) Technol.*, Jun. 2012, pp. 137–138, doi: 10.1109/VLSIT.2012.6242499.

- [7]. K. Takeuchi, T. Nagumo, S. Yokogawa, K. Imai, and Y. Hayashi, "Single-Charge-Based Modeling of Transistor Characteristics Fluctuations Based on Statistical Measurement of RTN Amplitude," in *Proc. Symp. Very Large Scale Integr. (VLSI) Technol.*, Jun. 2009, pp. 54–55.

- [8]. K. Ota, M. Saitoh, C. Tanaka, D. Matsushita, and T. Numata, "Systematic Study of RTN in Nanowire Transistor and Enhanced RTN by Hot Carrier Injection and Negative Bias Temperature Instability," in *Proc. Symp. Very Large Scale Integr. (VLSI) Technol.*, Jun. 2014, pp. 200–201, doi: 10.1109/VLSIT.2014.6894417.

- [9]. C. Liu, K. T. Lee, H. Lee, Y. Kim, S. Pae, and J. Park, "New Observations on the Random Telegraph Noise induced Vth Variation in Nano-scale MOSFETs," in *Proc. Int. Rel. Phys. Symp.*, 2014, pp. XT.17.1-XT.17.5, doi: 10.1109/IRPS.2014.6861194.

- [10]. T. Nagumo, K. Takeuchi, T. Hase, and Y. Hayashi, "Statistical Characterization of Trap Position, Energy, Amplitude and Time Constants by RTN Measurement of Multiple Individual Traps," in *IEDM Tech. Dig.*, pp. 628-631, 2010, doi: 10.1109/IEDM.2010.5703437.

- [11]. C. Chen, Q. Ran, H. Cho, A. Kerber, Y. Liu, M. Lin, and R. W. Dutton, "Correlation of I<sub>d</sub>- and I<sub>g</sub>-Random Telegraph Noise to Positive Bias Temperature Instability in Scaled High-κ/Metal Gate n-type MOSFETs," in *Proc. Int. Rel. Phys. Symp.*, May 2011, pp. 190–195, doi: 10.1109/IRPS.2011.5784475.

- [12]. M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, S. De Gendt, and G. Groeseneken, "New analysis method for time-dependent device-to-device variation accounting for within-device fluctuation," *IEEE Trans. Electron Devices*, vol. 60, no. 8, pp. 2505–2511, Aug. 2013, doi: 10.1109/TED.2013.2270893.

- [13]. A. Teramoto, T. Fujisawa, K. Abe, S. Sugawa, and T. Ohmi, "Statistical Evaluation for Trap Energy Level of RTS Characteristics," in *Proc. Symp. Very Large Scale Integr. (VLSI) Technol.*, Jun. 2010, pp. 99–100, doi: 10.1109/VLSIT.2010.5556186.

- [14]. J. W. Lu, C. Vaz, J. P. Campbell, J. T. Ryan, K. P. Cheung, G. F. Jiao, G. Bersuker, and C. D. Young, "Device-Level PBTI-induced Timing Jitter Increase in Circuit-Speed Random Logic Operation," in *Proc. Symp. Very Large Scale Integr. (VLSI) Technol.*, Jun. 2014, pp. 102–103, doi: 10.1109/VLSIT.2014.6894387.

- [15]. M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, T. Schram, R. Ritzenthaler, G. Groeseneken, and A. Asenov, "Development of a Technique for Characterizing Bias Temperature Instability-Induced Device-to-Device Variation at SRAM-Relevant Conditions," *IEEE Trans. Electron Devices*, vol. 61, no. 9, pp. 3081–3089, Sept. 2014, doi: 10.1109/TED.2014.2335053.

- [16]. J. Franco, B. Kaczer, M. Toledano-Luque, Ph. J. Roussel, J. Mitard, L.-A Ragnarsson, L. Witters, T. Chiarella, M. Togo, N. Horiguchi, G. Groeseneken, M. F. Bukhori, T. Grasser, and A. Asenov, "Impact of Single Charged Gate Oxide Defects on the Performance and Scaling of Nanoscaled FETs," in *Proc. Int. Rel. Phys. Symp.*, 2012, pp. 5A.4.1-5A.4.6, doi: 10.1109/IRPS.2012.6241841.

- [17]. B. Kaczer, J. Franco, M. Toledano-Luque, Ph. J. Roussel, M. F. Bukhori, A. Asenov, B. Schwarz, M. Bina, T. Grasser, and G. Groeseneken, "The Relevance of Deeply-Scaled FET Threshold Voltage Shifts for Operation Lifetimes," in *Proc. Int. Rel. Phys. Symp.*, 2012, pp. 5A.2.1-5A.2.6, doi: 10.1109/IRPS.2012.6241839.

- [18]. A. Asenov, R. Balasubramaniam, A. R. Brown, and J. H. Davies, "RTS Amplitudes in Decananometer MOSFETs: 3-D Simulation Study," *IEEE Trans. Electron Devices*, vol. 50, no. 3, pp. 839–845, Mar. 2003, doi: 10.1109/TED.2003.811418.

- [19]. M. F. Bukhori, S. Roy, and A. Asenov, "Simulation of Statistical Aspects of Charge Trapping and Related Degradation in Bulk MOSFETs in the Presence of Random Discrete Dopants," *IEEE Trans. Electron Devices*, Vol. 57, No. 4, pp. 795-803, 2010, doi: 10.1109/TED.2010.2041859

- [20]. M. Nour, Z. Çelik-Butler, A. Sonnet, F.-C. Hou, S. Tang, and G. Mathur, "A Stand-Alone, Physics-Based, Measurement-Driven Model and Simulation Tool for Random Telegraph Signals Originating From Experimentally Identified MOS Gate-Oxide Defects," *IEEE Trans.*

*Electron Devices*, Vol. 63, No. 4, pp.1428-1436, 2016, doi: 10.1109/TED.2016.2528218.

- [21]. J. F. Zhang, M. H. Chang, Z. Ji, L. Lin, I. Ferain, G. Groeseneken, L. Pantisano, S. De Gendt, M. M. Heyns, "Dominant layer for stress-induced positive charges in Hf-based gate stacks," *IEEE Electron Dev. Lett.*, Vol.29, No.12, pp.1360-1363, 2008, doi: 10.1109/LED.2008.2006288.

- [22]. R. Gao, Z. Ji, S. M. Hatta, J. F. Zhang, J. Franco, B. Kaczer, W. Zhang, M. Duan, S. De Gendt, D. Linten, G. Groeseneken, J. Bi and M. Liu, "Predictive As-grown-Generation (A-G) model for BTI-induced device/circuit level variations in nanoscale technology nodes," in *IEDM Tech. Dig.*, pp. 778-781, 2016, doi: 10.1109/IEDM.2016.7838520.

- [23]. M. Duan, J. F. Zhang, Z. Ji, W. Zhang, D. Vigar, A. Asenov, L. Gerrer, V. Chandra, R. Aitken, and B. Kaczer, "Insight into Electron Traps and Their Energy Distribution under Positive Bias Temperature Stress and Hot Carrier Aging," *IEEE Trans. Electron Devices*, Vol. 63, No. 9, pp. 3642-3648, 2016, doi: 10.1109/TED.2016.2590946.

- [24]. M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, and A. Asenov, "Key issues and solutions for characterizing hot carrier aging of nano-meter scale nMOSFETs," *IEEE Trans. Electron Devices*, Vol. 64, No. 6, pp.2478-2484, 2017, doi: 10.1109/TED.2017.2691008.

- [25]. J. F. Zhang, Z. Ji, and W. Zhang, "As-grown-generation (AG) model of NBTI: A shift from fitting test data to prediction," *Microelectronics Reliability*, Vol. 80, pp. 109–123, 2018, doi: 10.1016/j.microrel.2017.11.026.

- [26]. M. Duan, J. F. Zhang, Z. Ji, J. G. Ma, W. Zhang, B. Kaczer, T. Schram, R. Ritzenthaler, G. Groeseneken, and A. Asenov, "Key issues and techniques for characterizing Time-dependent Device-to-Device Variation of SRAM," in *IEDM Tech. Dig.*, pp.774-777, 2013, doi: 10.1109/IEDM.2013.6724730.

- [27]. Z. Çelik-Butler, S. P. Devireddy, H.-H. Tseng, P. Tobin, A. Zlotnicka, "A low-frequency noise model for advanced gate-stack MOSFETs," Microelectronics Rel. Vol. 49, pp.103–112, 2009, doi: 10.1016/j.microrel.2008.12.005.

- [28]. W. Zhu, J. P. Han, and T. P. Ma, "Mobility measurement and degradation mechanisms of MOSFETs made with ultrathin high-k dielectrics," *IEEE Trans. Electron Dev.*, vol. 51, No.1, pp. 98-104, 2004, doi: 10.1109/TED.2003.821384.

- [29]. L. M. Procel, F. Crupi, J. Franco, L. Trojman, and B. Kaczer, "Defect-Centric Distribution of Channel Hot Carrier Degradation in Nano-MOSFETs," *IEEE Electron. Dev. Lett.*, vol. 35, no. 12, pp. 1167-1169, Dec, 2014, doi: 10.1109/LED.2014.2361342.

- [30]. M. Toledano-Luque, B. Kaczer, J. Franco, Ph.J. Roussel, T. Grasser, T.Y. Hoffmann, and G. Groeseneken, "From mean values to distributions of BTI lifetime of deeply scaled FETs through atomistic understanding of the degradation," in *Proc. Symp. Very Large Scale Integr. (VLSI) Technol.*, Jun. 2011, pp. 152–153.