# GeSe-based Ovonic Threshold Switching Volatile True Random Number Generator

Zheng Chai, Wei Shao, Weidong Zhang, James Brown, Robin Degraeve, Flora D. Salim, Sergiu Clima, Firas Hatem, Jian Fu Zhang, Pedro Freitas, John Marsland, Andrea Fantini, Daniele Garbin, Ludovic Goux, and Gouri Sankar Kar

Abstract—In this paper, we propose and demonstrate a novel technique for true random number generator (TRNG) application using GeSe-based Ovonic threshold switching (OTS) selector devices. The inherent variability in OTS threshold voltage results in a bimodal distribution of on/off states which can be easily converted into digital bits. The experimental evaluation shows that the proposed TRNG enables the generation of high-quality random bits that passed 12 tests in the National Institute of Standards and Technology statistical test suite without complex external circuits for post-processing. The randomness is further evidenced by the prediction rate of ~50% using machine learning algorithm. Compared with the TRNGs based on non-volatile memories, the volatile nature of OTS avoids the reset operation, thus further simplifying the operation and improving the generation frequency.

Index Terms—selector, OTS, GeSe, random number generation, variability, resistive-switching memory (RRAM)

#### I. INTRODUCTION

RANDOM number generators (RNGs) are essential in many applications such as communication systems, statistical sampling, computer simulation and cryptography systems [1]. Different from the software-based pseudo-RNGs [2], hardware-based true RNGs (TRNGs), which use local physical phenomena to produce truly random outputs, cannot be replicated or predicted externally, and are therefore particularly critical in hardware security applications such as the Internet of Things (IoT) [3]. There are existing CMOS-based TRNGs based on randomness sources such as thermal noise [4]-[6], random telegraph noise (RTN) [7],[8], current fluctuation in oxide after soft breakdown [9], time-dependent oxide breakdown (TDDB) [10], etc. However, most of these CMOS TRNGs suffer from complex circuitry for randomness extraction, hence difficulty in scalability.

Emerging memory devices are promising for a broad spectrum of applications such as storage class memory [11] and neuromorphic computing [12]. Several TRNGs based on emerging memory devices have been proposed, utilizing RTN [8], cycle-to-cycle variability [13] or the stochastic delay time

of switching [14] as the randomness source, in which the randomness extraction can be greatly simplified by reading the random "0" or "1" bits directly from the on/off state. Despite this improvement, RTN in those devices are not stable enough [15],[16], while to use cycle-to-cycle variability as randomness source those non-volatile devices require a reset operation to erase the bit stored in the last cycle before generating a new bit, which increases operational complexity and limits the generation frequency. Moreover, many emerging devices suffer from limited endurance or throughput which hinders their TRNG application [13],[14],[17]-[19].

Selector devices are used to suppress the sneak current in resistive-switching memory (RRAM) arrays. Ovonic threshold switching (OTS) chalcogenide materials have gained interest for selector application because of their favorable electrical characteristics such as volatile nature, abrupt switching and excellent endurance[20],[21]-[23]. Particularly, the endurance of GeSe-based OTS device is more than 10<sup>10</sup> cycles by using a simple recovery scheme, while after composition optimization, the OTS based on Se-Ge-As-Te has achieved an excellent endurance of more than 10<sup>11</sup> cycles without recovery operation. Recently, it has been reported that under a constant voltage, the time-to-switch-on (t-on) follow the Weibull distribution [24]. This stochastic nature of OTS switching, being a drawback for memory applications, however can be exploited to implement TRNGs. The volatile nature of OTS makes reset operations unnecessary, thus simplifying the operation conditions and improving the generation frequency. The compatibility of OTS selectors to RRAM fabrication process may facilitate OTS TRNG in protecting the data memorized in RRAM arrays or assisting RRAM-based security applications [25], [26].

In this work, we demonstrate a scalable TRNG using GeSebased OTS selector with volatile switching. The 10,000-bit random stream generated from a single device without complex extraction circuity demonstrates good randomness by passing the National Institute of Standards and Technology (NIST) statistical tests and the machine learning prediction test based on long short-term memory (LSTM) architecture, proving that OTS selector is a promising candidate for TRNG application.

Manuscript received dd/mm/yyyy; revised dd/mm/yyyy; accepted dd/mm/yyyy. Date of publication dd/mm/yyyy; date of current version dd/mm/yyyy. This work was supported by the EPSRC of U.K. under EP/M006727/1 & EP/S000259/1). The review of this letter was arranged by Editor XXXX. (Corresponding author: Zheng Chai, Weidong Zhang.)

Zheng Chai, Weidong Zhang, James Brown, Firas Hatem, Jian Fu Zhang, Pedro Freitas and John Marsland are with the Department of Electronics and Electrical Engineering, Liverpool John Moores University, L3 3AF Liverpool, U.K. (e-mail: <a href="mailto:z.chai@ljmu.ac.uk">z.chai@ljmu.ac.uk</a>; <a href="mailto:w.zhang@ljmu.ac.uk">w.zhang@ljmu.ac.uk</a>).

Wei Shao and Flora D. Salim are with the School of Science (Computer Science), RMIT University, Melbourne, VIC 3001, Australia. Robin Degraeve, Sergiu Clima, Andrea Fantini, Daniele Garbin,

Robin Degraeve, Sergiu Clima, Andrea Fantini, Daniele Garbin, Ludovic Goux, and Gouri Sankar Kar are with imec, 3001 Leuven, Belgium.

Color versions of one or more of the figures in this letter are available online at <a href="http://ieeexplore.ieee.org">http://ieeexplore.ieee.org</a>. Digital Object Identifier XXXX

## II. DEVICE AND CHARACTERIZATION

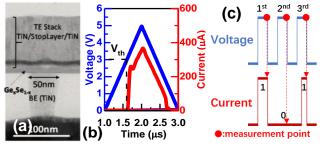

Amorphous GexSe<sub>1-x</sub> films are prepared by room temperature physical vapor deposition (PVD). TiN/GeSe/TiN selector devices were integrated in a 300 mm process flow, using a pillar (TiN) bottom electrode which defines the device size down to 50 nm. A GexSe<sub>1-x</sub> chalcogenide films was achieved and passivated with a low-temperature BEOL process scheme, as shown in Fig. 1a. The device size used in this work is 65 nm and the Ge<sub>x</sub>Se<sub>1-x</sub> thickness is 10 nm. Fig. 1b shows the typical I-V of a triangular switching pulse [27]. The fast I-V characterization was done with a Keysight B1500A semiconductor analyzer with embedded B1530A Waveform Generator/Fast Measurement Unit (WGFMU).

Fig.1. (a) TEM of the OTS selector used in this work. (b) A typical I-V of a triangular switching pulse. (c) Schematic of the bitstream generation waveform. Current is measured at the end of each pulse. Device might be switched on immediately (1<sup>st</sup> pulse), or not switched on (2<sup>nd</sup> pulse), or switched on after some time during the pulse (3<sup>rd</sup> pulse). Such stochasticity is used as the source of the randomness generation.

# III. RESULTS AND DISCUSSIONS

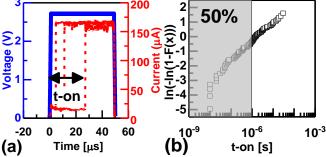

It has been reported that under a constant voltage bias, the current response varies: the device might be switched on immediately; or switched on after some time (t-on) during the pulse; or remain off till the end of the pulse (Fig. 1c) [24],[27]. 100 repetitive square pulses are applied onto an OTS selector, with amplitude of 2.7V and duration of 50 μs. Fig. 2a demonstrates the current response of 3 arbitrarily selected pulses with different t-on. t-on of the total 100 pulses follows Weibull distribution (Fig. 2b). Note t-on cannot be recorded below 10 ns due to instrumental limitation. Around 50 t-on falls below 1 μs, suggesting that under this condition (2.7V, 1μs), the OTS device has a balanced probability to be switched on or not, which can be a good source of random "0" and "1" generation.

Fig.2. (a) Current response of 3 arbitrarily selected pulses with different t-on, out of the 100 pulses with Vpulse = 2.7 V and tpulse =  $50 \mu s$ ; (b) Weibull plot of t-on measured from the 100 pulses. ~50% of the t-on falls below 1  $\mu s$ .

To verify this, after first-firing, a sequence of 10,000 square pulses with the width of 1 µs and amplitude of 2.7 V is applied

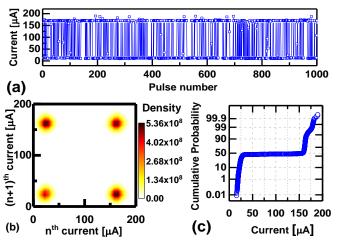

onto this OTS device. Current measurement is carried out at the end of each pulse to check whether the device has been switched on or not, as shown in Fig. 1c. Fig. 3a demonstrates the current measured at the initial 1000 pulses. The low current state refers to the cycles in which OTS remains off, while the high current state refers to the cycles in which OTS has been switched on. The two cases, i.e. switch-on and remain-off, distribute randomly. For the statistical analysis of the entire 10,000 current states, a 2-D kernel density of the current at (n+1)<sup>th</sup> pulse as a function of the current at n<sup>th</sup> pulse, i.e. time-lag-plot, is plotted in Fig. 3b to visualize the current states and transitions between them. The balanced color indicates that the two states are indeed statistically balanced. The cumulative distribution plot (CDF) in Fig. 3c also shows a bimodal distribution, with an abrupt separation probability at 50%.

Fig.3. (a) Demonstration of the current measured at the initial 1000 pulses using  $V_{\text{pulse}}=2.7~V$  and  $t_{\text{pulse}}=1~\mu\text{s}.$  (b) 2-D kernel density of the time lag plot of the entire 10,000 obtained current states. (c) Cumulative distribution plot (CDF) of the 10,000 current states showing a bimodal distribution of states abruptly separated at ~50%

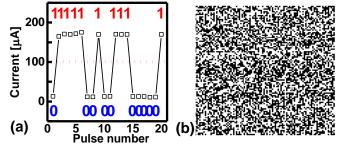

The entire 10,000-bit "0" and "1" sequence is generated by comparing the measured current with a criteria level of  $100 \,\mu\text{A}$ . "1" will be generated for the switch-on case, and otherwise "0" will be generated, as demonstrated with the initial 20 pulses in Fig. 4a. The generated random bits are presented as a 2-D image in Fig. 4b for clearer illustration. Black color represents bit 0 and white is bit 1. Almost equal number black and white bits are randomly distributed without any regular pattern.

Fig.4. (a) Demonstration of the "0" and "1" bits generated by the initial 20 pulses. 100  $\mu$ A is used as the criteria (dash line). (b) A 100×100 2-D image representation of the generated 10,000-bit random stream. Black colour represents "0" and white is "1".

The randomness of the bits produced was further evaluated by the National Institute of Standards and Technology (NIST)

Test Suite, a statistical package to evaluate the randomness of binary sequences. Table I summarized the test result for the 10,000 random bits generated by the OTS-TRNG. Each test calculates a p-value, and p>0.001 [28] and success proportion  $\geq$  9/10 are considered good performance. Note that some of the tests consist of several individual tests and we report the smallest p-value out of them. The generated random sequences have passed 12 NIST tests, supporting an excellent randomness performance of the proposed TRNG. The randomness is also evaluated with machine learning test using long short-term memory (LSTM) architecture [29], a powerful tool for handling long-range dependencies in general-purpose modeling tasks. The LSTM consists of two hidden layers, with 32 neurons in each layer. A prediction rate of 49.63% has been achieved, further supporting that the unpredictability of our TRNG's bit-sequence is acceptable [30].

TABLE I: NIST TEST RESULT

| Test                      | p-value   | Proportion | Result |

|---------------------------|-----------|------------|--------|

| Frequency                 | 0.350485  | 9/10       | Pass   |

| Block Frequency           | 0.350485  | 9/10       | Pass   |

| Runs                      | 0.739918  | 10/10      | Pass   |

| Longest Run               | 0.534146  | 9/10       | Pass   |

| FFT                       | 0.534146  | 10/10      | Pass   |

| Cumulative Sums           | 0.004301* | 9/10       | Pass   |

| Linear Complexity         | 0.122325  | 10/10      | Pass   |

| Approximate entropy       | 0.534146  | 9/10       | Pass   |

| Non- Overlapping Template | 0.004342* | 10/10      | Pass   |

| Overlapping Template      | 0.002043* | 10/10      | Pass   |

| Serial                    | 0.122325* | 9/10       | Pass   |

| Rank                      | 0.949536  | 1/1        | Pass   |

The sequence is divided into 10 streams, except the Rank test \*Smallest of the multiple p-values

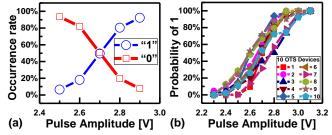

Fig.5. (a) Occurrence rate of "0" and "1" at different pulse amplitudes, intersecting at 2.7V. (b) Occurrence rate of "1" at different pulse amplitudes measured in 10 devices at different locations across a 300 mm wafer.

As shown in Fig. 5a, "1" appears more frequently with increasing pulse amplitude. 2.7 V is the balance point generating the balanced "0" and "1" random bits while the ratio of "0" and "1" can be modulated by simply tuning pulse amplitude. This agrees with the previous observation that the threshold voltage (V<sub>th</sub>) of OTS selectors statistically depends on operation voltage and time [27]. Such random switching is also observed in 10 OTS device with the same size but at different locations across a 300 mm wafer (Fig. 5b). The balance point varies between 2.6 V and 2.8 V, due to process variation across the wafer. Similar random switching has also been observed in a wide range of chalcogenide materials such as GeAsTe and Si-Ge-As-Te [23].

The difficulty in finding the accurate balance point, and the sensitivity this point to bias and process variations, is a common issue for many emerging TRNG solutions based on novel logic and memory devices such as FeFET, RRAM and magnetic tunnel junction (MTJ)[8],[13],[14],[31],[32]. It can be migrated by solutions at the peripheral circuitry level, for example, a bias-sweeping scanning scheme associated with a counter can be designed to determine the balance point. This paper aims to demonstrates the novel concept of OTS-based TRNG. The design of such peripheral circuitry for tracking or correction is a subject of future work.

The volatile switching mechanism of OTS not only makes reset operation unnecessary, but also provide excellent throughput due to its electronic-induced switching nature [33], which is a great advantage over memristor-TRNGs whose throughput can be bottlenecked by the relative slower atomic/ionic movement [14]. The switching speed of OTS can be shorter than 2 ns [20]. Furthermore, its dependence of switching probability on both voltage and time make it possible to conveniently reduce the pulse width to nanosecond level by increasing the switching voltage, while keeping the bimodal distribution balanced [24]. It is predictable that the throughput can be conveniently boosted to 100 MHz or higher, by increasing the operation voltage for a faster switching speed.

## IV. CONCLUSIONS

In this paper, we propose and demonstrate a novel technique for TRNG application using GeSe-based OTS selector devices. The statistical switch-on variability can be easily converted into digital "0"s and "1"s with high-quality randomness. The generated 10,000-bit sequence passes 12 tests in the NIST statistical test suite. The randomness is further supported by the machine-learning algorithm. Compared with the TRNGs based on non-volatile memories, the volatile nature of OTS avoids the reset operation hence improves the generation speed. OTS device has shown great potential for TRNGs with excellent reliability, tunability, and throughput. This work proves that OTS selectors can be used as TRNGs especially in hardware security applications in the era of IoT.

# **REFERENCES**

- T.L. Blackwell, Application of randomness in system performance measurement, Harvard University, Cambridge, Massachusetts, 1998

- [2] G. Alvarez and S. Li, Some basic cryptographic requirements for chaos-based cryptosystems, *Int. J. Bifurcation Chaos*, vol. 16, no. 8, pp. 2129-2151, Aug. 2006, DOI: 10.1142/S0218127406015970

- [3] A. Menezes, P. van Oorschot and S. Vanstone, Handbook of Applied Cryptography, Boca Raton, FL, USA, CRC Press, Inc., 1996

- [4] M. Bucci, L. Germani, R. Luzzi, A. Trifiletti and M. Varanonuovo, A high-speed oscillator-based truly random number source for cryptographic applications on a smart card IC, *IEEE Trans. Computers*, vol. 52, no. 882, pp. 403–409, Apr. 2003, DOI: 10.1109/TC.2003.1190581

- [5] C.S. Petrie and J.A. Connelly, A noise-based IC random number generator for applications in cryptography, *IEEE Trans. Circuits and Systems I*, vol. 47, no. 5, pp. 615–621, May 2002, DOI: 10.1109/81.847868

- [6] C. Tokunaga, D. Blaauw and T. Mudge, True random number generator with a metastability-based quality control, *IEEE J. Solid-State Circuits*, vol. 43, no. 1, pp. 78-85, Jan. 2008, DOI: 10.1109/JSSC.2007.910965

- [7] J. Brown, R. Gao, Z. Ji, J. Chen, J. Wu, J. Zhang, B. Zhou, Q. Shi, J. Crowford and W. Zhang, A low-power and high-speed True Random

- Number Generator using generated RTN, in VLSI Symp. Tech. Dig., Honolulu, HI, USA, June 2018, DOI: 10.1109/VLSIT.2018.8510671

- [8] R. Brederlow, R. Prakash, C. Paulus and R. Thewes, A low-power true random number generator using random telegraph noise of single oxide-traps, *IEEE International Solid State Circuits Conference -Digest of Technical Papers*, San Francisco, CA, USA, Feb. 2006, DOI: 10.1109/ISSCC.2006.1696222

- [9] S. Yasuda, H. Satake, T. Tanamoto, R. Ohba, K. Uchida and S. Fujita, Physical random number generator based on MOS structure after soft breakdown, *IEEE J. Solid-State Circuits*, vol. 39, no. 8, pp. 1375-1377, Sept. 2004, DOI: 10.1109/JSSC.2004.831480

- [10] N. Liu, N. Pinckney, S. Hanson, D. Sylvester and D. Blaauw, A true random number generator using time-dependent dielectric breakdown, Symposium on VLSI Circuits - Digest of Technical Papers, Honolulu, HI, USA, June 2011

- [11] Y. Chen and C. Petti, ReRAM technology evolution for storage class memory application, 46th European Solid-State Device Research Conference (ESSDERC), Lausanne, Switzerland, Sept. 2016, DOI: 10.1109/ESSDERC.2016.7599678

- [12] Z. Chai, P. Freitas, W. Zhang, F. Hatem, J. F. Zhang, J. Marsland, B. Govoreanu, L. Goux, and G. S. Kar, Impact of RTN on Pattern Recognition Accuracy of RRAM-based Synaptic Neural Network, *IEEE Electron Device Lett.*, vol. 39, no. 11, pp. 1652-1655, Sept. 2018, DOI: 10.1109/LED.2018.2869072

- [13] H. Mulaosmanovic, T. Mikolajick and S. Slesazeck, Random Number Generation Based on Ferroelectric Switching, *IEEE Electron Device Lett.*, vol. 39, no. 1, pp. 135-138, Nov. 2018, DOI: 10.1109/LED.2017.2771818

- [14] H. Jiang, D. Belkin, S.E. Savel'ev, S. Lin, Z. Wang, Y. Li, S. Joshi, R. Midya, C. Li, M. Rao, M. Barnell, Q. Wu, J.J. Yang and Q. Xia, A novel true random number generator based on a stochastic diffusive memristor, *Nat. Commun.*, vol. 8, no. 882, pp. 1-9, Oct. 2017, DOI: 10.1038/s41467-017-00869-x

- [15] Z. Chai, J. Ma, W.D. Zhang, B. Govoreanu, J.F. Zhang, Z. Ji, M. Jurczak, Probing the Critical Region of Conductive Filament in Nanoscale HfO<sub>2</sub> Resistive-Switching Device by Random Telegraph Signals, *IEEE Trans. Electron Devices*, vol. 64, no. 10, pp. 4099-4105, Sept. 2017, DOI: 10.1109/TED.2017.2742578

- [16] D. Veksler, G. Bersuker, B. Chakrabarti, E. Vogel, S. Deora, K. Matthews, D. C. Gilmer, H.-F. Li, S. Gausepohl, and P.D. Kirsch, Methodology for the statistical evaluation of the effect of random telegraph noise (RTN) on RRAM characteristics, in IEDM Tech. Dig., San Francisco, CA, USA, Dec. 2012, DOI: 10.1109/IEDM.2012.6479013

- [17] E. Piccinini, R. Brunetti, and M. Rudan, Self-Heating Phase-Change Memory-Array Demonstrator for True Random Number Generation, *IEEE Trans. Electron Devices*, vol. 64, no. 5, pp. 2185 – 2192, May 2017, DOI: 10.1109/TED.2017.2673867

- [18] C.-Y Huang, W. C. Shen, Y.-H. Tseng, Y.-C. King, and C.-J. Lin, A Contact-Resistive Random-Access-Memory-Based True Random Number Generator, *IEEE Electron Device Lett.*, vol. 33, no. 8, pp. 1108 – 1110, August 2012, DOI: 10.1109/LED.2012.2199734

- [19] H.-S. P. Wong, S. Raoux, S.-B. Kim, J. Liang, J.P. Reifenberg, B. Rajendran, M. Asheghi, and K.E. Goodson, Phase change memory, *Proc. IEEE*, vol. 98, no. 12, pp. 2201–2227, Dec. 2010, DOI: 10.1109/JPROC.2010.2070050

- [20] B. Govoreanu, G.L. Donadio, K. Opsomer, W. Devulder, V.V. Afanas' ev, T. Witters, S. Clima, N.S. Avasarala, A. Redolfi, S. Kundu, O. Richard, D. Tsvetanova, G. Pourtois, C. Detavemie, L. Goux, G. S. Kar, Thermally stable integrated Se-based OTS selectors with >20 MA/cm² current drive, >3.10³ half-bias nonlinearity, tunable threshold voltage and excellent endurance, in VLSI Symp. Tech. Dig., Kyoto, Japan, June 2017, DOI: 10.23919/VLSIT.2017.7998207

- [21] N.S. Avasarala, G. L. Donadio, T. Witters, K. Opsomer, B. Govoreanu, A. Fantini, S. Clima, H. Oh, S. Kundu, W. Devulder, M. H. van der Veen, J. Van Houdt, M. Heyns, L. Goux, G. S. Kar, Half-

- threshold bias Ioffreduction down to nA range of thermally and electrically stable high-performance integrated OTS selector, obtained by Se enrichment and N-doping of thin GeSe layers, *in VLSI Symp. Tech. Dig.*, Honolulu, HI, USA, June 2018, DOI: 10.1109/VLSIT.2018.8510680

- [22] F. Hatem, Z. Chai, W. Zhang, A. Fantini, R. Degraeve, S. Clima, D. Garbin, J. Robertson, Y. Guo, J.F. Zhang, J. Marsland, P. Freitas, L. Goux, G. Kar, Endurance improvement of more than five orders in GexSe1-x OTS selectors by using a novel refreshing program scheme, 35.2, in IEDM Tech. Dig., Washington, DC, USA, Dec. 2019

- [23] D. Garbin, W. Devulder, R. Degraeve, G.L. Donadio, S. Clima, K. Opsomer, A. Fantini, D. Cellier, W.G. Kim, M. Pakala, A. Cockburn, C. Detavernier, R. Delhougne, L. Goux, G.S. Kar, Composition Optimization and Device Understanding of Si-Ge-As-Te Ovonic Threshold Switch Selector with Excellent Endurance, 35.1, in IEDM Tech. Dig., Washington, DC, USA, Dec. 2019

- [24] Z. Chai, W. Zhang, R. Degraeve, S. Clima, F. Hatem, J.F. Zhang, P. Freitas, J. Marsland, A. Fantini, D. Garbin, L. Goux, and G.S. Kar, Dependence of switching probability on operation conditions in GexSe1-x OTS selectors, *IEEE Electron Device Lett.*, vol. 40, no. 8, pp. 1269-1272, Aug. 2019, DOI: 10.1109/LED.2019.2924270

- [25] R. Liu, H. Wu, Y. Pang, H. Qian and S. Yu, Experimental Characterization of Physical Unclonable Function Based on 1 kb Resistive Random Access Memory Arrays, *IEEE Electron Device Lett.*, vol. 36, no. 12, pp. 1380-1383, Oct. 2015, DOI: 10.1109/LED.2015.2496257

- [26] A. Chen, Comprehensive assessment of RRAM-based PUF for hardware security applications, in IEDM Tech. Dig., Washington, DC, USA, Dec. 2015, DOI: 10.1109/IEDM.2015.7409672

- [27] Z. Chai, W. Zhang, R. Degraeve, S. Clima, F. Hatem, J. F. Zhang, P. Freitas, J. Marsland, A. Fantini, D. Garbin, L. Goux and G.S. Kar, Evidence of filamentary switching and relaxation mechanisms in GexSe<sub>1-x</sub>OTS selectors, in VLSI Symp. Tech. Dig., Kyoto, Japan, June. 2019, DOI: 10.23919/VLSIT.2019.8776566

- [28] A. Rukhin, J. Soto, J. Nechvatal, M. Smid, E. Barker, S. Leigh, M. Levenson, M. Vangel, D. Banks, A. Heckert, J. Dray, and S. Vo, A Statistical Test Suite for Random and. Pseudorandom Number Generators for. Cryptographic Applications, NIST, Gaithersburg, MD, USA, Special Pub. 800-22, 2010

- [29] S. Hochreiter and J. Schmidhuber, Long short-term memory, *Neural Comput.*, vol. 9, no. 8, pp. 1735–1780, Nov. 1997, DOI: 10.1162/neco.1997.9.8.1735

- [30] J. Kim, T. Ahmed, H. Nili, N.D. Truong, J. Yang, D.S. Jeong, S. Sriram, D.C. Ranasinghe and O. Kavehei, Nano-Intrinsic True Random Number Generation: A Device to Data Study, *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 66, no. 7, pp. 2615-2626, Feb. 2019, DOI: 10.1109/TCSI.2019.2895045

- [31] S. Balatti, S. Ambrogio, Z. Wang, and D. Ielmini, True Random Number Generation by Variability of Resistive Switching in Oxide-Based Devices, *IEEE Journal On Emerging And Selected Topics In Circuits And Systems*, vol. 5, no. 2, pp. 214-221, June 2015, DOI: 10.1109/JETCAS.2015.2426492

- [32] W.H. Choi, L.V. Yang, J. Kim, A. Deshpande, G. Kang, J.-P. Wang, and C.H. Kim. A magnetic tunnel junction based true random number generator with conditional perturb and real-time output probability tracking. in IEDM Tech. Dig., Dec. 2014, DOI: 10.1109/IEDM.2014.7047039

- [33] S.R. Ovshinsky, Reversible Electrical Switching Phenomena in Disordered Structures, Phys. Rev. Lett., vol. 21, no. 20-11 p. 1450, Nov. 1968, DOI:https://doi.org/10.1103/PhysRevLett.21.1450