# Hot carrier aging and its variation under use-bias: kinetics, prediction, impact on Vdd and SRAM

M. Duan<sup>1</sup>, J. F. Zhang<sup>1</sup>, A. Manut<sup>1</sup>, Z. Ji<sup>1</sup>, W. Zhang<sup>1</sup>, A. Asenov<sup>2</sup>, L. Gerrer<sup>2</sup>, D. Reid<sup>3</sup>, H. Razaidi<sup>2</sup>, D. Vigar<sup>4</sup>, V. Chandra<sup>5</sup>, R. Aitken<sup>5</sup>, B. Kaczer<sup>6</sup>, and G. Groeseneken<sup>6</sup>

<sup>1</sup>School of Engineering, Liverpool John Moores University, Byrom Street, Liverpool L3 3AF, UK (<u>j.f.zhang@ljmu.ac.uk</u>)

<sup>2</sup>Dept. Electronics and Electrical Engineering, University of Glasgow, UK.

<sup>3</sup>GSS, Glasgow, UK.

<sup>4</sup>CSR, Cambridge CB4 0WZ, UK.

<sup>5</sup>Arm R&D, San Jose, USA.

<sup>6</sup>IMEC, Leuven B3001, Belgium.

# **Abstract**

As CMOS scales down, hot carrier aging (HCA) scales up and can be a limiting aging process again. This has motivated re-visiting HCA, but recent works have focused on accelerated HCA by raising stress biases and there is little information on HCA under use-biases. Early works proposed that HCA mechanism under high and low biases are different, questioning if the high-bias data can be used for predicting HCA under use-bias. A key advance of this work is proposing a new methodology for evaluating the HCA-induced variation under use-bias. For the first time, the capability of predicting HCA under use-bias is experimentally verified. The importance of separating RTN from HCA is demonstrated. We point out the HCA measured by the commercial Source-Measure-Unit (SMU) gives erroneous power exponent. The proposed methodology minimizes the number of tests and the model requires only 3 fitting parameters, making it readily implementable.

#### Introduction

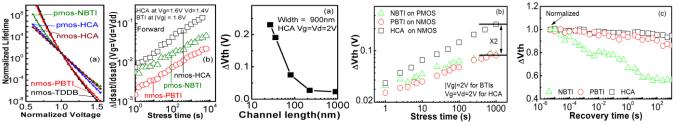

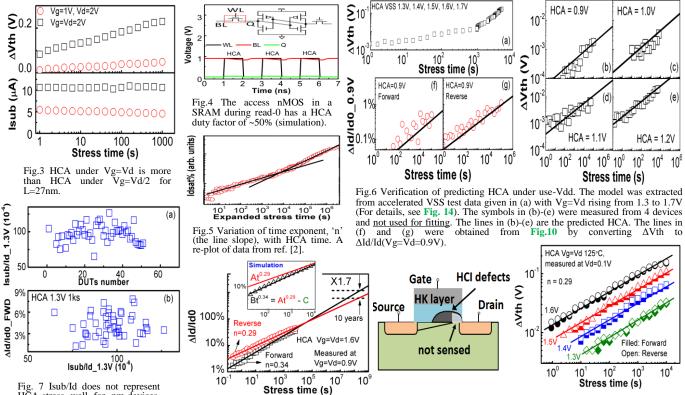

Recent results (**Fig.1**) show Hot Carrier Aging (HCA) can be severe for current/future CMOS nodes [1-7], because: (i) Channel length downscaling enhances HCA (**Fig.2a**). For some sub-30nm processes, HCA can be higher than BTI (**Figs.1b&2b**); (ii) HCA can have larger time exponents (**Figs.1b&2b**) [3-7] and its importance increases with aging. (iii) NBTI recovery [8-10] is higher than HCA (**Fig.2c**); (iv) Conventionally, the worst HCA occurs during switch near Vg~Vd/2 and duty factor (DF) is typically low (1~2%) [7,11]. For modern CMOS, however, more damage occurs under Vg=Vd (**Fig. 3**) [3,6,7] and DF can be high. For example, during 'read 0' in a SRAM cell, one access nMOSFET can suffer HCA for ~50% of time (**Fig. 4**).

The renewed HCA-threat has motivated its re-visit [1-7,12]. It is reported aging mechanisms and time exponent, 'n' (**Eq.1** in **Table 1**), are different under different stress biases [1,6,7]. 'n' can also vary with time (e.g. **Fig.5**) [2,4,5,7], challenging the lifetime,  $\tau$ , prediction based on **Eq.1** that requires a constant 'n' [11,13,14]. The recent works have focused on bias-accelerated HCA [1-7,12] and there is little data on HCA under **use-bias**. For test engineers, *two pressing questions* are: can  $\tau$  under use-bias still be predicted by the established JEDEC method based on **Eq.1** and how to evaluate 'n' correctly for HCA? A key advance of this work is answering them and finding the pitfalls for extracting 'n'. For the first time, the capability of predicting HCA under use-bias is experimentally verified (**Fig.6**).

# **Devices and Experiments**

nMOSFETs of MG/HK were made by an industrial process with L×W of 27×(90~900)nm and use-Vdd of 0.9V. Vd=Vg is chosen to represent stress, as Isub/Id has a device-to-device variation (DDV) at stress-0 for nm-devices (**Fig.7a**) and it does not correlate with HCA (**Fig.7b**). All tests were at 125°C

#### Methodology

A. Selecting parameter for extracting power exponent, 'n'

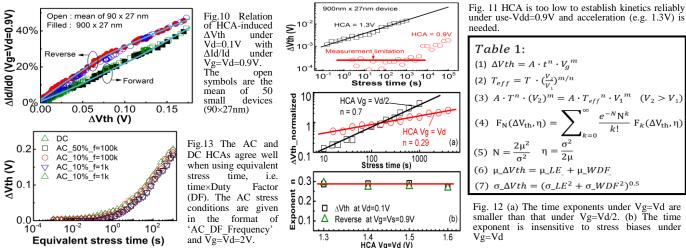

HCA was widely monitored by forward saturation current shift under Vg=Vd=Vdd,  $\Delta$ Id/Id F, although reverse saturation current shift, ∆Id/Id R, and ∆Vth(Vd≤0.1V) also were used [1-7,11,12]. The problem is 'n' for  $\Delta Id/Id$  F is larger than 'n' for  $\Delta Id/Id$  R, leading to their incorrect crossover and errors in prediction at 10 years (Fig.8), highlighting the importance of 'n'-accuracy. Under Vg=Vd, ΔId/Id F does not sense the HCA-defects above space charge region (Fig.8), resulting in an apparent larger 'n', as simulated by subtracting a constant from real power law (inset of Fig.8). The 'n' extracted from the forward  $\Delta Id/Id$  is erroneous. To capture all defects,  $\Delta Vth(Vd=0.1V)$  should be used for extracting 'n', as  $\Delta V$ th  $F = \Delta V$ th R(**Fig.9**). Once  $\Delta V$ th is predicted, we propose evaluating  $\Delta Id/Id$  F and  $\Delta Id/Id$  R by using their measured relation with  $\Delta V$ th (**Fig.10**).

#### B. HCA acceleration

SRAM often is used for qualifying new processes [15], where the access nMOSFETs suffer the worst HCA under Vg≈Vd (Figs.3&4). HCA under use-Vg=Vd must be predicted and we focus on it here. Under use-bias, Fig.11 shows that HCA is too low to establish its kinetics reliably within a practical time and acceleration is needed. One may accelerate HCA by raising Vd only [12] or both Vg and Vd with Vg=Vd [1,6]. Fig.12a confirms 'n' is larger under Vg<Vd than under Vg=Vd [1,7], so that Vg<Vd must not be used to predict HCA under use-Vg=Vd. When accelerated by Vg=Vd, 'n' is bias-independent (Fig.12b) and should be used.

### C. DC versus AC

Unlike NBTI(AC)<NBTI(DC) [8-10], the AC and DC HCAs agree well, regardless of frequency and duty-factor (DF) for the same equivalent stress time, i.e. DF×time (**Fig.13**), confirming the frequency-independence [3]. DC will be used.

# D. Voltage-Step-Stress (VSS)

The VSS technique recently developed for NBTI [16] allows extracting both 'n' and 'm' (Eq.1) from just one large

device, reducing test numbers by ~80%, and will be adopted for HCA here. For an L×W=27×900nm, stress under each Vg=Vd lasted for T=1ks and biases were then stepped up (Fig.14), lifting HCA up from the power law (Fig.14c). Based on Eqs.1-3, HCA under a high Vg=Vd was converted into a longer equivalent stress time under a low Vg=Vd (Fig.14c) and  $\Delta$ Vth follows a power law well even when  $\Delta$ Vth>150mV, corresponding to  $\Delta$ Id/Id>30% (Fig.10), well beyond the typical 10% HCA lifetime criterion and allowing reliable extraction of 'n' and 'm' (Fig.14c).

#### **Prediction**

A model is useful only if it can predict aging under usebias. The HCA predicted by the model extracted from the VSS data in Fig.14 agrees well with the test data in Figs.6b-g. The highest ΔVth in Figs.6a&14 is ~2-orders above ΔVth under 0.9V (Fig.6b), verifying its prediction capability. We emphasize the model was extracted from the data in Fig.6a only and the test data in Figs.6b-g were not used for fitting. The extracted model (Eq.1) can be used for evaluating HCA under any bias and time and for predicting lifetime and operation Vdd (Fig. 15).

#### HCA in nm-width devices

Unlike L×W=27×900nm, 27×90nm devices suffer from RTN-like within-a-device fluctuation (WDF) and large device-to-device variation (DDV) (**Fig.16**). To extract HCA kinetics, one has to use the smooth mean of 50 devices, but 'n' depends on how data is taken (**Fig.17**). After a stress, ΔVth fluctuates and one can use its up-envelope (UE), lower-envelope (LE) [17], or average over a period of time, e.g. ~10ms (**Fig.17b**), as a typical quasi-DC Source-Measure-Unit (SMU) does. The 'n' from UE and DC (inset of **Fig. 17a**) is smaller than the 'n=0.29' from a device of W=900nm (**Fig.14c**), but the 'n' from LE agrees well with it. The smaller 'n' for UE incorrectly takes it below LE when extrapolating (see the 'cross-over' in **Fig. 17a**).

To explain the difference in 'n', **Figs.18a&b** show that WDF=(UE-LE) does not increase with aging. It must originate from as-grown defects and should be excluded from aging kinetics, so that LE must be used for extracting 'n'. LE\_F and LE\_R correlates (**Fig.19a**), but WDF\_F and WDF\_R does not (**Fig.19b**), supporting their different origins.

Since HCA-recovery is insignificant (**Fig.2c**), one may think it can be measured by a quasi-DC SMU [7,18]. This, however, gives an erroneous lower 'n' (**Fig.17a**) by including some as-grown WDF. Adding a constant to a power law leads to an apparent lower 'n' at short time and a variation of 'n' with time (inset, **Fig.17a**) [13].

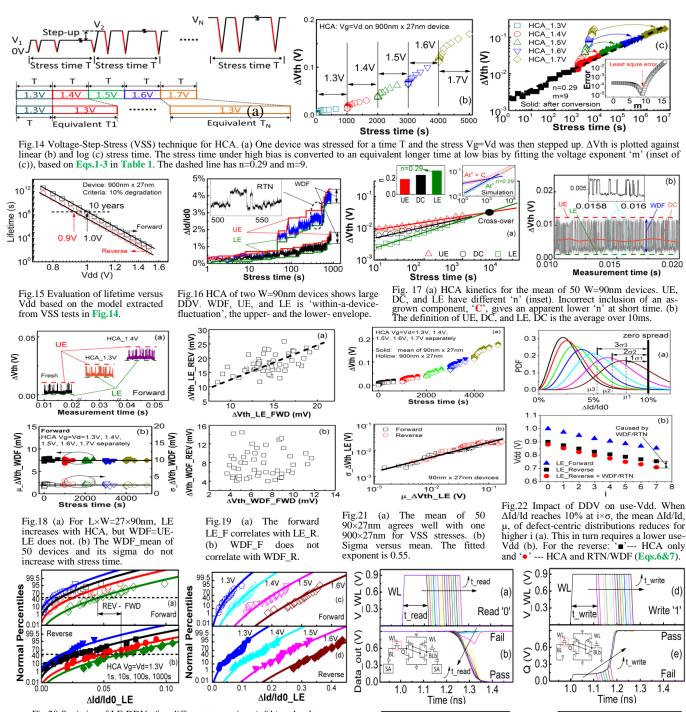

# Statistic HCA

The DDV of LE at different time (**Figs.20a&b**) and voltage (**Figs.20c&d**) follows the defect-centric distribution (**Eqs.4&5**) well [19]. LE\_mean of 50 W=90nm devices agrees well with  $\Delta V$ th of one W=900nm device (**Fig.21a**) and can be predicted by the same method (**Figs.6&14**). After

knowing LE\_mean, the standard deviation,  $\sigma$ , can be evaluated from its power law relation with the mean (Fig.21b).

#### A. Impact on use-Vdd

To have a yield corresponding to  $i\times\sigma$ ,  $\Delta Id/Id=10\%$  is required at  $i\times\sigma$ , resulting in smaller mean value (**Fig.22a**) and in turn lower use-Vdd (**Fig.22b**) for higher i. For a yield of  $3\times\sigma$  (99.7%), HCA-only and HCA+WDF (**Eqs.6,7**) reduces Vdd from its zero-spread value by 75mV and 100mV, respectively.

#### B. Impact on 6T-SRAM

Assuming only one access nMOSFET suffered HCA and using the predicted HCA distribution at 10 years under 0.9V for simulation [20], static write/read noise margin reduces/rises, respectively (Fig.23), as a weakened access nMOSFET is not in favor of write. Both the dynamic read (Figs.24a-c) and write (Figs.24d-f) access time deteriorates, since longer time is required through a weakened access nMOSFET. This demonstrates that the extracted HCA model can be incorporated into a compact simulator to evaluate the required margin for a specified yield.

#### **Conclusions**

As CMOS scales down, HCA scales up. For the first time, this work experimentally verifies that the HCA under use-Vdd can be predicted by the power law extracted from VSS-method, provided that correct acceleration and 'n'-evaluation are made. We point out the forward saturation  $\Delta Id/Id$  and HCA measured by SMU gives erroneous 'n' for nm-width devices. The model requires only 3 fitting parameters (Eq.1), making it readily implementable.

# Acknowledgement

The authors thank Plamen Asenov of GSS for his critical comments. This work was supported by the EPSRC of U.K. under the Grant No. EP/L010607/1.

#### References

- [1] A. Bravaix et al, IRPS 2013, 2D.6.1-2D6.9.

- [2] J. H. Stathis et al, IEDM 2014, p. 522.

- [3] G. T. Sasse, IEEE Trans. Elec. Dev., 55, pp.3167-3174, 2008.

- [4] A. J. Scholten et al, IEEE Trans. Elec. Dev., 58, pp.1-8, 2011.

- [5] F. Cacho et al. IRPS 2014, 5D.4.1.

- [6] A. Bravaix et al, IEDM 2011, p.622.

- [7] M. Cho et al, IEEE Trans. Elec. Dev., 60, pp. 4002-4007, 2013.

- [8] S. Ramey et al, IRPS 2014, XT.2.1.

- [9] M. H. Chang and J. F. Zhang, J.Appl.Phys., 101, art. no. 024516, 2007.

- [10] S. F. W. M. Hatta et al, IEEE Trans. Elec. Dev., 60, pp.1745-1753, 2013.

- [11] JEDEC 2011 p.15.

- [12] C. Liu et al, IEDM 2014, p 836.

- [13] Z. Ji et al, IEDM 2013, p.413

- [14] Z. Ji et al, IEEE Trans. Elec. Dev., 57, pp.228-237, 2010.

- [15] U. Bhattacharya, Intel Tech. J. 2008, p.111.

- [16] Z. Ji et al, IRPS 2014, GD-2.

- [17] M. Duan et al, IEDM 2013, p.774.

- [18] N. H. H. Hsu et al, IRPS 2012.

- [19] L. M. Procel et al, IEEE Elec.Dev.Lett., 35, p. 1167-1169, 2014.

- [20] http://ptm.asu.edu/.

Fig.1 A comparison of Hot Carrier Aging (HCA) with BTIs reported by early works. (a) and (b) are re-plots of data from refs. [2] and [1], respectively.

Fig.2 (a) Downscaling L increases HCA. The stress was at 125°C for 1000sec. (b) A comparison of HCA and BTIs for L=27nm used in this work. Stresses were under the same |Vg|, with Vd=Vg for HCA and Vd=0 for PBTI and NBTI. (c) A comparison of their recovery under Vg=Vd=0.

HCA-stress well for nm-devices, as it has a device-to-device

Equivalent stress time (s)

FICA-stress well for infl-devices, as it has a device-to-device Fig.8 Although test data (o and  $\square$ ) show ( $\triangle Id/Id = F$ )-( $\triangle Id/Id = F$ ), higher 'n' for  $\triangle Id/Id = F$  variation (DDV) at stress=0 (a) and leads to incorrect ( $\triangle Id/Id = F$ )-( $\triangle Id/Id = F$ ) when extrapolating.  $\triangle Id/Id = F$  does not sense its DDV does not correlate with the defects above space charges. The ' $\triangle$ ' in inset is calculated from (At<sup>0.29</sup>-Constant), which fits well with Bt<sup>0.34</sup> (black line). Subtracting a constant from a real power law (red line) can give an 'apparent' higher 'n'. Id was measured under Vg=Vd=0.9V.

Fig.9 The forward and reverse  $\Delta Vth$ measured under Vd=0.1V agrees

HCA Vg=Vd (V)

smaller than that under Vg=Vd/2. (b) The time exponent is insensitive to stress biases under

1.2 1.3 1.4 1.1 ∆ld/ld0\_LE Ald/Id0 LE Time (ns) Time (ns) Fig.20 Statistics of LE DDV after different stress time (a&b) and voltage LE FWD 2 LE FWD (c&d). The lines are fitted with the defect-centric distribution (Eqs.4&5). 30% 30% ∐ 20% □ 10% **⊥** 20% ARSNM/RSNM0 0.6 0123456 0% Ω  $\mathbf{S}^{0.3}$ 0% 0% -40% 1.0 1.2 1.3 1.4 1.0 **0**0.0 Read Static Noise Margin ■ IF FWD t\_read (normalized) t write (normalized) -80% Write Noise Margi FWD 0.6 Fig.24 Impact of HCA of access nMOS on dynamic read (a-c) and write (d-

0.3

0.0

HCI

0.2

VQ (V)

0.8

Fig.23 Impact of the predicted HCA at 10 years under 0.9V on static read (a) and write (b) noise margins. Their change at i×σ is given in (c). The 32nm PTM model from [20] was used.

Fig.24 Impact of HCA of access nMOS on dynamic read (a-c) and write (d-f) assess time, normalized against their fresh value. The mean and sigma of HCA under Vdd=0.9V at 10 years were predicted based on test data and then used to compute the defect-centric PDF vs HCA. For a given PDF, the corresponding HCA were used to compute the failure time, as illustrated in (a,b) and (d,e). The (t\_Fail, PDF) pairs were plotted in (c) & (f). The insets of (c)&(f) shows the normalized margins against i×σ.