### LJMU Research Online

Alharbi, M, Edwards, G and Stocker, R

Hybrid Quantum-Dot Cellular Automata Nanocomputing Circuits

http://researchonline.ljmu.ac.uk/id/eprint/24083/

### **Article**

**Citation** (please note it is advisable to refer to the publisher's version if you intend to cite from this work)

Alharbi, M, Edwards, G and Stocker, R (2024) Hybrid Quantum-Dot Cellular Automata Nanocomputing Circuits. Electronics, 13 (14).

LJMU has developed LJMU Research Online for users to access the research output of the University more effectively. Copyright © and Moral Rights for the papers on this site are retained by the individual authors and/or other copyright owners. Users may download and/or print one copy of any article(s) in LJMU Research Online to facilitate their private study or for non-commercial research. You may not engage in further distribution of the material or use it for any profit-making activities or any commercial gain.

The version presented here may differ from the published version or from the version of the record. Please see the repository URL above for details on accessing the published version and note that access may require a subscription.

For more information please contact <a href="mailto:researchonline@ljmu.ac.uk">researchonline@ljmu.ac.uk</a>

MDPI

Article

### Hybrid Quantum-Dot Cellular Automata Nanocomputing Circuits

Mohammed Alharbi <sup>1,\*</sup>, Gerard Edwards <sup>1</sup> and Richard Stocker <sup>2</sup>

- Division of Electronic and Electrical Engineering, School of Engineering, Faculty of Engineering and Technology, Liverpool John Moores University, Liverpool L3 2ET, UK; g.edwards@ljmu.ac.uk

- Department of Computer Science, Electronics and Electrical Engineering, Faculty of Science and Engineering, University of Chester, Chester CH1 4BJ, UK; r.stocker@chester.ac.uk

- \* Correspondence: m.alharbi@2022.ljmu.ac.uk; Tel.: +966-54406-9694

Abstract: Quantum-dot cellular automata (QCA) is an emerging transistor-less field-coupled nanocomputing (FCN) approach to ultra-scale 'nanochip' integration. In QCA, to represent digital circuitry, electrostatic repulsion between electrons and the mechanism of electron tunnelling in quantum dots are used. QCA technology can surpass conventional complementary metal oxide semiconductor (CMOS) technology in terms of clock speed, reduced occupied chip area, and energy efficiency. To develop QCA circuits, irreversible majority gates are typically used as the primary components. Recently, some studies have introduced reversible design techniques, using reversible majority gates as the main building block, to develop ultra-energy-efficient QCA circuits. However, this approach resulted in time delays, an increase in the number of QCA cells used, and an increase in the chip area occupied. This work introduces a novel hybrid design strategy employing irreversible, reversible, and partially reversible QCA gates to establish an optimal balance between power consumption, delay time, and occupied area. This hybrid technique allows the designer to have more control over the circuit characteristics to meet different system needs. A combination of reversible, irreversible, and innovative partially reversible majority gates is used in the proposed hybrid design method. We evaluated the hybrid design method by examining the half-adder circuit as a case study. We developed four hybrid QCA half-adder circuits, each of which simultaneously incorporates various types of majority gates. The QCADesigner-E 2.2 simulation tool was used to simulate the performance and energy efficiency of the half-adders. This tool provides numerical results for the circuit input/output response and heat dissipation at the physical level within a microscopic quantum mechanical model.

Keywords: quantum-dot cellular automata (QCA); hybrid; half-adder; QCADesigner-E

Citation: Alharbi, M.; Edwards, G.; Stocker, R. Hybrid Quantum-Dot Cellular Automata Nanocomputing Circuits. *Electronics* **2024**, *13*, 2760. https://doi.org/10.3390/ electronics13142760

Academic Editor: Chang Wook Ahn

Received: 21 May 2024 Revised: 27 June 2024 Accepted: 12 July 2024 Published: 13 July 2024

Copyright: © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

### 1. Introduction

Quantum-dot cellular automata (QCA) is a field-coupled nanocomputing (FCN) approach in which information is encoded as the polarisation of each cell in terms of the orientation of the electrons in a quantum dot [1]. The QCA concept for encoding binary information relies on QCA cells, which consist of four quantum dots and two electron charges, arranged in an antipodal orientation [2]. The information is subsequently propagated to neighbouring cells via Coulombic electrostatic forces [3], which results in energy-efficient digital circuits with no current flow and no associated ohmic dissipation.

Theoretically, QCA offers several advantages over complementary metal oxide semi-conductor (CMOS) technology in the development of digital circuits, including a lower power consumption, higher speed, and higher integration density. QCA circuits are significantly smaller than CMOS circuits due to the use of quantum dots, which measure just a few nanometres across, with a view to being implemented at the molecular level. The R. Wolkow University of Alberta research group has made fantastic progress on experimentally implementing QCA cells and forming useful digital circuits with the quantum dots that form dangling hydrogen bonds on the surface of silicon [4]. In comparison, even the smallest transistors in advanced CMOS technology are relatively larger. This size reduction

Electronics **2024**, 13, 2760 2 of 24

allows for greatly increased densities of logic gates and computing elements within the same area. Additionally, QCA circuits can operate at higher frequencies than CMOS circuits. This is because there is no current flow; instead, the interaction of electrons in quantum dots allows for rapid dynamics, which could lead to faster processing speeds. Moreover, QCA circuits are theoretically more energy-efficient than CMOS circuits. QCA achieves data transfer by controlling the electron tunnelling between quantum dots, thus changing the cell charge configuration, which encodes binary information. Conversely, CMOS technology relies on the repeated charging and discharging of capacitors during each clock cycle, which leads to significant energy dissipation. While QCA presents many advantages over CMOS, it remains largely in the experimental stage. Before QCA can be considered a viable commercial alternative to CMOS in practical applications, researchers must address significant challenges such as fabrication issues, temperature stability, integration with existing technologies, simulation and modelling tools, and design scalability.

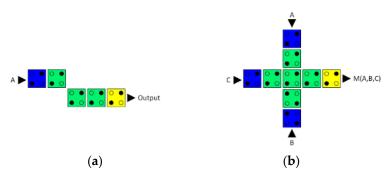

The process of designing QCA digital circuits typically entails the use of majority gates and inverters. An 'AND' or 'OR' gate can be generated by assigning a binary value of '0' or '1' to one of the majority gate inputs, respectively. Thus, the incorporation of majority gates and inverters enables the development of different digital circuits. QCA technology allows for the construction of computer systems by building complex Boolean functions using inverters and majority gates. The QCA-based computer system improvement is particularly significant for fields in which speed, area, and power consumption are critical considerations. The standard QCA inverter is reversible due to the one-to-one connection between the input and output signals, as shown in Figure 1a. Conversely, the conventional majority gate is irreversible because of its configuration, which includes three inputs and only a single output pin, as depicted in Figure 1b.

Figure 1. (a) QCA inverter and (b) conventional irreversible QCA majority gate.

The conventional irreversible QCA majority gate has been utilised as a fundamental component in several studies to develop various QCA digital circuits [5–7]. According to the second law of thermodynamics, information loss typically occurs in conventional irreversible computing methods, accompanied by heat dissipation, in which bits are irreversibly erased within the logic circuitry, known as Landauer's limit [8]. The heat dissipation due to the information loss is quantified as  $k_BT\ln 2$  joules per bit erased, where  $k_B$  is the Boltzmann constant and T is the temperature [8]. The experimental verification of Landauer's theory has confirmed the existence of a physical limit to irreversible computing [9–11]. In CMOS technology, for example, the amount of energy that is dissipated due to information loss is approximately fifty times greater than Landauer's lower limit [12].

To perform computing operations with ultralow energy dissipation below  $k_BT\ln 2$ , reversible logic operations are essential, with each input signal having a unique associated output pin [13]. Theoretically, reversible computing operations, in which reversibility is maintained from the logic synthesis level down to the physical layout level, result in no information loss and consequently zero energy dissipation into the environment [14]. Several studies have simulated QCA digital circuits with extremely low energy dissipation by utilising logically and physically reversible design techniques [15–19]. These reversible design techniques use reversible majority gates, which recycle the input signals, as the

Electronics **2024**, 13, 2760 3 of 24

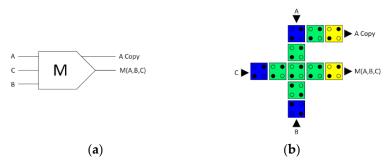

main building blocks. Figure 2a shows the logic symbol of the reversible majority gate, while Figure 2b shows the QCA layout. The implementation of QCA circuits with logically and physically reversible approaches results in significantly less energy dissipation than that employing irreversible circuits [13]. However, reversible design methods often lead to time delays, increased area usage, and the use of more QCA cells, i.e., increases in circuit cost metrics [20].

**Figure 2.** (a) Logic symbol and (b) QCA layout of the reversible majority gate with three input and three output pins.

Generally, the term hybrid circuit refers to an electronic circuit that combines various types of components, manufacturing processes, substrate materials, or technology integrations to achieve a specific functionality. Hybrid circuits offer significant advantages by utilising the unique capabilities of different component types or technologies. This approach frequently results in improved performance and efficiency, as well as a smaller size and lower cost compared to using a single component or technology. Hybrid circuits are especially valuable in applications requiring complex functionalities that no single technology can sufficiently provide.

Prior research has developed hybrid QCA circuits by combining several QCA components to build these circuits. These studies presented hybrid QCA adder circuits that combined a Ladner-Fischer adder with a ripple carry adder [21] or a carry-select adder with a ripple carry adder [22]. The main goal of these designs was to increase speed and reduce the occupied area in comparison to standard QCA adder circuits. However, this study introduces an innovative hybrid design method that provides a compromise between energy-efficiency-oriented reversible design methods and cost-efficiency-oriented irreversible design methods. The hybrid design strategy described here utilises a combination of reversible and irreversible majority gates, as well as the novel partially reversible majority gate that is developed in this study. The performance of the hybrid design strategy is examined using the half-adder circuit as a case study. Four different half-adder designs are developed in this research, each utilising a specific combination of three types of majority gates. The information loss, energy dissipation, speed of data transmission, occupied area, number of QCA cells used, and circuit cost of the introduced half-adder designs are comprehensively examined. A comparison of the results shows that the hybrid design approach provides the designer with a high level of control over the circuit characteristics, allowing an optimal trade-off between circuit cost and energy efficiency to be achieved to meet the requirements of different systems.

The subsequent sections of this paper are structured as follows: Section 2 elucidates the underlying principle of the proposed hybrid design method. Section 3 presents a case study on the hybrid QCA design method for the half-adder circuit. Section 4 presents the simulation results for the half-adder designs. Section 5 discusses the simulation results for the hybrid QCA half-adders. Section 6 provides the conclusions of this study.

### 2. Hybrid Design Method

Power consumption, operating frequency, and area are key specifications that need to be considered when designing digital integrated circuits (ICs) to ensure that a circuit meets Electronics **2024**, 13, 2760 4 of 24

its intended performance, efficiency, and application requirements [23]. Current QCA design methodologies use a single form of a majority gate, either reversible or irreversible, to build QCA digital circuits. Irreversible majority gates are employed in QCA circuits when the primary consideration is cost-effectiveness in terms of the operating frequency and occupied area. Conversely, reversible majority gates are employed in QCA circuits when the primary emphasis is on power efficiency. Most applications require circuits that simultaneously demonstrate optimal levels of efficiency in terms of power consumption, time, and area. This study introduces an innovative hybrid design method that represents a compromise between energy-efficiency-oriented reversible design methods and cost-efficiency-oriented irreversible design methods.

In the hybrid design method discussed in this study, three types of majority gates are simultaneously used to develop QCA digital circuits. The hybrid design method utilises reversible and irreversible majority gates, along with a novel partially reversible majority gate, as the primary building blocks for creating hybrid QCA circuits. The key advantage of the proposed hybrid design method is its ability to provide a high level of control over the circuit characteristics during the circuit design process. The ultimate function of the circuit determines the number of majority gates employed for each of the three types of majority gates.

For example, if energy efficiency is prioritised for the circuit while maintaining an appropriate level of cost efficiency, then the number of reversible majority gates must surpass the number of irreversible and partially reversible majority gates in the circuit. In contrast, if minimising the area costs while maintaining a suitable level of energy efficiency is the focus, then the circuit must include more irreversible majority gates than reversible and partially reversible majority gates. To establish the optimal trade-off between energy dissipation and circuit cost, the use of a greater proportion of partially reversible majority gates than reversible and irreversible majority gates is advisable. Thus, the hybrid design method allows the designer to determine the number of different types of majority gates in the circuit, i.e., reversible, partially reversible, or irreversible, thereby providing significant control over the circuit characteristics throughout the design process.

To execute the hybrid design strategy, we first developed an innovative, partially reversible majority gate. Only a few previous studies have investigated the partially reversible design concept [24–26]. In 2011, Ottavi et al. introduced a partially reversible method to balance the energy dissipation, delay time, and area used through the inclusion of memory stages and a control mechanism, which resembled a pipeline [24]. However, this strategy is less efficient when more pipeline clock zones are utilised [25]. In 2019, Chaves et al. presented an alternative approach to designing partially reversible circuits in FCN technologies by considering layout alterations rather than timing modifications [26]. This approach relies on recycling one input signal for the logic gate. To our knowledge, this method has not yet been validated for QCA logic gate design.

For the first time, this study shows how to use a partially reversible design method to make a novel three-input partially reversible QCA majority gate. Figure 3 shows the proposed three-input partially reversible QCA majority gate, which recycles one input signal. The logic symbol diagram of this partially reversible majority gate is shown in Figure 3a, and the QCA layout design is shown in Figure 3b. The functionality of the three-input partially reversible majority gate is determined by setting one of its inputs to a binary value of 0 or 1, which determines whether the gate operates as an AND gate or an OR gate, respectively. For example, when the input C is set to 0, the gate is an AND gate, whereas when the input C is set to 1, the gate is an OR gate.

The novel partially reversible majority gate, as well as the conventional irreversible and reversible majority gates, are all used in the proposed hybrid design method to create hybrid QCA digital circuits.

Electronics **2024**, 13, 2760 5 of 24

Figure 3. Partially reversible QCA majority gate: (a) logic symbol diagram and (b) QCA layout.

Data synchronisation is essential for precise data transmission and accurate operation in digital logic circuits [27]. To manage the timing of QCA circuits, external clocks are employed to precisely adjust the tunnelling barriers between QCA cells [1,28,29]. This study integrates the universal, scalable, and efficient (USE) clocking scheme [29] with the proposed hybrid design method to synchronise the data transmission of hybrid QCA digital circuits. The USE clocking scheme has notable adaptability, so it can effectively meet the requirements of the designed QCA circuit. These requirements include the integration of feedback channels with various loop sizes, the establishment of common cell libraries, and simplified routing. The USE clocking system is divided into four time zones, designated 1 to 4. Each time zone is composed of 25 QCA cells, arranged in a five-by-five pattern, and each time zone corresponds to a unique period. A complete clock cycle is formed with these four time zones. Further details can be found in previous works [30–33].

In addition, wire crossing is a crucial issue in digital circuits. The proposed hybrid design method employs the multilayer approach developed by Bajec and Pecar [34] to address this issue.

### 3. Design of Hybrid QCA Half-Adder Circuits

A comprehensive case study is a valuable tool for demonstrating the practical applicability and effectiveness of the proposed hybrid design methodology in designing QCA digital circuits. In very-large-scale integration (VLSI) systems, the half-adder circuit is a fundamental building block for arithmetic operations. The circuit adds two single-bit binary numbers and generates the sum (S) and carry (C) outputs. This section presents the design of the half-adder circuit as a case study to demonstrate the effectiveness of the innovative hybrid design methodology.

The type and number of majority gates used to design a QCA circuit are critical aspects that can influence circuit specifications. In previous studies, only one type of majority gate, either the reversible majority gate [15,19] or the irreversible majority gate [35–40], was used in the design of QCA half-adder circuits. In terms of the number of majority gates used for designing a half-adder circuit, a few prior studies used five majority gates [37,39], whereas others used four majority gates [15,19,40]. In this case study, we developed hybrid QCA half-adder circuits by simultaneously using three types of majority gates: reversible, irreversible, and partially reversible. Furthermore, the total number of majority gates used to build these half-adders was four. By using the three different types of majority gates to represent the four majority gates that constitute the half-adder, we can obtain a total of 81 different possible combinations that can represent the same QCA half-adder circuit. Despite all these designs having the same functionality, each has unique specifications. The number of majority gates for each of the three types of majority gates used in the circuit determines the energy consumption, delay time, and area occupied. Thus, by changing the types of majority gates included in the circuit, the designer can achieve a higher level of control over the final specifications of the circuit.

Describing the 81 possible combinations that represent the hybrid QCA half-adder circuit is a large design configuration task. This section takes four distinct combinations of majority gates to design four different hybrid QCA half-adder circuits as a sample of the

Electronics **2024**, 13, 2760 6 of 24

full design configuration space. These four versions are sufficient to effectively illustrate the concept of the hybrid design methodology. The main difference between these four hybrid QCA half-adder circuits lies in the number of reversible, partially reversible, and irreversible majority gates employed in designing the half-adder circuit. The first proposed design of a hybrid QCA half-adder uses three fully reversible majority gates and one irreversible majority gate. The second proposed design uses two fully reversible majority gates, one partially reversible majority gate, and one irreversible majority gate. The third proposed design consists of two fully reversible and two irreversible majority gates. The fourth proposed design consists of two partially reversible and two irreversible majority gates. Table 1 lists the technological parameters used to develop the novel hybrid QCA half-adder circuits. To prevent wire junction issues, a multilayer approach with three distinct layers was used. Furthermore, we employed the USE clocking technique to synchronise the data transmission.

| <b>Table 1.</b> Technological and simulation pa | oarameters. |

|-------------------------------------------------|-------------|

|-------------------------------------------------|-------------|

| Parameter             | Description                                                                      | Value                             |

|-----------------------|----------------------------------------------------------------------------------|-----------------------------------|

| QD size               | Quantum dot size                                                                 | 5 nm                              |

| Cell area             | Dimensions of each cell                                                          | $18 \times 18 \text{ nm}$         |

| Cell distance         | Distance between two cells                                                       | 2 nm                              |

| Layer separation      | Distance between QCA layers in multilayer crossing                               | 11.5 nm                           |

| Clock high            | Max. saturation energy of the clock signal                                       | $9.8 \times 10^{-22}  \mathrm{J}$ |

| Clock low             | Min. saturation energy of the clock signal                                       | $3.8 \times 10^{-23} \text{ J}$   |

| Relative permittivity | Relative permittivity of the materials used in the QCA systems (GaAs and AlGaAs) | 12.9                              |

| Radius of effect      | Maximum distance between cells for which interactions are considered             | 80 nm                             |

| Temp                  | Operating temperature                                                            | 1 K                               |

| τ                     | Relaxation time                                                                  | $1 \times 10^{-15} \text{ s}$     |

| Τγ                    | Period of the clock signal                                                       | $1 \times 10^{-9} \text{ s}$      |

| Tin                   | Period of the input signals                                                      | $1 \times 10^{-9} \text{ s}$      |

| Tstep                 | Time interval of each iteration step                                             | $1 \times 10^{-16} \text{ s}$     |

| Tsim                  | Total simulation time                                                            | $8 \times 10^{-9} \text{ s}$      |

| $\gamma$ shape        | Shape of the clock signal slope                                                  | Gaussian                          |

| $\gamma_{ m slope}$   | Rise and fall time of the clock signal                                           | $1 \times 10^{-10} \text{ s}$     |

Equation (1) describes the Boolean expression, and Table 2 presents the truth table of the proposed hybrid QCA half-adder circuits.

**Table 2.** Hybrid QCA half-adder circuit truth table.

| A | В | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

$$Sum = (A.\overline{B}) + (\overline{A}.B)$$

$$Carry = (A.B)$$

(1)

3.1. First Hybrid QCA Half-Adder Design (Three Fully Reversible and One Irreversible Majority Gate)

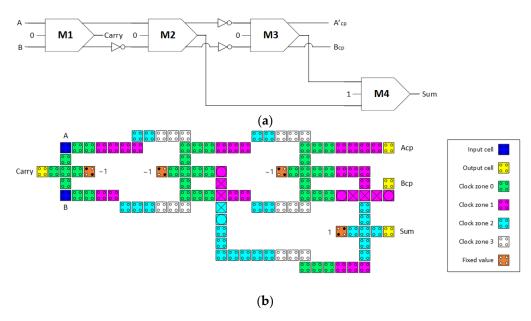

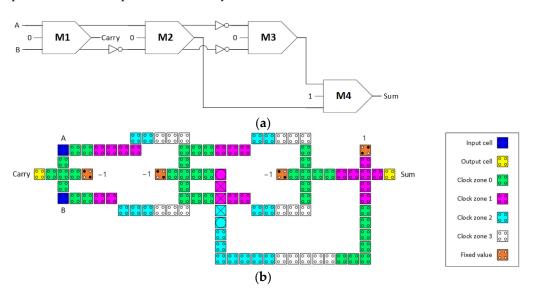

Figure 4 presents the first developed design of a hybrid QCA half-adder. The circuit uses three fully reversible majority gates (M1, M2, and M3) and one irreversible majority gate (M4). Figure 4a depicts the logic synthesis of this hybrid half-adder circuit, whereas Fig-

Electronics **2024**, 13, 2760 7 of 24

ure 4b displays the QCA layout. The circuit consists of 117 QCA cells, which occupy an area of  $0.16~\mu m^2$ . The measured latency is 11 clock phases, which is equal to 2.75 clock cycles.

Figure 4. First hybrid QCA half-adder circuit (a) logic synthesis and (b) QCA layout.

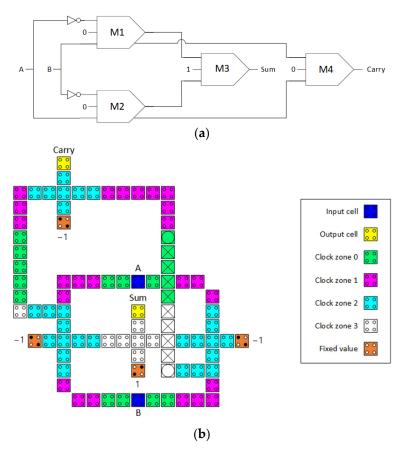

3.2. Second Hybrid QCA Half-Adder Design (Two Fully Reversible, One Partially Reversible, and One Irreversible Majority Gate)

Two fully reversible majority gates (M1 and M2), one partially reversible majority gate (M3), and one irreversible majority gate (M4) make up the second hybrid QCA half-adder circuit. Figure 5a shows the logic synthesis of this hybrid half-adder circuit, whereas Figure 5b shows the QCA layout. In the second design, the only modification compared with the first design is the change in the reversibility of one majority gate, M3, from fully to partially reversible. Consequently, there is a 6% decrease in the number of QCA cells compared to the first design, resulting in a total of 110 QCA cells in the second design. However, the occupied area and delay time are consistent with those of the first design, with an area of 0.16 m2 and a delay of 11 clock phases, equivalent to 2.75 clock cycles.

Figure 5. Second hybrid QCA half-adder circuit (a) logic synthesis and (b) QCA layout.

Electronics **2024**, 13, 2760 8 of 24

## 3.3. Third Hybrid QCA Half-Adder Design (Two Fully Reversible and Two Irreversible Majority Gates)

Figure 6 shows the third design for a hybrid QCA half-adder. The circuit is composed of two fully reversible majority gates (M1 and M2) and two irreversible majority gates (M3 and M4). Figure 6a depicts the logic synthesis of the third hybrid QCA half-adder circuit, whereas Figure 6b displays the QCA layout. In the third design, the only modification compared with the second design is the change in the reversibility of one majority gate, M3, from partially reversible to irreversible. As a result, the number of QCA cells decreases by 8.2%, the occupied area decreases by 18.8%, and the speed improves by 9% compared to those of the second design. For the third hybrid QCA half-adder, 101 QCA cells are used to build the circuit, which occupy an area of 0.13  $\mu m^2$ . The measured latency is 10 clock phases, which is equal to 2.5 clock cycles.

Figure 6. Third hybrid QCA half-adder circuit (a) logic synthesis and (b) QCA layout.

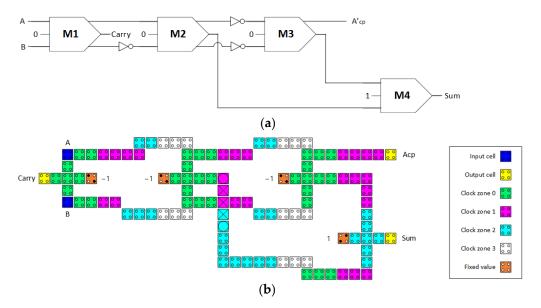

### 3.4. Fourth Hybrid QCA Half-Adder Design (Two Partially Reversible and Two Irreversible Majority Gates)

Figure 7 presents the fourth developed design of a hybrid QCA half-adder. Two partially reversible majority gates (M1 and M2) and two irreversible majority gates (M3 and M4) are used in the circuit. Figure 7a displays the logic synthesis of this hybrid half-adder circuit, while Figure 7b displays the QCA layout. The fourth design differs from the third design in that the reversibility of two majority gates, M1 and M2, changes from partially reversible to irreversible. As a result, compared with those of the third design, the number of QCA cells decreases by 11.9%, the occupied area decreases by 7.7%, and the speed significantly improves by 60%. The fourth hybrid QCA half-adder consists of 90 QCA cells, which occupy an area of 0.12  $\mu m^2$ . The measured latency is 4 clock phases, which is equal to 1 clock cycle.

Electronics **2024**, 13, 2760 9 of 24

Figure 7. Fourth hybrid QCA half-adder circuit (a) logic synthesis and (b) QCA layout.

### 4. Simulation Results

This section offers an in-depth examination of the hybrid QCA half-adder circuits discussed in Section 3, focusing on their performance reliability, information loss, energy dissipation, and circuit cost.

### 4.1. Performance Evaluation

We used the QCADesigner-E 2.2 simulation tool to simulate the input/output behaviour of the four presented hybrid QCA half-adder designs. QCADesigner-E 2.2 uses a microscopic quantum mechanical model of tunnelling inside a QCA cell, along with the intra- and intercell electrostatic interactions, and a density matrix description of energy dissipation within a phenomenological model [33]. Our earlier paper [18] provides more details on the energy dissipation treatment within the quantum mechanical coherence vector formalism for the density matrix.

To validate the reliability of the innovative hybrid design method for developing QCA digital circuits, we compared the simulated waveforms with the values in the truth table of the half-adder circuit given in Table 2.

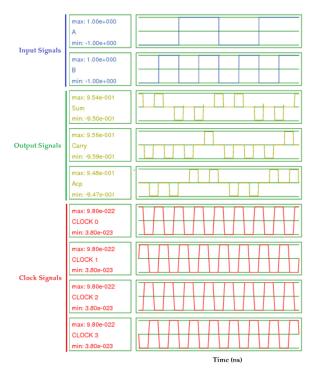

## 4.1.1. Simulated Waveforms of the First Hybrid (Three Fully Reversible and One Irreversible Majority Gate) QCA Half-Adder Design

Figure 8 shows the simulated waveforms of the first hybrid QCA half-adder design. The polarisation output corresponds to the truth table values in Table 2, thus confirming the performance reliability of the first hybrid QCA half-adder design.

Figure 8. Simulated waveforms of the first hybrid QCA half-adder design.

4.1.2. Simulated Waveforms of the Second Hybrid (Two Fully Reversible, One Partially Reversible, and One Irreversible Majority Gate) QCA Half-Adder Design

Figure 9 illustrates the simulated waveforms of the second hybrid QCA half-adder design. The polarisation output accurately matches the half-adder truth table values in Table 2, confirming the performance reliability of the second hybrid QCA half-adder design.

Figure 9. Simulated waveforms of the second hybrid QCA half-adder design.

## 4.1.3. Simulated Waveforms of the Third Hybrid (Two Fully Reversible and Two Irreversible Majority Gates) QCA Half-Adder Design

Figure 10 depicts the simulated waveforms of the third hybrid QCA half-adder design. The polarisation output exactly matches the truth table values in Table 2, proving that the third hybrid QCA half-adder design is reliable.

Figure 10. Simulated waveforms of the third hybrid QCA half-adder design.

## 4.1.4. Simulated Waveforms of the Fourth Hybrid (Two Partially Reversible and Two Irreversible Majority Gates) QCA Half-Adder Design

Figure 11 displays the simulated waveforms of the fourth hybrid QCA half-adder design. The polarisation output precisely matches the truth table values in Table 2, proving the performance reliability of the fourth hybrid QCA half-adder design.

### 4.2. Information Dissipation Calculation

This section presents calculations of the information dissipation for the hybrid QCA half-adder circuits considered. Shannon's entropy is a key concept in information theory that quantifies the level of information contained within a set of possible outcomes [41]. Various disciplines, including telecommunications, encryption, and data compression, commonly employ Shannon's entropy. Thus, Shannon's entropy was used to calculate the total amount of information dissipated in each of the four hybrid QCA half-adder circuits presented in this study. The formula for Shannon's entropy H(X) for a discrete random variable X with possible values of  $x_1, x_2, x_3, \ldots, x_n$  is given by Equation (2):

$$H(X) = -\sum_{i=1}^{n} P(x_i) \times \log_2 P(x_i),$$

(2)

where  $P(x_i)$  is the probability of outcome  $x_i$ , and  $\log_2$  is the logarithm of the two-bit entropy.

Figure 11. Simulated waveforms of the fourth hybrid QCA half-adder design.

To determine the amount of information lost in each gate, we measured the difference between Shannon's entropy for the probability distributions of the initial and final states of the gates, i.e., H(X) - H(Y), where the entropy H(X) of X is the summation of the contributions of all initial states, and the entropy H(Y) of Y is the summation of the contributions of all the final states. Finally, the total information dissipated in a circuit is computed by summing the information lost for the gates comprising the circuit using Equation (3).

$$T = \sum_{i=1}^{n} H(X_i),\tag{3}$$

where n is the number of gates used to construct the circuit.

## 4.2.1. Information Dissipation of the First Hybrid (Three Fully Reversible and One Irreversible Majority Gate) QCA Half-Adder Design

First, we calculated Shannon's entropy using Equation (2) to define the amount of information lost for each gate in the first design. This design consists of three fully reversible majority gates (M1, M2, and M3) and one irreversible gate (M4), as illustrated in Figure 4. Table 3 provides a comprehensive breakdown of the Shannon's entropy calculations for all gates in the first design. Table 3a–c show that the fully reversible majority gates M1, M2, and M3 recycle all the information without any information loss. Table 3d, in contrast, shows that the irreversible majority gate M4 loses 0.5 bits of information. Next, we used Equation (3) to compute the total amount of information lost in the first design. Equation (3) aggregates the Shannon's entropy lost from all the majority gates that form the circuit. According to Table 3, the information loss of the first design is solely attributable to the irreversible majority gate M4. Thus, the total amount of information lost in the first design is equivalent to the M4 information loss, which is 0.5 bits.

1

*H*(

$x_2 \\ x_3$

Table 3. Information dissipation calculation for the first hybrid QCA half-adder design.

|                       |              |                     |          | (a       | a) Gate               | M1                   |          |                     |          |          |

|-----------------------|--------------|---------------------|----------|----------|-----------------------|----------------------|----------|---------------------|----------|----------|

|                       |              | Input               |          |          |                       |                      |          |                     |          |          |

| $x_i$                 | A            | В                   | $P(x_i)$ | $H(x_i)$ | $y_i$                 | carry                | $A_{cp}$ | $B_{cp}$            | $P(y_i)$ | $H(y_i)$ |

| $x_0$                 | 0            | 0                   | 1/4      | 0.5      | $y_0$                 | 0                    | 0        | 0                   | 1/4      | 0.5      |

| $x_1$                 | 0            | 1                   | 1/4      | 0.5      | $y_1$                 | 0                    | 0        | 1                   | 1/4      | 0.5      |

| $x_2$                 | 1            | 0                   | 1/4      | 0.5      | $y_2$                 | 0                    | 1        | 0                   | 1/4      | 0.5      |

| $x_3$                 | 1            | 1                   | 1/4      | 0.5      | <i>y</i> 3            | 1                    | 1        | 1                   | 1/4      | 0.5      |

| -                     | Н            | I(X)                |          | 2        |                       |                      | H(       | Y)                  |          | 2        |

|                       |              |                     |          | H(X      | X) - H                | (Y) = 0              |          |                     |          |          |

|                       |              |                     |          | (l       | ) Gate                | M2                   |          |                     |          |          |

|                       | Input Output |                     |          |          |                       |                      |          | tput                |          |          |

| $x_i$                 | $A_{cp}$     | $\overline{B}_{cp}$ | $P(x_i)$ | $H(x_i)$ | $y_i$                 | M2 <sub>output</sub> | $A_{cp}$ | $\overline{B}_{cp}$ | $P(y_i)$ | $H(y_i)$ |

| $\overline{x_0}$      | 0            | 1                   | 1/4      | 0.5      | <i>y</i> <sub>0</sub> | 0                    | 0        | 1                   | 1/4      | 0.5      |

| <i>x</i> <sub>1</sub> | 0            | 0                   | 1/4      | 0.5      | V <sub>1</sub>        | 0                    | 0        | 0                   | 1/4      | 0.5      |

| 1 $\frac{1}{4}$ 0.5 $\frac{1}{4}$ 1 1 1 $\frac{1}{4}$   | _ | <br>0.0 |     |   |        |        |     |  |

|---------------------------------------------------------|---|---------|-----|---|--------|--------|-----|--|

| $0 	 \frac{1}{4} 	 0.5 	 y_1 	 0 	 0 	 0 	 \frac{1}{4}$ | 1 |         | 0 - | 1 | 0<br>1 | 0<br>1 | 0.5 |  |

H(X) - H(Y) = 0

#### (c) Gate M3

|       |                     | Input    |          |          |                       | Output               |                     |          |          |          |  |

|-------|---------------------|----------|----------|----------|-----------------------|----------------------|---------------------|----------|----------|----------|--|

| $x_i$ | $\overline{A}_{cp}$ | $B_{cp}$ | $P(x_i)$ | $H(x_i)$ | $y_i$                 | M3 <sub>output</sub> | $\overline{A}_{cp}$ | $B_{cp}$ | $P(y_i)$ | $H(y_i)$ |  |

| $x_0$ | 1                   | 0        | 1/4      | 0.5      | <i>y</i> <sub>0</sub> | 0                    | 1                   | 0        | 1/4      | 0.5      |  |

| $x_1$ | 1                   | 1        | 1/4      | 0.5      | $y_1$                 | 1                    | 1                   | 1        | 1/4      | 0.5      |  |

| $x_2$ | 0                   | 0        | 1/4      | 0.5      | $y_2$                 | 0                    | 0                   | 0        | 1/4      | 0.5      |  |

| $x_3$ | 0                   | 1        | 1/4      | 0.5      | <i>y</i> 3            | 0                    | 0                   | 1        | 1/4      | 0.5      |  |

|       | Н                   | I(X)     |          | 2        |                       |                      | H(                  | Y)       |          | 2        |  |

# $\frac{H(X) - H(Y) = 0}{\text{(d) Gate M4}}$

|       |                      | Input                |          |          |                       | Output |          |          |

|-------|----------------------|----------------------|----------|----------|-----------------------|--------|----------|----------|

| $x_i$ | M2 <sub>output</sub> | M3 <sub>output</sub> | $P(x_i)$ | $H(x_i)$ | $y_i$                 | sum    | $P(y_i)$ | $H(y_i)$ |

| $x_0$ | 0                    | 0                    | 1/       | 0.5      | <i>y</i> <sub>0</sub> | 0      | 1/       | 0.5      |

| $x_1$ | 0                    | 1                    | 1/2      | 0.5      | $y_1$                 | 1      | 1/2      | 0.5      |

| $x_2$ | 1                    | 0                    | 1/4      | 0.5      | $y_2$                 | 1      | 1/       | 0.5      |

| $x_3$ | 0                    | 0                    | 1/4      | 0.5      | <i>y</i> <sub>3</sub> | 0      | 1/2      | 0.5      |

|       |                      |                      | H(X)     | 1.5      |                       |        | H(Y)     | 1        |

|       |                      |                      |          | H(X)     | )-H(Y)=0.5            |        |          |          |

## 4.2.2. Information Dissipation of the Second Hybrid (Two Fully Reversible, One Partially Reversible, and One Irreversible Majority Gate) QCA Half-Adder Design

Initially, we calculated Shannon's entropy using Equation (2) to define the amount of information lost for each gate in the second design. This design consists of two fully reversible majority gates (M1 and M2), one partially reversible gate (M3), and one irreversible gate (M4), as illustrated in Figure 5. Table 4 provides a comprehensive breakdown of the Shannon's entropy calculations for all gates in the second design. Table 4a,b show that the fully reversible majority gates M1 and M2 recycle all the information without any information loss. In contrast, Table 4c,d show that the partially reversible majority gate M3 and the irreversible majority gate M4 lose 0.5 bits of information each. According to Table 4, the information loss of the second design is attributable to the partially reversible

Electronics 2024, 13, 2760 14 of 24

> majority gate M3 and irreversible majority gate M4. Thus, the total amount of information lost in the second design is equivalent to the summation of the M3 and M4 information losses, which is 1 bit.

Table 4. Information dissipation calculation for the second hybrid QCA half-adder design.

|         |                      |                      |          | (a       | ) Gate I              | <b>M</b> 1          |          |                     |          |          |

|---------|----------------------|----------------------|----------|----------|-----------------------|---------------------|----------|---------------------|----------|----------|

|         |                      | Input                |          |          |                       |                     | Ou       | tput                |          |          |

| $x_i$   | A                    | В                    | $P(x_i)$ | $H(x_i)$ | $y_i$                 | carry               | $A_{cp}$ | $B_{cp}$            | $P(y_i)$ | $H(y_i)$ |

| $x_0$   | 0                    | 0                    | 1/4      | 0.5      | <i>y</i> <sub>0</sub> | 0                   | 0        | 0                   | 1/4      | 0.5      |

| $x_1$   | 0                    | 1                    | 1/4      | 0.5      | $y_1$                 | 0                   | 0        | 1                   | 1/4      | 0.5      |

| $x_2$   | 1                    | 0                    | 1/4      | 0.5      | $y_2$                 | 0                   | 1        | 0                   | 1/4      | 0.5      |

| $x_3^-$ | 1                    | 1                    | 1/4      | 0.5      | $y_3$                 | 1                   | 1        | 1                   | 1/4      | 0.5      |

|         |                      |                      | H(X)     | 2        |                       |                     |          |                     | H(Y)     | 2        |

|         |                      |                      |          | H(X      | ) – H()               | ()=0                |          |                     |          |          |

|         |                      |                      |          | (b       | ) Gate I              | M2                  |          |                     |          |          |

|         |                      | Input                |          |          |                       |                     | Ou       | tput                |          |          |

| $x_i$   | $A_{cp}$             | $\overline{B}_{cp}$  | $P(x_i)$ | $H(x_i)$ | $y_i$                 | M2 <sub>outpu</sub> | t Acp    | $\overline{B}_{cp}$ | $P(y_i)$ | $H(y_i)$ |

| $x_0$   | 0                    | 1                    | 1/4      | 0.5      | <i>y</i> <sub>0</sub> | 0                   | 0        | 1                   | 1/4      | 0.5      |

| $x_1$   | 0                    | 0                    | 1/4      | 0.5      | $y_1$                 | 0                   | 0        | 0                   | 1/4      | 0.5      |

| $x_2$   | 1                    | 1                    | 1/4      | 0.5      | $y_2$                 | 1                   | 1        | 1                   | 1/4      | 0.5      |

| $x_3$   | 1                    | 0                    | 1/4      | 0.5      | <i>y</i> <sub>3</sub> | 0                   | 1        | 0                   | 1/4      | 0.5      |

|         |                      |                      | H(X)     | 2        |                       |                     |          |                     | H(Y)     | 2        |

|         |                      |                      |          | H(X      | ) – H()               | () = $0$            |          |                     |          |          |

|         |                      |                      |          | (c)      | ) Gate I              | М3                  |          |                     |          |          |

|         |                      | Input                |          |          |                       |                     | Ou       | tput                |          |          |

| $x_i$   | $\overline{A}_{cp}$  | $B_{cp}$             | $P(x_i)$ | $H(x_i)$ | $y_i$                 | $M3_{oi}$           | ıtput    | $\overline{A}_{cp}$ | $P(y_i)$ | $H(y_i)$ |

| $x_0$   | 1                    | 0                    | 1/4      | 0.5      | $y_0$                 | C                   |          | 1                   | 1/4      | 0.5      |

| $x_1$   | 1                    | 1                    | 1/4      | 0.5      | $y_1$                 | 1                   |          | 1                   | 1/4      | 0.5      |

| $x_2$   | 0                    | 0                    | 1/4      | 0.5      | $y_2$                 | C                   | )        | 0                   | 1/       |          |

| $x_3$   | 0                    | 1                    | 1/4      | 0.5      | $y_3$                 | C                   | )        | 0                   | 1/2      | 0.5      |

|         |                      |                      | H(X)     | 2        |                       |                     |          |                     | H(Y)     | 1.5      |

|         |                      |                      |          | H(X)     | -H(Y)                 | ) = 0.5             |          |                     |          |          |

|         |                      |                      |          | (d       | ) Gate I              | M4                  |          |                     |          |          |

|         |                      | Input                |          |          |                       |                     | Ou       | tput                |          |          |

| $x_i$   | M2 <sub>output</sub> | M3 <sub>output</sub> | $P(x_i)$ | $H(x_i)$ | $y_i$                 |                     | sum      |                     | $P(y_i)$ | $H(y_i)$ |

| $x_0$   | 0                    | 0                    | 1/2      | 0.5      | $y_0$                 |                     | 0        |                     | 1/2      | 0.5      |

| $x_1$   | 0                    | 1                    |          |          | $y_1$                 |                     | 1        |                     | /2       | 0.5      |

| $x_2$   | 1                    | 0                    | 1/4      | 0.5      | $y_2$                 |                     | 1        |                     | 1/2      | 0.5      |

| • •     | Ω                    | Ω                    | 1./.     | 0.5      | 4.                    |                     | Λ        |                     | 72       | 0.5      |

### 4.2.3. Information Dissipation of the Third Hybrid (Two Fully Reversible and Two Irreversible Majority Gates) QCA Half-Adder Design

0.5

1.5

0

$x_3$

0

$\frac{1}{4}$

H(X)

First, we calculated Shannon's entropy using Equation (2) to define the amount of information lost for each gate in the third design. This design consists of two fully reversible majority gates (M1 and M2) and two irreversible majority gates (M3 and M4), as illustrated in Figure 6. Table 5 provides a comprehensive breakdown of the Shannon's entropy calculations for all gates in the third design. Table 5a,b demonstrate that the fully reversible

*y*<sub>3</sub>

H(X) - H(Y) = 0.5

H(Y)

0

1

majority gates M1 and M2 recycle all the information without any information loss. In contrast, Table 5c,d show that the irreversible majority gates M3 and M4 lose 1.19 bits and 0.5 bits of information, respectively. Next, we used Equation (3) to compute the total amount of information lost in the third design. According to Table 4, the information loss of the third design is attributable to the irreversible majority gates M3 and M4. Thus, the total amount of information lost in the third design is equivalent to the summation of the M3 and M4 information losses, which is 1.69 bits.

|                       |                     |                      |               | (a       | ) Gate I              | И1                   |                      |                     |               |          |

|-----------------------|---------------------|----------------------|---------------|----------|-----------------------|----------------------|----------------------|---------------------|---------------|----------|

|                       |                     | Input                |               |          |                       |                      | Out                  | tput                |               |          |

| $x_i$                 | A                   | В                    | $P(x_i)$      | $H(x_i)$ | $y_i$                 | carry                | $A_{cp}$             | $B_{cp}$            | $P(y_i)$      | $H(y_i)$ |

| $x_0$                 | 0                   | 0                    | 1/4           | 0.5      | <i>y</i> <sub>0</sub> | 0                    | 0                    | 0                   | 1/4           | 0.5      |

| $x_1$                 | 0                   | 1                    | 1/4           | 0.5      | $y_1$                 | 0                    | 0                    | 1                   | 1/4           | 0.5      |

| $x_2$                 | 1                   | 0                    | 1/4           | 0.5      | $y_2$                 | 0                    | 1                    | 0                   | 1/4           | 0.5      |

| <i>x</i> <sub>3</sub> | 1                   | 1                    | 1/4           | 0.5      | <i>y</i> <sub>3</sub> | 1                    | 1                    | 1                   | 1/4           | 0.5      |

|                       |                     |                      | H(X)          | 2        |                       |                      |                      |                     | H(Y)          | 2        |

|                       |                     |                      |               | H(X      | )-H()                 | ()=0                 |                      |                     |               |          |

|                       |                     |                      |               | (b       | ) Gate I              | М2                   |                      |                     |               |          |

|                       |                     | Input                |               |          |                       |                      | Out                  | tput                |               |          |

| $x_i$                 | $A_{cp}$            | $\overline{B}_{cp}$  | $P(x_i)$      | $H(x_i)$ | $y_i$                 | M2 <sub>output</sub> | $A_{cp}$             | $\overline{B}_{cp}$ | $P(y_i)$      | $H(y_i)$ |

| $x_0$                 | 0                   | 1                    | 1/4           | 0.5      | $y_0$                 | 0                    | 0                    | 1                   | 1/4           | 0.5      |

| $x_1$                 | 0                   | 0                    | $\frac{1}{4}$ | 0.5      | $y_1$                 | 0                    | 0                    | 0                   | 1/4           | 0.5      |

| $x_2$                 | 1                   | 1                    | 1/4           | 0.5      | $y_2$                 | 1                    | 1                    | 1                   | $\frac{1}{4}$ | 0.5      |

| <i>x</i> <sub>3</sub> | 1                   | 0                    | 1/4           | 0.5      | <i>y</i> <sub>3</sub> | 0                    | 1                    | 0                   | 1/4           | 0.5      |

|                       |                     |                      | H(X)          | 2        |                       |                      |                      |                     | H(Y)          | 2        |

|                       |                     |                      |               |          | ) – H(Y               |                      |                      |                     |               |          |

|                       |                     |                      |               | (c)      | Gate N                | <b>/13</b>           |                      |                     |               |          |

|                       |                     | Input                |               |          |                       |                      |                      | tput                |               |          |

| $x_i$                 | $\overline{A}_{cp}$ | $B_{cp}$             | $P(x_i)$      | $H(x_i)$ | $y_i$                 | <i>N</i> .           | I3 <sub>output</sub> |                     | $P(y_i)$      | $H(y_i)$ |

| $x_0$                 | 1                   | 0                    | 1/4           | 0.5      | $y_0$                 |                      | 0                    |                     | 1/4           | 0.5      |

| $x_1$                 | 1                   | 1                    | 1/4           | 0.5      | $y_1$                 |                      | 1                    |                     |               |          |

| $x_2$                 | 0                   | 0                    | 1/4           | 0.5      | $y_2$                 |                      | 0                    |                     | 3/4           | 0.31     |

| <i>x</i> <sub>3</sub> | 0                   | 1                    | 1/4           | 0.5      | $y_3$                 |                      | 0                    |                     |               |          |

|                       |                     |                      | H(X)          | 2        |                       |                      |                      |                     | H(Y)          | 0.81     |

|                       |                     |                      |               |          | $\frac{-H(Y)}{X}$     |                      |                      |                     |               |          |

|                       |                     | Input                |               | (a       | ) Gate I              | V14                  | 0                    | tput                |               |          |

| $x_i$                 | M2 outmut           | M3 <sub>output</sub> | $P(x_i)$      | $H(x_i)$ | $y_i$                 |                      | sum                  | iput                | $P(y_i)$      | $H(y_i)$ |

| $\frac{x_i}{x_0}$     | 0                   | 0                    |               |          | $y_0$                 |                      | 0                    |                     |               |          |

| $x_1$                 | 0                   | 1                    | 1/2           | 0.5      | $y_1$                 |                      | 1                    |                     | 1/2           | 0.5      |

| $x_2$                 | 1                   | 0                    | 1/4           | 0.5      | <i>y</i> <sub>2</sub> |                      | 1                    |                     | 1/            | 0.5      |

| $x_3$                 | 0                   | 0                    | 1/4           | 0.5      | <i>y</i> 3            |                      | 0                    |                     | 1/2           | 0.5      |

H(X)

1.5

H(X) - H(Y) = 0.5

H(Y)

Electronics 2024, 13, 2760 16 of 24

### 4.2.4. Information Dissipation of the Fourth Hybrid (Two Partially Reversible and Two Irreversible Majority Gates) QCA Half-Adder Design

Initially, we calculated Shannon's entropy using Equation (2) to define the amount of information lost for each gate in the fourth design. This design consists of two partially reversible majority gates (M1 and M2) and two irreversible majority gates (M3 and M4), as illustrated in Figure 7. Table 6 provides a comprehensive breakdown of the Shannon's entropy calculations for all gates in the fourth design. Table 5a-d show that the partially reversible majority gates M1 and M2 and the irreversible majority gates M3 and M4 lose 0.5, 0.5, 0.5, and 1.19 bits of information, respectively. Next, we used Equation (3) to compute the total amount of information lost in the fourth design. According to Table 4, the information loss of the fourth design is attributable to the partially reversible majority gates M1 and M2 and irreversible majority gates M3 and M4. Thus, the total amount of information lost in the fourth design is equivalent to the summation of the M1, M2, M3, and M4 information losses, which is 2.69 bits.

|                       |                  |                      |               | (a) Gat  | te M1                 |                      |          |          |          |

|-----------------------|------------------|----------------------|---------------|----------|-----------------------|----------------------|----------|----------|----------|

|                       |                  | Input                |               |          |                       |                      | Output   |          |          |

| $x_i$                 | $\overline{A}$   | В                    | $P(x_i)$      | $H(x_i)$ | $y_i$                 | M1 <sub>output</sub> | $B_{cp}$ | $P(y_i)$ | $H(y_i)$ |

| $x_0$                 | 1                | 0                    | 1/4           | 0.5      | <i>y</i> <sub>0</sub> | 0                    | 0        | 1/       | 0.5      |

| $x_1$                 | 1                | 1                    | 1/4           | 0.5      | $y_1$                 | 1                    | 1        | 1/2      | 0.5      |

| $x_2$                 | 0                | 0                    | 1/4           | 0.5      | $y_2$                 | 0                    | 0        | 1/4      | 0.5      |

| $x_3$                 | 0                | 1                    | 1/4           | 0.5      | <i>y</i> <sub>3</sub> | 0                    | 1        | 1/4      | 0.5      |

|                       |                  |                      | H(X)          | 2        |                       |                      |          | H(Y)     | 1.5      |

|                       |                  |                      |               | H(X) - H | (Y) = 0.5             |                      |          |          |          |

|                       |                  |                      |               | (b) Ga   | te M2                 |                      |          |          |          |

|                       |                  | Input                |               |          |                       |                      | Output   |          |          |

| $x_i$                 | $\boldsymbol{A}$ | $\overline{B}$       | $P(x_i)$      | $H(x_i)$ | $y_i$                 | $M2_{output}$        | $A_{cp}$ | $P(y_i)$ | H(y)     |

| $x_0$                 | 0                | 1                    | 1/4           | 0.5      | $y_0$                 | 0                    | 1        | 1/2      | 0.5      |

| $x_1$                 | 0                | 0                    | 1/4           | 0.5      | $y_1$                 | 0                    | 0        |          |          |

| $x_2$                 | 1                | 1                    | $\frac{1}{4}$ | 0.5      | $y_2$                 | 1                    | 1        | 1/4      | 0.5      |

| <i>x</i> <sub>3</sub> | 1                | 0                    | 1/4           | 0.5      | <i>y</i> <sub>3</sub> | 0                    | 0        | 1/4      | 0.5      |

|                       |                  |                      | H(X)          | 2        |                       |                      |          | H(Y)     | 1.5      |

|                       |                  |                      |               | H(X) - H | (Y) = 0.5             |                      |          |          |          |

|                       |                  |                      |               | (c) Gat  | e M3                  |                      |          |          |          |

|                       |                  | Input                |               |          |                       |                      | Output   |          |          |

| $x_i$                 | $M1_{output}$    | M2 <sub>output</sub> | $P(x_i)$      | $H(x_i)$ | $y_i$                 | sun                  | n        | $P(y_i)$ | H(y      |

| $x_0$                 | 0                | 0                    | 1/2           | 0.5      | $y_0$                 | 0                    |          | 1/2      | 0.5      |

| $x_1$                 | 1                | 0                    |               |          | $y_1$                 | 1                    |          | 72       | 0.0      |

| $x_2$                 | 0                | 1                    | 1/4           | 0.5      | $y_2$                 | 1                    |          | 1/2      | 0.5      |

| <i>x</i> <sub>3</sub> | 0                | 0                    | 1/4           | 0.5      | $y_3$                 | 0                    |          |          |          |

|                       |                  |                      | H(X)          | 1.5      |                       |                      |          | H(Y)     | 1        |

|                       |                  |                      |               | H(X) - H | ` '                   |                      |          |          |          |

|                       |                  |                      |               | (d) Ga   | te M4                 |                      |          |          |          |

|                       |                  | Input                |               |          |                       |                      | Output   |          |          |

| $x_i$                 | $A_{cp}$         | $B_{cp}$             | $P(x_i)$      | $H(x_i)$ | $y_i$                 | carı                 | у        | $P(y_i)$ | H(y)     |

| $x_0$                 | 0                | 0                    | 1/4           | 0.5      | $y_0$                 | 0                    |          |          |          |

| $x_1$                 | 0                | 1                    | 1/4           | 0.5      | $y_1$                 | 0                    |          | 3/4      | 0.3      |

| $x_2$                 | 1                | 0                    | 1/4           | 0.5      | $y_2$                 | 0                    |          | 1/       |          |

| <i>x</i> <sub>3</sub> | 1                | 1                    | 1/4           | 0.5      | <i>y</i> <sub>3</sub> | 1                    |          | 1/4      | 0.5      |

|                       |                  |                      | H(X)          | 2        |                       |                      |          | H(Y)     | 0.8      |

|                       |                  |                      | ()            | _        |                       |                      |          | 11(1)    | 0.0      |

H(X) - H(Y) = 1.19

Electronics 2024, 13, 2760 17 of 24

### 4.2.5. Summary of Information Dissipated in the Hybrid QCA Half-Adder Designs

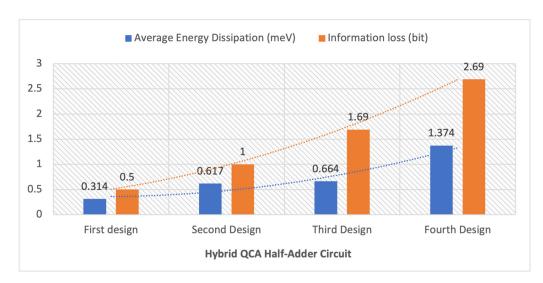

Table 7 presents a summary of the information dissipation of the four hybrid half-adder designs discussed earlier in this section.

| Proposed Half-Adder Design - | Nu               | Information I are    |              |                                      |

|------------------------------|------------------|----------------------|--------------|--------------------------------------|

| Proposed Hall-Adder Design   | Fully Reversible | Partially Reversible | Irreversible | <ul> <li>Information Loss</li> </ul> |

| First design                 | 3                | 0                    | 1            | 0.5                                  |

| Second design                | 2                | 1                    | 1            | 1                                    |

| Third design                 | 2                | 0                    | 2            | 1.69                                 |

2

0

Fourth design

Table 7. Information dissipation of the proposed hybrid QCA half-adder designs.

Table 7 demonstrates that a reduction in circuit reversibility can lead to an increase in information loss. Simply stated, replacing a reversible majority gate with an irreversible or partially reversible gate, or replacing a partially reversible majority gate with an irreversible gate, will result in a greater loss of information in the circuit.

2

2.69

The first hybrid QCA half-adder design uses three fully reversible majority gates (M1, M2, and M3) and one irreversible majority gate (M4), resulting in a loss of 0.5 bits of information.

The second hybrid QCA half-adder design uses two fully reversible majority gates (M1 and M2), one partially reversible majority gate (M3), and one irreversible majority gate (M4). The only alteration compared to the first design is a change in the reversibility of the third majority gate (M3) from fully reversible to partially reversible. The substitution of the third reversible majority gate (M3) with a partially reversible gate results in a twofold increase in information dissipation, from 0.5 bits to 1 bit, compared to the first design.

The third hybrid QCA half-adder design uses two fully reversible majority gates (M1 and M2) and two irreversible majority gates (M3 and M4). The only change from the second design is the substitution of the third majority gate (M3). The third majority gate (M3) has changed from being partially reversible in the second design to becoming irreversible in the third design. In comparison with the second design, changing the third majority gate (M3) results in an increase in information loss, from 1 bit to 1.69 bits. This implies a 0.69-bit increase in information loss, which equates to 69%. Compared to the first design, the third design shows an increase in information loss, from 0.5 bits to 1.69 bits. This implies a 1.19-bit increase in information loss, which equates to 238%.

The fourth hybrid QCA half-adder design uses two partially reversible majority gates (M1 and M2) and two irreversible majority gates (M3 and M4). The fourth design exhibits a 1-bit increase in information dissipation compared to the third design, rising from 1.69 bits to 2.69 bits, which corresponds to a 59% increase. In comparison to the second design, the fourth design demonstrates a 1.69-bit increase in information dissipation, representing a 169% increase from 1 bit to 2.69 bits. Compared to the first design, the fourth design achieves a substantial rise in information dissipation with a 2.19-bit increase, which is equivalent to a 438% increase from 0.5 bits to 2.69 bits.

### 4.3. Energy Dissipation Simulation

Precise calculations of energy dissipation are essential for evaluating the efficiency of QCA circuits. In QCA, energy efficiency is crucial because it enables a promising solution for realising low-power computing, which is a major challenge in contemporary electronic architecture. An in-depth assessment of circuit energy management is essential for improving circuit design and performance, since the circuit involves the dissipation of energy between the clock, cells, and environment.

This study used the QCADesigner-E 2.2 [33] simulation tool to evaluate the energy dissipation in hybrid QCA half-adder circuits. QCADesigner-E extends the well-known QCA simulation tool QCADesigner specifically for detailed analysis of energy dissipation

within QCA circuits. This tool provides a mechanism for evaluating the energy dissipation to the surrounding environment by solving the ordinary differential equations for the coherence vector description of the density matrix [33]. A small time step helps reduce simulation errors, leading to more accurate results. The time step  $(T_{\text{step}})$  for each iteration of the simulation was set to 0.1 fs in this study. This led to a simulation error tolerance of approximately 5%. This approach strikes a balance between the need for precision and the practical aspects of the simulation run time, ensuring that the simulation remains computationally feasible. This value is a practical threshold taken to reduce the CPU time for numerical simulations. However, the time step is low enough to ensure that the results are still meaningful, in terms of having the necessary degree of numerical energy conservation, and thus useful for design evaluation. Managing and understanding these errors is critical for improving simulation models and interpreting simulation results. Table 1 presents a comprehensive description of the technological and simulation parameters used in this study to simulate energy dissipation.

Table 8 shows the simulation results for the energy dissipation of the innovative, partially reversible QCA majority gate. Additionally, Table 8 illustrates the energy losses associated with both the fully reversible and irreversible majority gates that are commonly used in QCA digital circuit construction. The simulation results show that the fully reversible QCA majority gate reported in reference [19] uses 93% less energy than the partially reversible QCA majority gate suggested in this work. Additionally, the partially reversible QCA majority gate introduced in this study consumes 92% less energy than the conventional irreversible majority gate.

**Table 8.** Energy dissipation values for majority gates with different levels of reversibility.

| QCA Majority Gate -                                 | Energy Dissipation for an Input Combination Signal [meV] |                |                |                |                |                |                |                |  |

|-----------------------------------------------------|----------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|

| QCA Majority Gate                                   | 000                                                      | 001            | 010            | 011            | 100            | 101            | 110            | 111            |  |

| Standard irreversible [19]<br>Fully reversible [19] | 0.001<br>0.003                                           | 0.709<br>0.003 | 0.714<br>0.003 | 0.711<br>0.003 | 0.709<br>0.003 | 0.714<br>0.003 | 0.711<br>0.003 | 0.001<br>0.003 |  |

| Proposed partially reversible (Figure 3b)           | 0.002                                                    | 0.052          | 0.052          | 0.053          | 0.053          | 0.053          | 0.052          | 0.002          |  |

The energy dissipation simulation results for the novel hybrid QCA half-adder circuits are shown in Table 9. The energy dissipation values of all the designs were simulated using QCADesigner-E by employing the simulation and technological parameters presented in Table 1.

**Table 9.** Energy dissipation values for the proposed hybrid QCA half-adder circuits.

| Proposed Hybrid QCA | Energy 1 | Dissipation for<br>Signal | an Input Com<br>[meV] | Total Energy | Average Energy                      |                   |  |

|---------------------|----------|---------------------------|-----------------------|--------------|-------------------------------------|-------------------|--|

| Half-Adder Design – | 00       | 01                        | 10                    | 11           | <ul><li>Dissipation [meV]</li></ul> | Dissipation [meV] |  |

| First design        | 0.367    | 0.283                     | 0.378                 | 0.228        | 1.256                               | 0.314             |  |

| Second design       | 0.550    | 0.641                     | 0.635                 | 0.641        | 2.467                               | 0.617             |  |

| Third design        | 0.646    | 0.641                     | 0.726                 | 0.642        | 2.655                               | 0.664             |  |

| Fourth design       | 1.470    | 1.310                     | 1.250                 | 1.466        | 5.496                               | 1.374             |  |

The simulation findings on the energy dissipation in the hybrid QCA half-adder circuits indicate that the use of majority gates with a higher level of reversibility, which can recycle more input data, can lead to a decrease in the energy dissipation of the QCA circuit. To compare the energy dissipation results for the hybrid QCA half-adder circuits under study, we calculated the average energy dissipation values. The average energy dissipation represents the average energy dissipation value across all input signal combinations in a

circuit. Table 9 shows the total and average energy dissipation calculations for the proposed hybrid QCA half-adder circuits.

The first design of the QCA half-adder circuit utilises three reversible majority gates (M1, M2, and M3) and one irreversible majority gate (M4), resulting in an average energy dissipation of 0.314 meV per operation.

The average energy dissipation of the hybrid QCA half-adder circuit increases by 97% to 0.617 meV when the third majority gate (M3) changes from fully reversible in the first design to partially reversible in the second design.

In the third design of the hybrid QCA half-adder circuit, the energy dissipation further increases. The average energy dissipation in the third design increases by 6.7% to 0.664 meV when the third majority gate (M3) is changed from partially reversible in the second design to irreversible in the third design.

In the fourth design of the hybrid QCA half-adder circuit, there is a significant increase in energy dissipation. Compared to the third design, the average energy dissipation increases by 107% to 1.374 meV. The fourth hybrid QCA half-adder design includes two partially reversible majority gates (M1 and M2) and two irreversible majority gates (M3 and M4), and it does not include any fully reversible majority gates, which can explain the significant increase in energy dissipation in the fourth design.

### 4.4. Cost Calculation

The circuit cost encompasses several aspects, including the complexity of the design and manufacturing process and the operational cost associated with the delay time. The delay time, number of logic gates, and number of crossovers are essential metrics for measuring the circuit performance, design complexity, and fabrication difficulty of a QCA circuit.

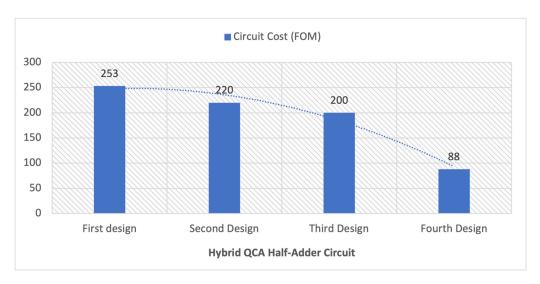

The cost function can be computed as a figure of merit (FOM) to evaluate the characteristics of QCA circuits [20,42]. Currently, there are two recognised cost functions for calculating the cost of QCA circuits. The first cost function is employed to calculate the cost of designs utilising three-input majority gates [20], while the second cost function is utilised to evaluate the cost of designs employing five-input majority gates [42]. Thus, the costs of hybrid half-adder circuits, which utilise three-input majority gates, can be calculated using the first cost function [20]. The cost function is shown in Equation (4).

$$Cost_{QCA} = (M^k + I + C^l) \times T^p, \quad k, l, p \ge 1$$

(4)

where M represents the number of three-input majority gates, I represents the number of inverters, C represents the number of crossovers, and T represents the delay time of the circuit measured in clock phases. In addition, the variables k, l, and p represent the powers assigned to the number of majority gates, number of crossovers, and delay time, respectively. Typically, we assign a weight of 1 to the number of inverters, because they have a limited impact on the complexity of QCA circuits.