# System Level Simulation of Quantum-Dot Cellular Automata Computer Circuits

Mohammed Alharbi

A thesis submitted in partial fulfilment of the requirements of Liverpool John Moores University for the degree of Doctor of Philosophy

December 2024

## **Table of Contents**

| TABL                                   | LE OF CONTENTS                                      | II       |

|----------------------------------------|-----------------------------------------------------|----------|

| LIST                                   | OF TABLES                                           | VII      |

| LIST                                   | OF FIGURES                                          | IX       |

| ABBR                                   | REVIATION                                           | XV       |

| ABST                                   | 'RACT                                               | XVII     |

| DECL                                   | LARATION                                            | XVIII    |

| DEDI                                   | CATION                                              | XIX      |

| ACKN                                   | NOWLEDGMENTS                                        | XX       |

| 1. II                                  | NTRODUCTION                                         | 1        |

| 1.1.                                   | Introduction to Nanocomputing                       | 1        |

| 1.2.                                   | Introduction to Quantum-Dot Cellular Automata (QCA) | 2        |

| 1.3.                                   | QCA Background                                      | 4        |

| <b>1.4.</b><br>1.4.1<br>1.4.2<br>1.4.3 | 2. QCA Inverter                                     | 9<br>10  |

| 1.5.                                   | QCA Clocking Algorithms                             | 12       |

| <b>1.6.</b><br>1.6.1<br>1.6.2          | 2. Multilayer Wire Crossing                         | 17<br>19 |

| 1.7.                                   | Energy Dissipation Analysis of QCA Cells            |          |

| 1.8.                                   | QCA Circuits Cost Calculation                       |          |

| 1.9.                                   | Experimental Implementations for QCA                |          |

| 1.9.1                                  |                                                     |          |

| 1.9.2                                  |                                                     |          |

| 1.9.3                                  | 3. Molecular FCN                                    |          |

| 2. 1 | REVERSIBLE DESIGN METHODOLOGY                                         | 29 |

|------|-----------------------------------------------------------------------|----|

| 2.1. | Reversible computing                                                  | 29 |

| 2.2. | Reversible QCA circuits background                                    | 30 |

| 2.3. | Reversible, time-synchronised design method                           | 32 |

| 2.3. |                                                                       |    |

| 2.3. |                                                                       |    |

| 2.3. | -                                                                     |    |

| 2.3  |                                                                       |    |

| 2.3. |                                                                       |    |

| 2.3  |                                                                       |    |

| 2.3. | -                                                                     |    |

| 3. ] | REVERSIBLE QCA COMBINATIONAL DIGITAL CIRCUITS                         | 42 |

| 3.1. | Designing reversible and time-synchronised QCA combinational circuits | 42 |

| 3.1. | .1. Reversible QCA XOR design                                         | 42 |

| 3.1. | .2. Reversible QCA XNOR design                                        | 44 |

| 3.1. |                                                                       |    |

| 3.1. |                                                                       |    |

| 3.1. | ······································                                |    |

| 3.1. |                                                                       |    |

| 3.1. |                                                                       |    |

| 3.1. | .8. Reversible QCA 2:4 decoder design                                 | 54 |

| 3.2. | Reliability simulation                                                |    |

| 3.2. | · · · · · · · · · · · · · · · · · · ·                                 |    |

| 3.2. |                                                                       |    |

| 3.2. |                                                                       |    |

| 3.2. |                                                                       |    |

| 3.2. |                                                                       |    |

| 3.2. |                                                                       |    |

| 3.2. |                                                                       |    |

| 3.2. |                                                                       |    |

| 3.2. | .9. Summary of the reliability simulation of the circuits             | 63 |

| 3.3. | Area cost and delay time evaluation                                   | 64 |

| 3.4. | Energy dissipation simulation                                         | 64 |

| 3.5. | Conclusion                                                            | 65 |

| 3.6. | Contribution                                                          | 66 |

| 4. ] | REVERSIBLE QCA SEQUENTIAL FLIP-FLOP CIRCUITS                          | 68 |

| 4.1. | Designing sequential QCA flip-flop circuits                           |    |

| 4.1. |                                                                       |    |

|      | 4.1.1.1. Irreversible QCA SR flip-flop design                         |    |

|      |                                                                       |    |

|                                                                                                                                                                                                                                                          | I.1.1.2. Reversible QCA SR flip-flop design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 4.1.                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

|                                                                                                                                                                                                                                                          | I.1.2.1. Irreversible QCA D flip-flop design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72               |

| 4                                                                                                                                                                                                                                                        | I.1.2.2. Reversible QCA D flip-flop design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |

| 4.1.                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

| 4                                                                                                                                                                                                                                                        | I.1.3.1. Irreversible QCA JK flip-flop design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |

| 4                                                                                                                                                                                                                                                        | I.1.3.2. Reversible QCA JK flip-flop design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

| 4.1.                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

|                                                                                                                                                                                                                                                          | I.1.4.1. Irreversible QCA T flip-flop design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  |

| 4                                                                                                                                                                                                                                                        | I.1.4.2. Reversible QCA T flip-flop design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |

| 4.2.                                                                                                                                                                                                                                                     | Reliability simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |

| 4.2.                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

|                                                                                                                                                                                                                                                          | I.2.1.1. Irreversible QCA SR flop-flop simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |

|                                                                                                                                                                                                                                                          | I.2.1.2. Reversible QCA SR flop-flop simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

| 4.2.                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

|                                                                                                                                                                                                                                                          | I.2.2.1. Irreversible QCA D flop-flop simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |

|                                                                                                                                                                                                                                                          | A.2.2.2. Reversible QCA D flop-flop simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |

| 4.2.                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

|                                                                                                                                                                                                                                                          | .2.3.1. Irreversible QCA JK flop-flop simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |

|                                                                                                                                                                                                                                                          | .2.3.2. Reversible QCA JK flop-flop simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |

| 4.2.                                                                                                                                                                                                                                                     | ······································                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |

|                                                                                                                                                                                                                                                          | .2.4.1. Irreversible QCA T flop-flop simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

|                                                                                                                                                                                                                                                          | A.2.4.2. Reversible QCA T flop-flop simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |

| 4.2.                                                                                                                                                                                                                                                     | 5. Summary of the reliability for the simulation of the flip-flops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |

| 4.0                                                                                                                                                                                                                                                      | Energy dissipation analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

| 4.3.                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

| 4.3.<br>4.4.                                                                                                                                                                                                                                             | Occupied area and delay time calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |

|                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97               |

| 4.4.                                                                                                                                                                                                                                                     | Occupied area and delay time calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97               |

| 4.4.<br>4.5.                                                                                                                                                                                                                                             | Occupied area and delay time calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 97<br>100<br>101 |

| 4.4.<br>4.5.<br>4.6.<br>4.7.                                                                                                                                                                                                                             | Occupied area and delay time calculation<br>Cost calculation<br>Conclusion<br>Contribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |

| 4.4.<br>4.5.<br>4.6.<br>4.7.                                                                                                                                                                                                                             | Occupied area and delay time calculation<br>Cost calculation<br>Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |

| 4.4.<br>4.5.<br>4.6.<br>4.7.                                                                                                                                                                                                                             | Occupied area and delay time calculation<br>Cost calculation<br>Conclusion<br>Contribution<br>ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS.<br>Reversible QCA 8:1 multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

| <ol> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>4.7.</li> <li>5. A</li> </ol>                                                                                                                                                                         | Occupied area and delay time calculation<br>Cost calculation<br>Conclusion<br>Contribution<br>ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS.<br>Reversible QCA 8:1 multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

| <ul> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>4.7.</li> <li>5. <i>A</i></li> <li>5.1.</li> <li>5.1.</li> </ul>                                                                                                                                      | Occupied area and delay time calculation<br>Cost calculation<br>Conclusion<br>Contribution<br>ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS.<br>Reversible QCA 8:1 multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

| <ul> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>4.7.</li> <li>5. 4</li> <li>5.1.</li> <li>5.1.</li> <li>5.5.</li> </ul>                                                                                                                               | Occupied area and delay time calculation<br>Cost calculation<br>Conclusion<br>Contribution<br><b>Contribution</b><br><b>ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS</b><br><b>Reversible QCA 8:1 multiplexer</b><br>1. Designing reversible QCA 8:1 multiplexer<br>5.1.1.1. Reversible QCA 2:1 multiplexer design                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |

| 4.4.<br>4.5.<br>4.6.<br>4.7.<br>5. A<br>5.1.<br>5.1.                                                                                                                                                                                                     | Occupied area and delay time calculation         Cost calculation         Conclusion         Contribution         ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS         Reversible QCA 8:1 multiplexer         1.       Designing reversible QCA 8:1 multiplexer         5.1.1.1.       Reversible QCA 4:1 multiplexer design         5.1.1.3.       Reversible QCA 8:1 multiplexer design                                                                                                                                                                                                                                                                                                                                                                |                  |

| 4.4.<br>4.5.<br>4.6.<br>4.7.<br>5. 4<br>5.1.<br>5.1.<br>5.1.                                                                                                                                                                                             | Occupied area and delay time calculation         Cost calculation         Conclusion         Contribution         ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS         Reversible QCA 8:1 multiplexer         1.       Designing reversible QCA 8:1 multiplexer         5.1.1.1       Reversible QCA 2:1 multiplexer design         5.1.1.2       Reversible QCA 4:1 multiplexer design         5.1.1.3       Reversible QCA 8:1 multiplexer design         2.       Energy dissipation simulation results                                                                                                                                                                                                                                               |                  |

| <ul> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>4.7.</li> <li>5. 4</li> <li>5.1.</li> <li>5.1.</li> <li>5.1.</li> <li>5.1.</li> </ul>                                                                                                                 | Occupied area and delay time calculation         Cost calculation         Conclusion         Contribution         ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS         Reversible QCA 8:1 multiplexer         1.       Designing reversible QCA 8:1 multiplexer         5.1.1.1.       Reversible QCA 2:1 multiplexer design         5.1.1.2.       Reversible QCA 4:1 multiplexer design         5.1.1.3.       Reversible QCA 8:1 multiplexer design         2.       Energy dissipation simulation results         3.       Cost calculation                                                                                                                                                                                                          |                  |

| <ul> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>4.7.</li> <li>5. 4</li> <li>5.1.</li> <li>5.1.</li> <li>5.1.</li> <li>5.1.</li> <li>5.1.</li> <li>5.1.</li> </ul>                                                                                     | Occupied area and delay time calculation         Cost calculation         Conclusion         Contribution         ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS         Reversible QCA 8:1 multiplexer         1.       Designing reversible QCA 8:1 multiplexer         5.1.1.1       Reversible QCA 2:1 multiplexer design         5.1.1.2       Reversible QCA 4:1 multiplexer design         5.1.1.3       Reversible QCA 8:1 multiplexer design         2.       Energy dissipation simulation results         3.       Cost calculation         4.       Discussion                                                                                                                                                                                 |                  |

| <ul> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>4.7.</li> <li>5. 4</li> <li>5.1.</li> <li>5.1.</li> <li>5.1.</li> <li>5.1.</li> </ul>                                                                                                                 | Occupied area and delay time calculation         Cost calculation         Conclusion         Contribution         ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS         Reversible QCA 8:1 multiplexer         1.       Designing reversible QCA 8:1 multiplexer         5.1.1.1       Reversible QCA 2:1 multiplexer design         5.1.1.2       Reversible QCA 4:1 multiplexer design         5.1.1.3       Reversible QCA 8:1 multiplexer design         5.1.1.3       Reversible QCA 8:1 multiplexer design         5.1.2       Reversible QCA 4:1 multiplexer design         5.1.3       Reversible QCA 8:1 multiplexer design         5.1.4       Bergy dissipation simulation results         3       Cost calculation         4       Discussion |                  |

| <ul> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> <li>4.7.</li> <li>5. 4</li> <li>5.1.</li> <li>5.2.</li> </ul> | Occupied area and delay time calculation         Cost calculation         Conclusion         Contribution         ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS.         Reversible QCA 8:1 multiplexer         1.       Designing reversible QCA 8:1 multiplexer         5.1.1.1.       Reversible QCA 2:1 multiplexer design         5.1.1.2.       Reversible QCA 4:1 multiplexer design         5.1.1.3.       Reversible QCA 8:1 multiplexer design         2.       Energy dissipation simulation results         3.       Cost calculation.         4.       Discussion         5.       Summary for designing a reversible QCA 8:1 multiplexer         Reversible QCA ALU                                                                         |                  |

| 4.4.<br>4.5.<br>4.6.<br>4.7.<br>5.<br>5.1.<br>5.1.<br>5.1.<br>5.1.<br>5.1.<br>5.1.<br>5.1                                                                                                                                                                | Occupied area and delay time calculation         Cost calculation         Conclusion         Contribution         ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS         Reversible QCA 8:1 multiplexer         1.       Designing reversible QCA 8:1 multiplexer design         5.1.1.1.       Reversible QCA 4:1 multiplexer design         6.1.1.2.       Reversible QCA 4:1 multiplexer design         6.1.1.3.       Reversible QCA 8:1 multiplexer design         2.       Energy dissipation simulation results         3.       Cost calculation.         4.       Discussion         5.       Summary for designing a reversible QCA 8:1 multiplexer         1.       Designing reversible QCA ALU                                                |                  |

| 4.4.<br>4.5.<br>4.6.<br>4.7.<br>5.1.<br>5.1.<br>5.1.<br>5.1.<br>5.1.<br>5.1.<br>5.1.<br>5                                                                                                                                                                | Occupied area and delay time calculation         Cost calculation         Conclusion         Contribution         ADVANCED REVERSIBLE QCA COMPUTING CIRCUITS.         Reversible QCA 8:1 multiplexer         1.       Designing reversible QCA 8:1 multiplexer         5.1.1.1.       Reversible QCA 2:1 multiplexer design         5.1.1.2.       Reversible QCA 4:1 multiplexer design         5.1.1.3.       Reversible QCA 8:1 multiplexer design         2.       Energy dissipation simulation results         3.       Cost calculation.         4.       Discussion         5.       Summary for designing a reversible QCA 8:1 multiplexer         Reversible QCA ALU                                                                         |                  |

| 5.2.2.                | Energy dissipation simulation results        | 135 |

|-----------------------|----------------------------------------------|-----|

| 5.2.3.                | Cost Calculation                             |     |

| 5.2.4.                | Discussion                                   |     |

| 5.2.5.                | Summary for designing a reversible QCA ALU   | 140 |

| 5.3. C                | onclusion                                    | 141 |

| 5.4. C                | ontribution                                  | 142 |

| 6. PAI                | RTIALLY REVERSIBLE DESIGN METHOD             | 148 |

| 6.1. D                | esigning partially reversible QCA half-adder | 149 |

| 6.2. Si               | mulation results and discussion              | 151 |

| 6.2.1.                | Performance evaluation                       | 151 |

| 6.2.2.                | Energy dissipation simulation                | 152 |

| 6.2.3.                | Cost Calculation                             | 154 |

| 6.3. C                | onclusion                                    | 155 |

| 6.4. C                | ontribution                                  | 155 |

|                       |                                              |     |

| 7. HY                 | BRID DESIGN METHOD                           | 157 |

|                       | esigning hybrid QCA half-adders              |     |

| 7.1.1.                | The HA-1 design                              |     |

| 7.1.2.                | The HA-2 design                              |     |

| 7.1.3.<br>7.1.4.      | The HA-3 design<br>The HA-4 design           |     |

| 7.0 0                 | -                                            |     |

| <b>7.2.</b> Si 7.2.1. | Performance evaluation                       |     |

| 7.2.1.                |                                              |     |

| 7.2.1                 | 8                                            |     |

| 7.2.1                 | -                                            |     |

|                       | .4. Simulated waveforms of HA-4 design       |     |

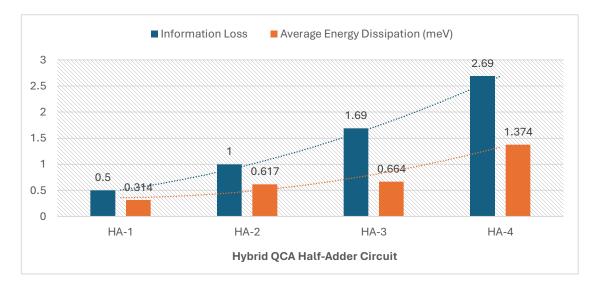

| 7.2.2.                | Information dissipation calculation          |     |

| 7.2.2                 | •                                            |     |

| 7.2.2                 | ·                                            |     |

| 7.2.2                 | •                                            |     |

| 7.2.2                 | •                                            |     |

| 7.2.2                 | •                                            |     |

| 7.2.3.                | Energy dissipation simulation                |     |

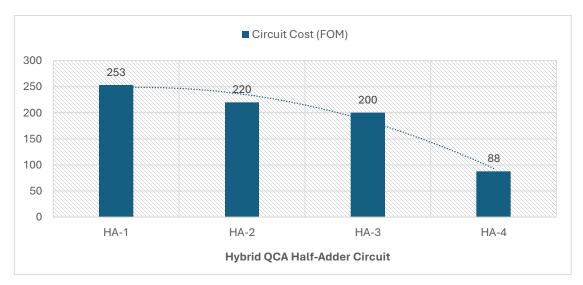

| 7.2.4.                | Cost calculation                             |     |

| 7.3. Di               | iscussion                                    | 176 |

| 7.4. C                | onclusion                                    | 177 |

| 76 0                  |                                              | 470 |

| 7.5. C                | ontribution                                  |     |

| 8.        | CONCLUSION AND FUTURE WORK            |     |

|-----------|---------------------------------------|-----|

| 8.1.      | Conclusion                            | 180 |

| 8.2.      | Future work                           | 183 |

| <b>RE</b> | FERENCES                              |     |

| AP        | PENDICES                              |     |

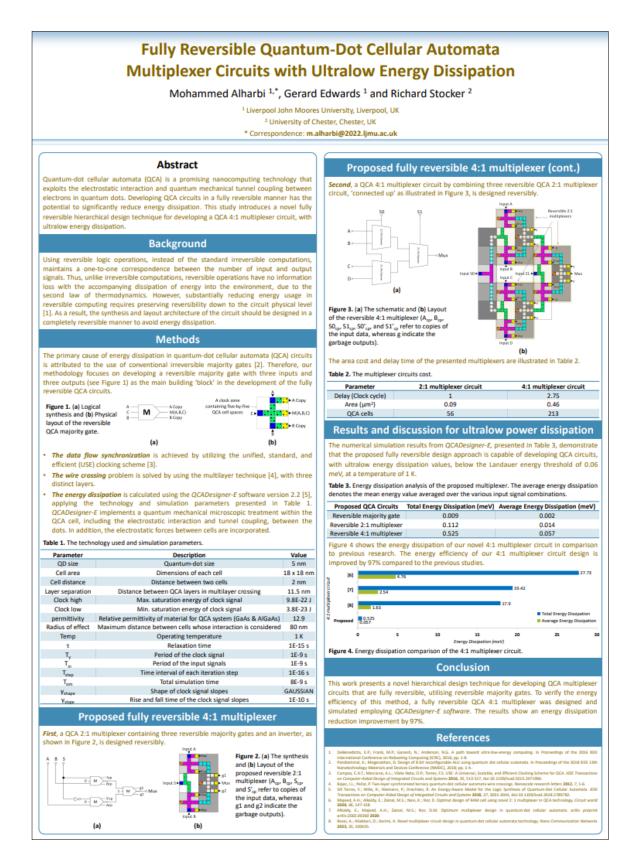

| Арр       | endix I: Published Article Papers     | 200 |

| Арр       | endix II: Published Book Chapters     | 205 |

| Арр       | endix III: Published Conference Paper | 206 |

| Арр       | endix IV: Presented Conference Poster | 207 |

## **List of Tables**

| Table 1.1 QCA versus other quantum computing technologies                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.1 The adopted technological parameters.    38                                                                                                                                  |

| Table 2.2 The employed simulation parameters                                                                                                                                           |

| Table 3.1 Truth table for XOR gate shown in Figure 3.1.                                                                                                                                |

| Table 3.2 Truth table for XNOR gate shown in Figure 3.2.       45                                                                                                                      |

| Table 3.3 Truth table for half-adder circuit shown in Figure 3.3.                                                                                                                      |

| Table 3.4 Truth table for half-subtractor circuit shown in Figure 3.4.                                                                                                                 |

| Table 3.5 Truth table for 2:1 multiplexer circuit shown in Figure 3.5.                                                                                                                 |

| Table 3.6 Truth table for 1:2 demultiplexer circuit shown in Figure 3.6.                                                                                                               |

| Table 3.7 Truth table for comparator circuit shown in Figure 3.7                                                                                                                       |

| Table 3.8 Truth table for 2:4 decoder circuit shown in Figure 3.8.                                                                                                                     |

| Table 3.9 Area cost and delay time for the proposed reversible and synchronous QCA designs64                                                                                           |

| Table 3.10 Energy dissipation values for the proposed reversible and synchronous QCA designs65                                                                                         |

| Table 4.1 Truth table for irreversible SR flip-flop circuit shown in Figure 4.1.                                                                                                       |

| Table 4.2 Truth table for reversible SR flip-flop circuit shown in Figure 4.2 with copies of the two inputs passed to the two additional outputs                                       |

| Table 4.3 Truth table for irreversible D flip-flop circuit shown in Figure 4.3.         73                                                                                             |

| Table 4.4 Truth table for reversible D flip-flop circuit shown in Figure 4.4.         74                                                                                               |

| Table 4.5 Truth table for irreversible JK flip-flop circuit shown in Figure 4.5.         77                                                                                            |

| Table 4.6 Truth table for reversible JK flip-flop circuit shown in Figure 4.6.         77                                                                                              |

| Table 4.7 Truth table for irreversible T flip-flop circuit shown in Figure 4.7                                                                                                         |

| Table 4.8 Truth table for reversible T flip-flop circuit shown in Figure 4.8                                                                                                           |

| Table 4.9 Average and total energy dissipation comparison                                                                                                                              |

| Table 4.10 Flip-flops area and delay time calculation                                                                                                                                  |

| Table 4.11 Flip-flops cost calculation101                                                                                                                                              |

| Table 5.1 Truth table for proposed 2:1 multiplexer circuit shown in Figure 5.1.                                                                                                        |

| Table 5.2 Truth table for proposed 4:1 multiplexer circuit shown in Figure 5.2.                                                                                                        |

| Table 5.3 Truth table for proposed 8:1 multiplexer circuit shown in Figure 5.3.                                                                                                        |

| Table 5.4 Energy dissipation analysis of the proposed multiplexer (The average energy dissipation refers to the mean energy value averaged over the various input signal combinations) |

| Table 5.5 QCA multiplexers cost                                                                                                                                                        |

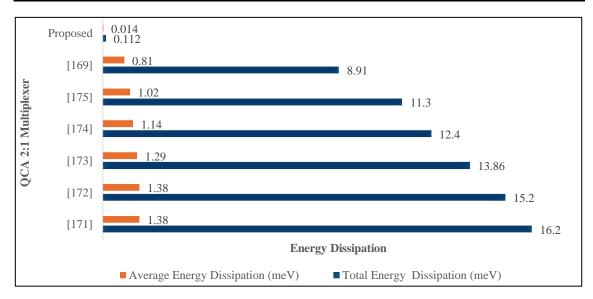

| Table 5.6 Energy dissipation comparison of the 2:1 multiplexer circuit                                                                                                                 |

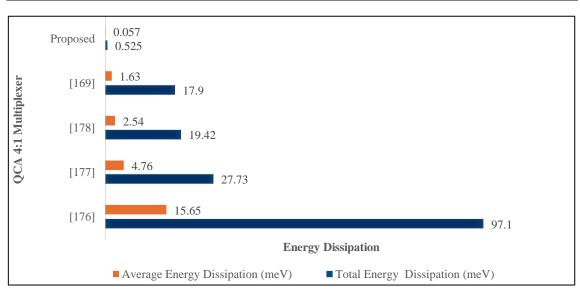

| Table 5.7 Energy dissipation comparison of the 4:1 multiplexer circuit                                                                                                 | 116       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

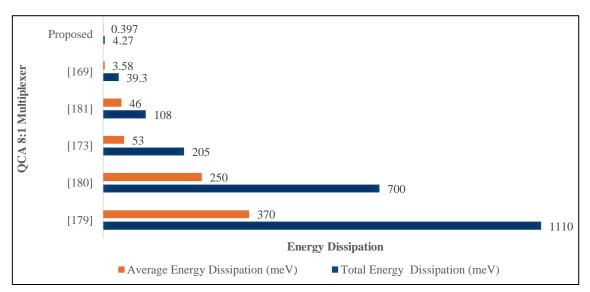

| Table 5.8 Energy dissipation comparison of the 8:1 multiplexer circuit                                                                                                 | 117       |

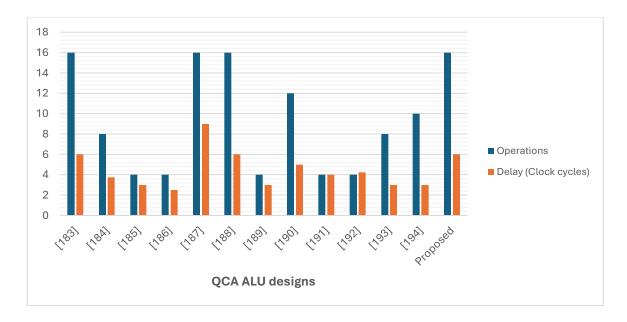

| Table 5.9 The operations of the proposed reversible QCA ALU.                                                                                                           | 120       |

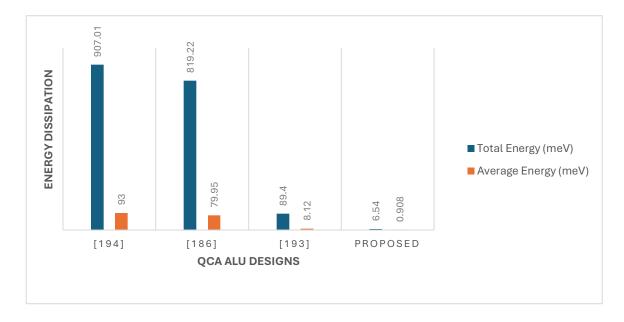

| Table 5.10 The energy dissipation analysis of the proposed reversible QCA ALU                                                                                          | 135       |

| Table 5.11 QCA ALU components cost.                                                                                                                                    |           |

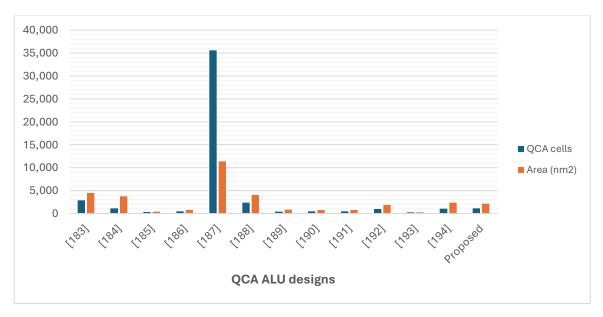

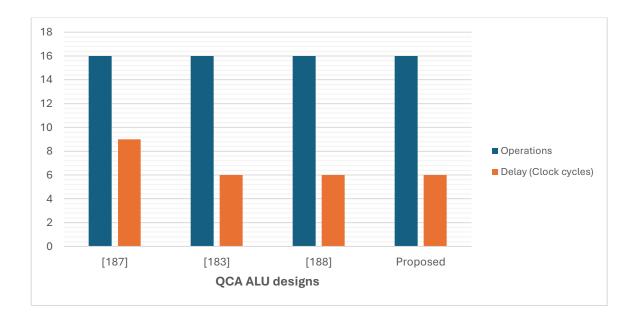

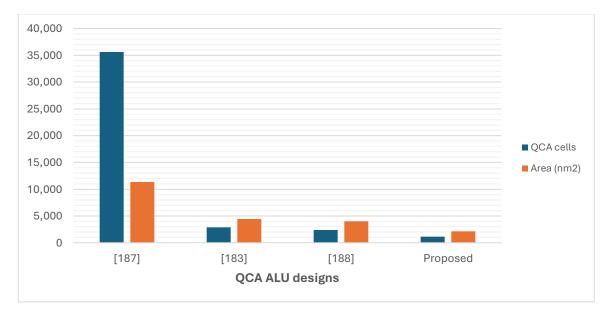

| Table 5.12 Comparison of performance and energy dissipation (Note that there are only references [181,188,189] that calculate the energy dissipation for the QCA ALU). | •         |

| Table 6.1 Energy Dissipation Values for Majority Gates with Different Reversibility Levels                                                                             | 153       |

| Table 6.2 Energy Dissipation Values for Half-Adder Circuits with Different Reversibility Lev                                                                           | vels. 154 |

| Table 6.3 Cost Values for Half-Adder Circuits with Different Reversibility Levels                                                                                      | 154       |

| Table 7.1 The number and types of majority gates utilised in the design of the four proposed       QCA half-adders.                                                    | •         |

| Table 7.2 Information dissipation calculation of HA-1                                                                                                                  |           |

| Table 7.3 Information dissipation calculation of HA-2                                                                                                                  | 170       |

| Table 7.4 Information dissipation calculation of HA-3                                                                                                                  | 171       |

| Table 7.5 Information dissipation calculation of HA-4                                                                                                                  | 172       |

| Table 7.6 Information dissipation for the hybrid QCA half-adder designs                                                                                                | 174       |

| Table 7.7 Energy dissipation values for the proposed hybrid QCA half-adder circuits.                                                                                   | 175       |

| Table 7.8 Cost values for the proposed hybrid QCA half-adder circuits                                                                                                  | 176       |

|                                                                                                                                                                        |           |

## **List of Figures**

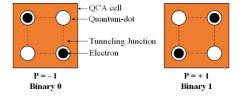

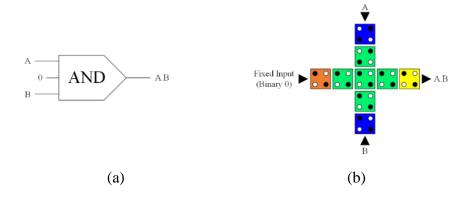

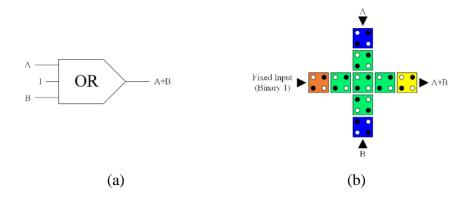

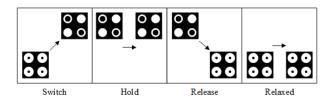

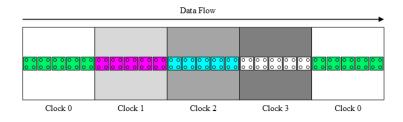

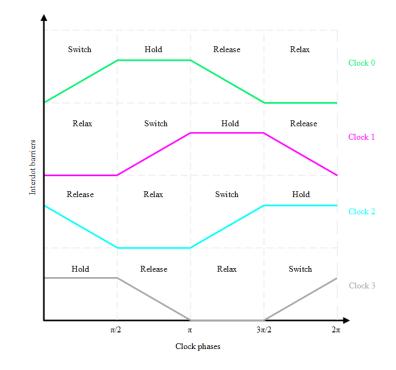

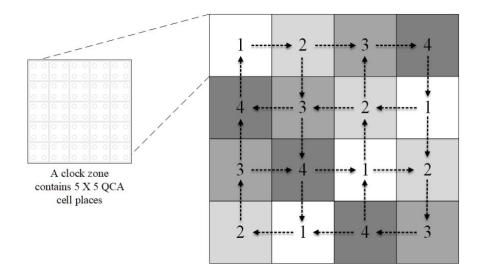

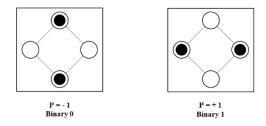

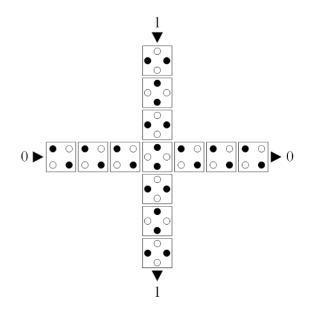

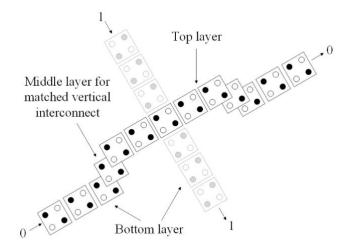

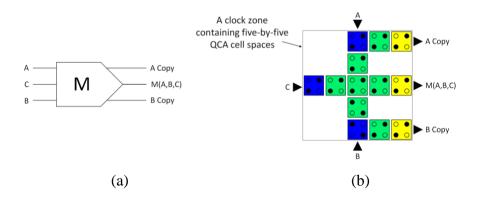

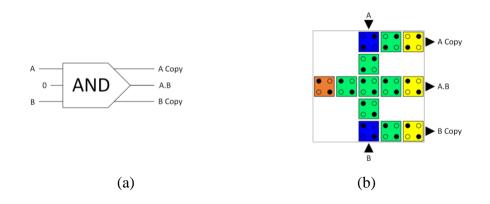

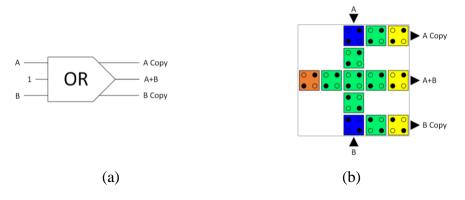

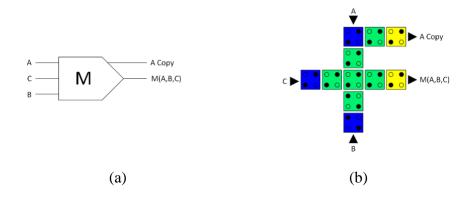

Figure 2.4 (a) The symbol of the reversible OR gate and (b) a USE clock zone containing the physical layout of the reversible QCA OR gate (the blue colour denotes the input cells, the yellow colour

| denotes the output cell, the green colour denotes the internal cells, and the orange cell with two electrons in the upper left and bottom right denotes the cell with a fixed value of '1')                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

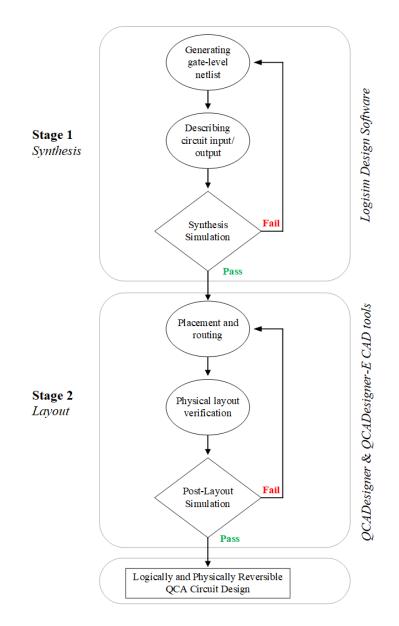

| Figure 2.5 The hierarchical structure of designing logically and physically reversible QCA circuits ( <i>Logisim</i> is used for the synthesis stage while <i>QCADesigner</i> and <i>QCADesigner</i> – <i>E</i> are employed for the layout stage)                                        |

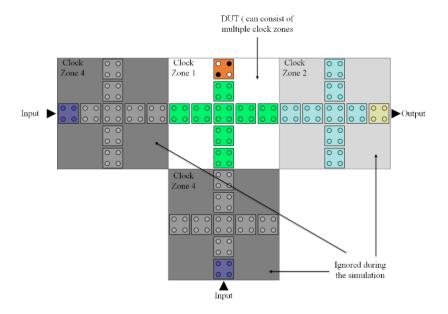

| Figure 2.6 Simulation testbench [96]41                                                                                                                                                                                                                                                    |

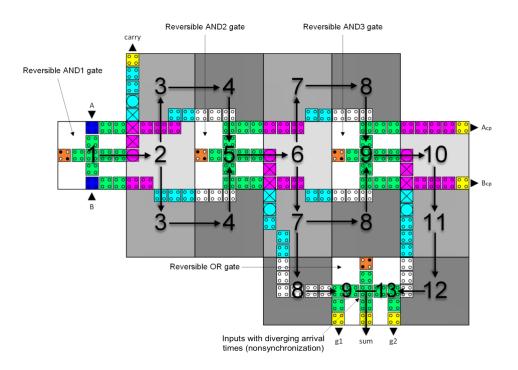

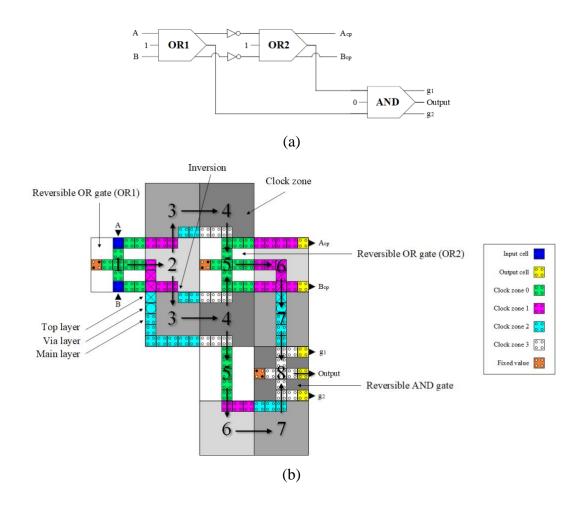

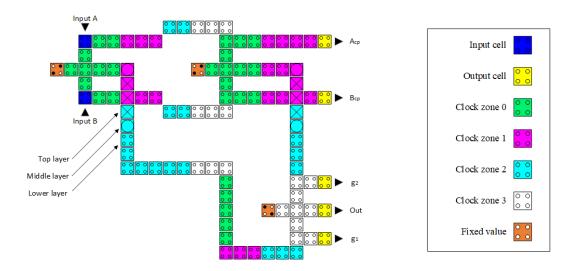

| Figure 3.1 (a) Logical synthesis and (b) physical QCA layout of the reversible time-synchronised QCA XOR (A <sub>cp</sub> and B <sub>cp</sub> indicate copies of the inputs, while g <sub>1</sub> and g <sub>2</sub> are so-called garbage outputs).                                      |

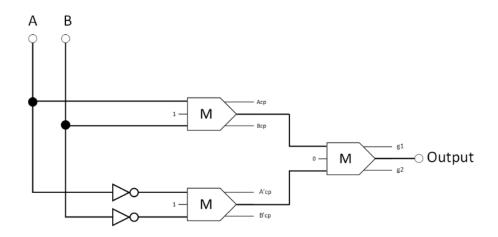

| Figure 3.2 (a) Logical synthesis and (b) physical QCA layout of the reversible time-synchronised QCA XNOR circuit (A <sub>cp</sub> and B <sub>cp</sub> indicate copies of the inputs, while g <sub>1</sub> and g <sub>2</sub> are so-called garbage outputs)                              |

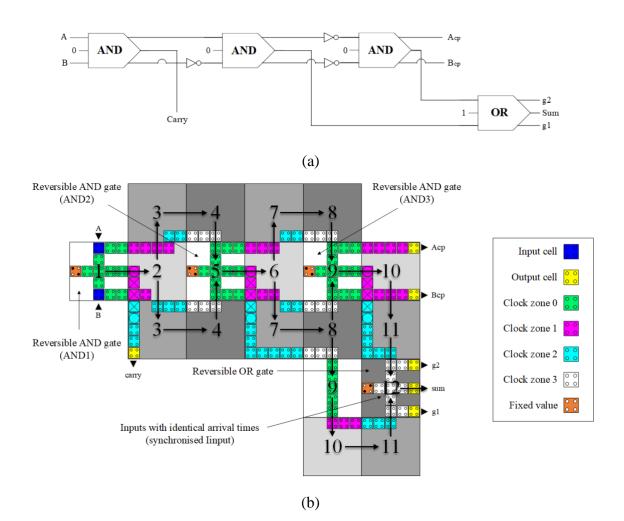

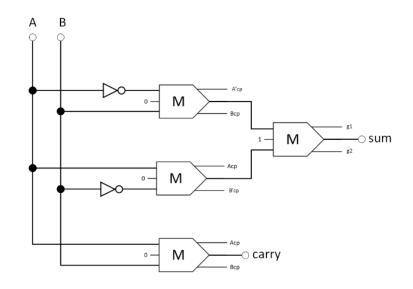

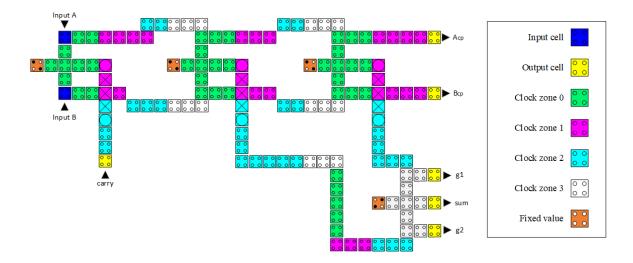

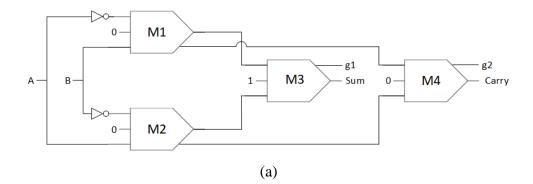

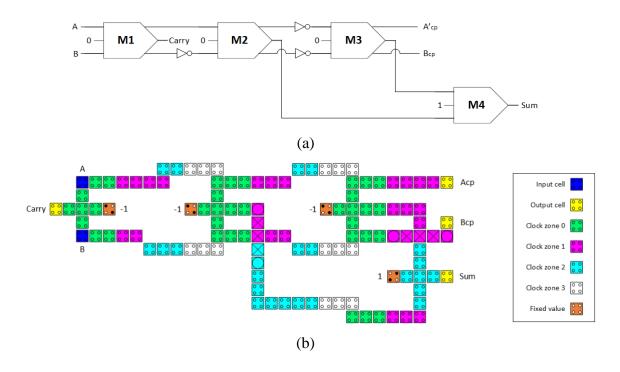

| Figure 3.3 (a) Logical synthesis and (b) physical QCA layout of the reversible time-synchronised QCA half-adder circuit (A <sub>cp</sub> and B <sub>cp</sub> indicate copies of the inputs, while g <sub>1</sub> and g <sub>2</sub> are so-called garbage outputs)                        |

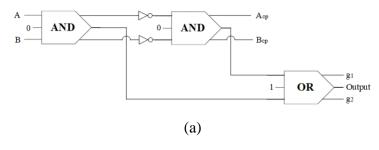

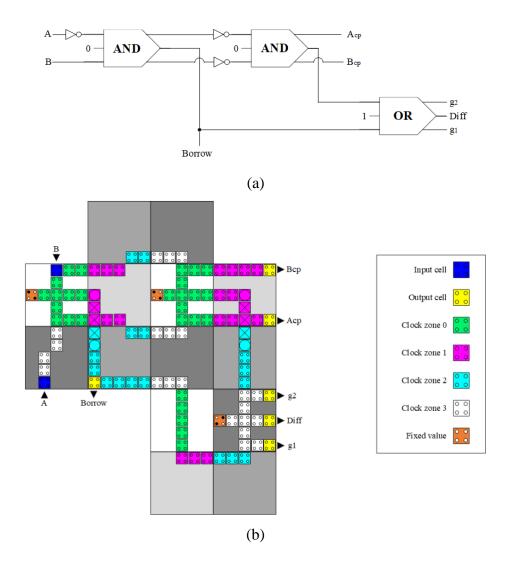

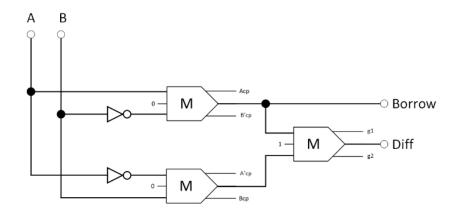

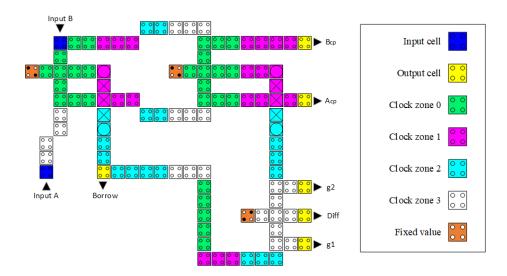

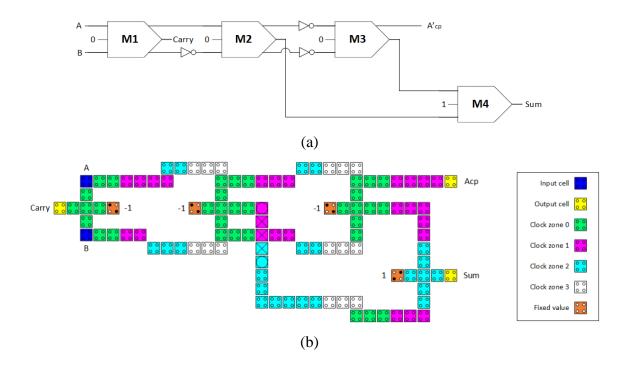

| Figure 3.4 (a) Logical synthesis and (b) physical QCA layout of the reversible time-synchronised QCA half-subtractor circuit (A <sub>cp</sub> and B <sub>cp</sub> indicate copies of the inputs, while g <sub>1</sub> and g <sub>2</sub> are so-called garbage outputs)                   |

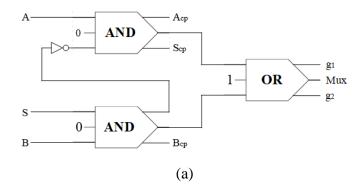

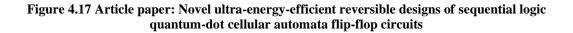

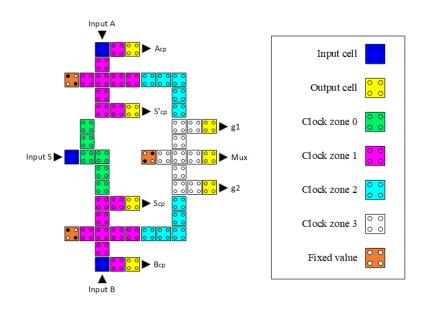

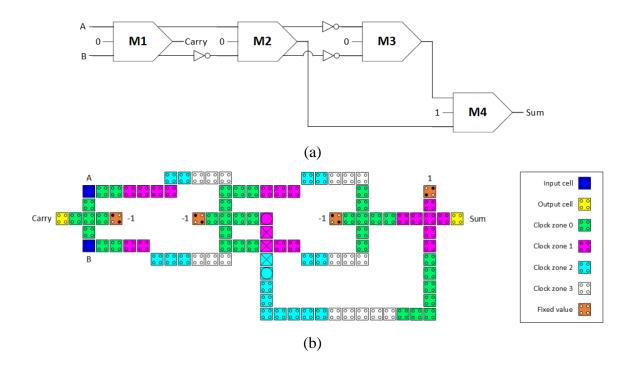

| Figure 3.5 (a) Logical synthesis and (b) physical QCA layout of the reversible time-synchronised QCA 2:1 multiplexer circuit (A <sub>cp</sub> , B <sub>cp</sub> and S <sub>cp</sub> indicate copies of the inputs, while g <sub>1</sub> and g <sub>2</sub> are so-called garbage outputs) |

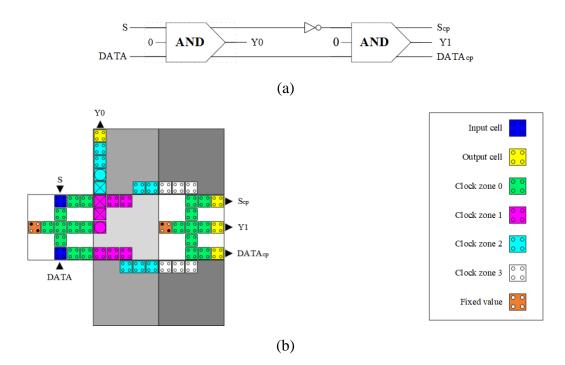

| Figure 3.6 (a) Logical synthesis and (b) physical QCA layout of the reversible time-synchronised QCA 1:2 demultiplexer circuit (S <sub>cp</sub> and DATA <sub>cp</sub> indicate copies of the inputs)                                                                                     |

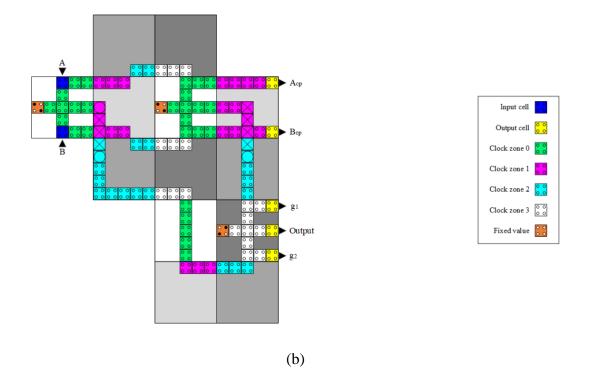

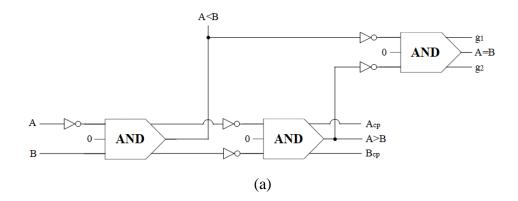

| Figure 3.7 (a) Logical synthesis and (b) physical QCA layout of the reversible time-synchronised QCA comparator circuit (A <sub>cp</sub> and B <sub>cp</sub> indicate copies of the inputs, while g <sub>1</sub> and g <sub>2</sub> are so-called garbage outputs)                        |

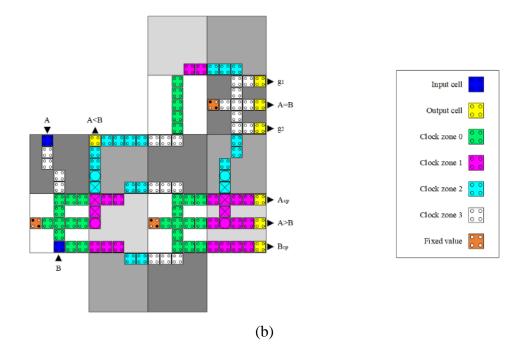

| Figure 3.8 (a) Logical synthesis and (b) physical QCA layout of the reversible time-synchronised QCA 2:4 decoder (A <sub>cp</sub> and B <sub>cp</sub> indicate copies of the inputs)54                                                                                                    |

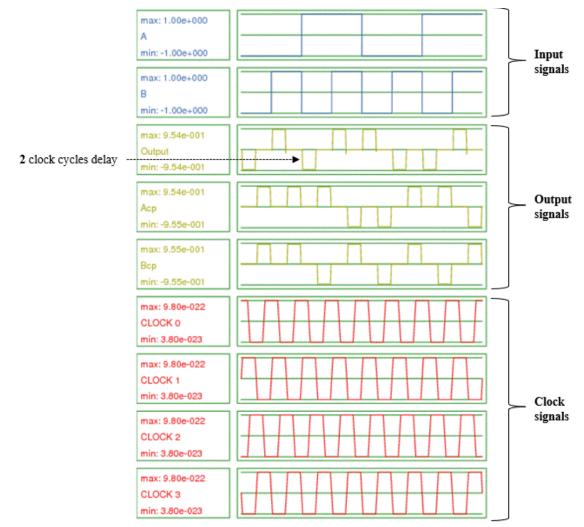

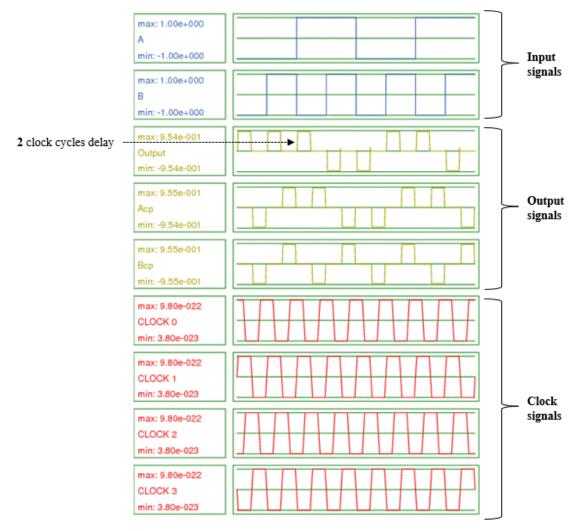

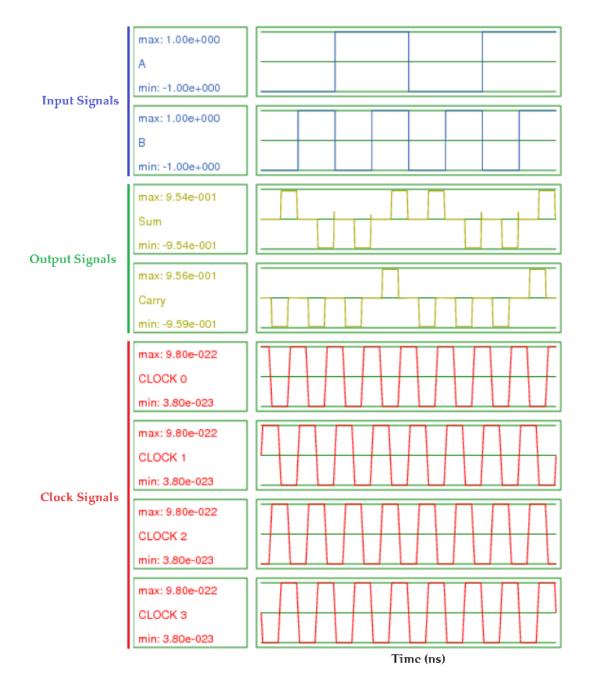

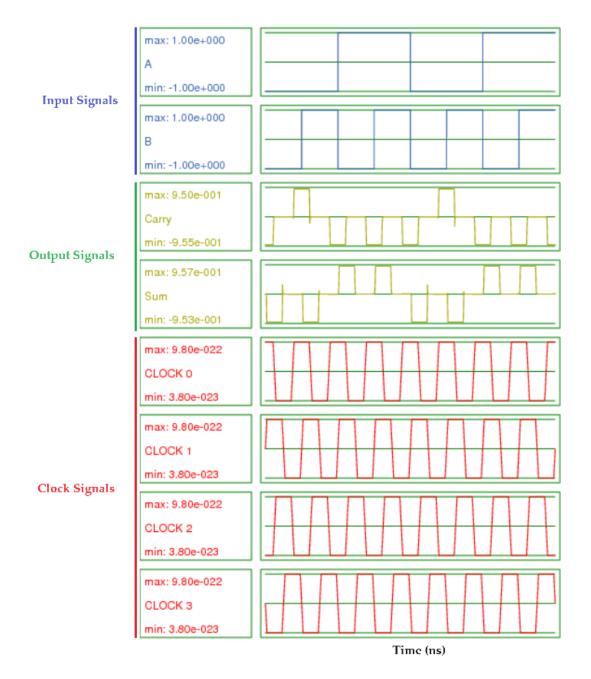

| Figure 3.9 Simulation waveforms of the proposed reversible time synchronised XOR design56                                                                                                                                                                                                 |

| Figure 3.10 Simulation waveforms of the proposed reversible time synchronised XNOR design57                                                                                                                                                                                               |

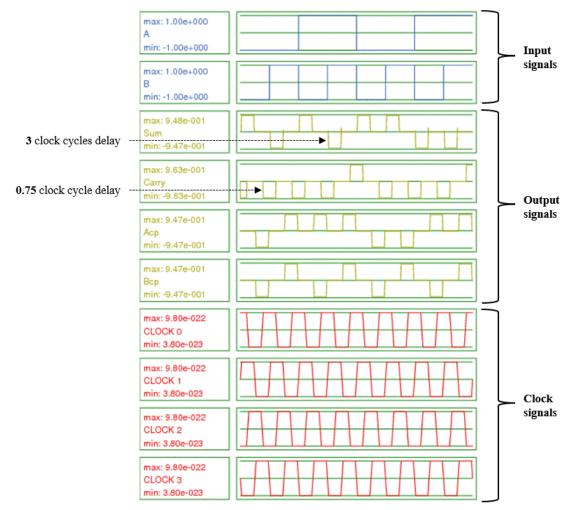

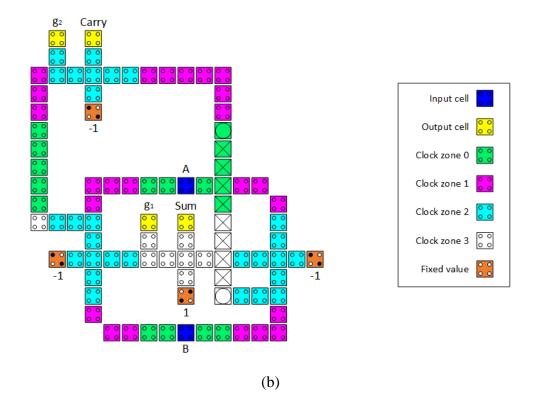

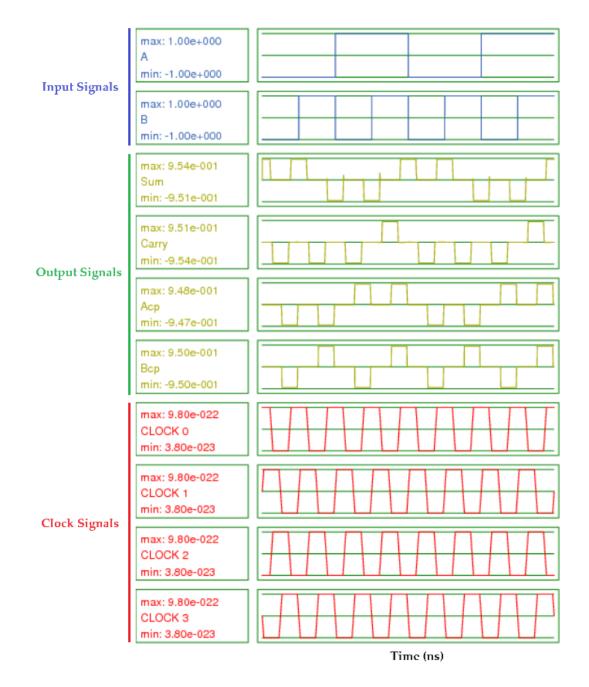

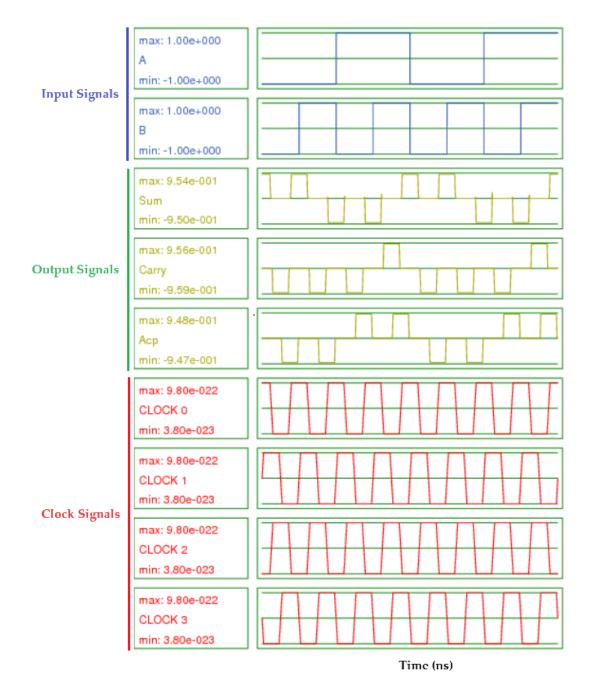

| Figure 3.11 Simulation waveforms of the proposed reversible time synchronised half-adder design.                                                                                                                                                                                          |

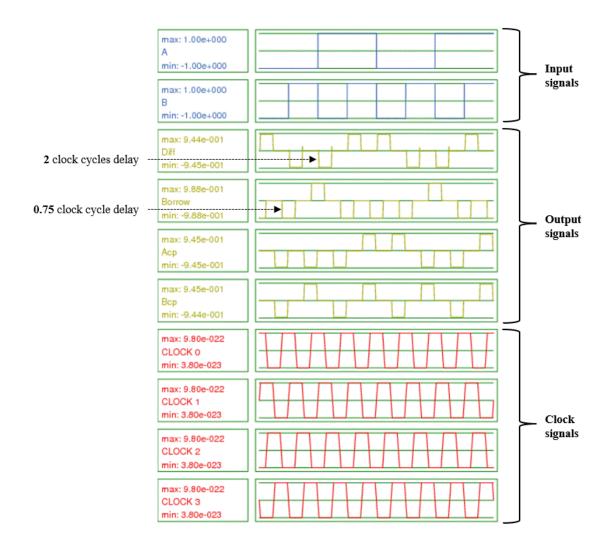

| Figure 3.12 Simulation waveforms of the proposed reversible time synchronised half-subtractor design                                                                                                                                                                                      |

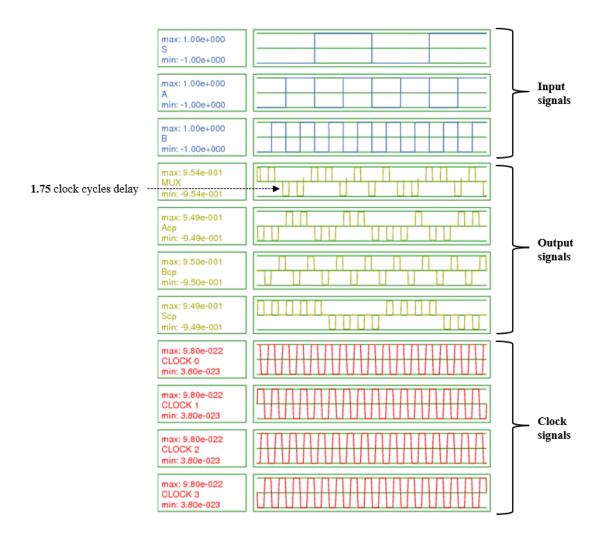

| Figure 3.13 Simulation waveforms of the proposed reversible time synchronised 2:1 multiplexer design                                                                                                                                                                                      |

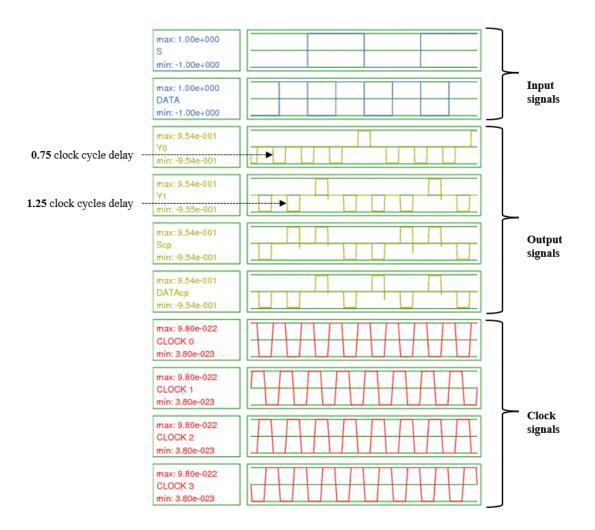

| Figure 3.14 Simulation waveforms of the proposed reversible time synchronised 1:2 demultiplexer design                                                                                                                                                                                    |

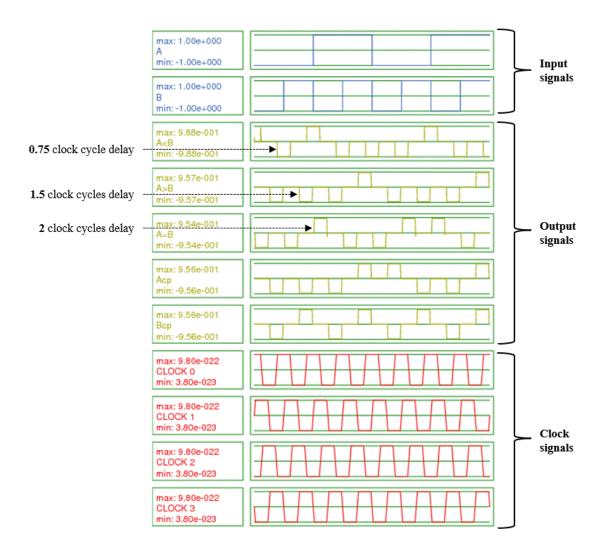

| Figure 3.15 Simulation waveforms of the proposed reversible time synchronised comparator design.<br>                                                                                                                                                                                      |

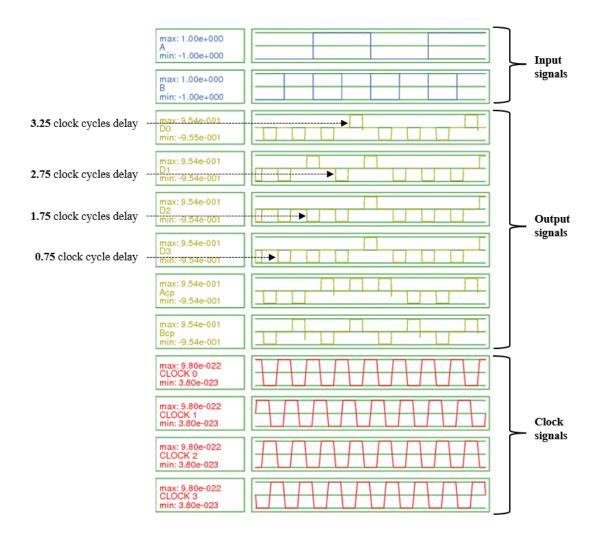

| Figure 3.16 Simulation waveforms of the proposed reversible time synchronised 2:4 decoder design.                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.17 Article paper: Design and simulation of reversible time-synchronized QCA combinational logic circuits with ultralow energy dissipation                                                                                                                                       |

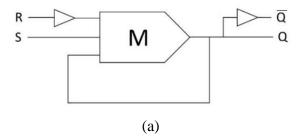

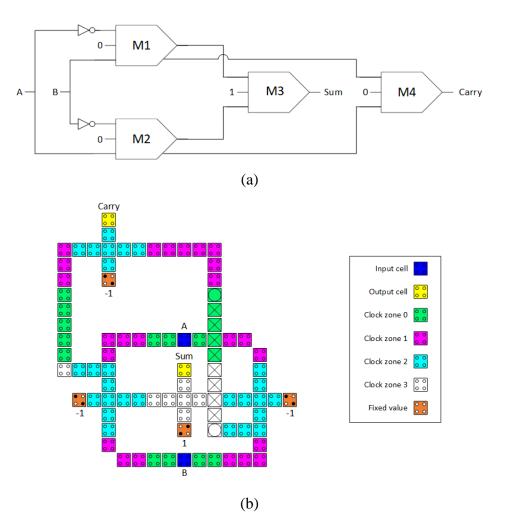

| Figure 4.1 (a) Logical synthesis design and (b) physical QCA layout of the proposed irreversible QCA SR flip-flop                                                                                                                                                                        |

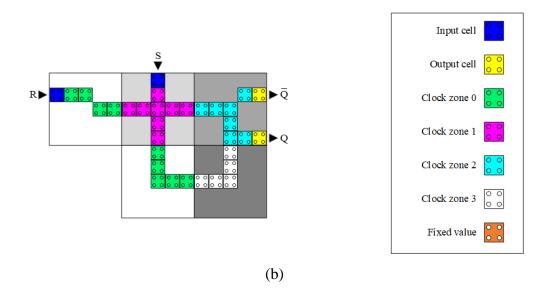

| Figure 4.2 (a) Logical synthesis design and (b) physical QCA layout of the proposed reversible QCA SR flip-flop (S <sub>cp</sub> and R <sub>cp</sub> indicate copies of the inputs)71                                                                                                    |

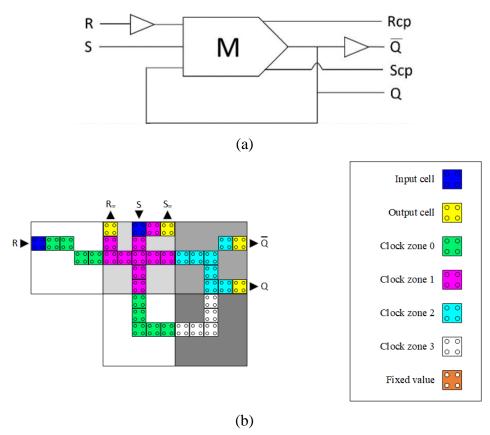

| Figure 4.3 (a) Logical synthesis design and (b) physical QCA layout of the proposed irreversible QCA D flip-flop                                                                                                                                                                         |

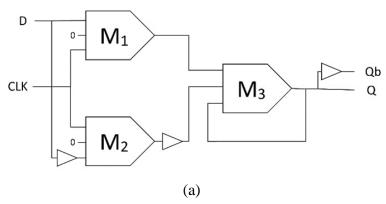

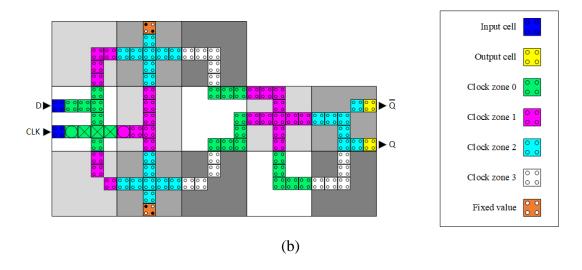

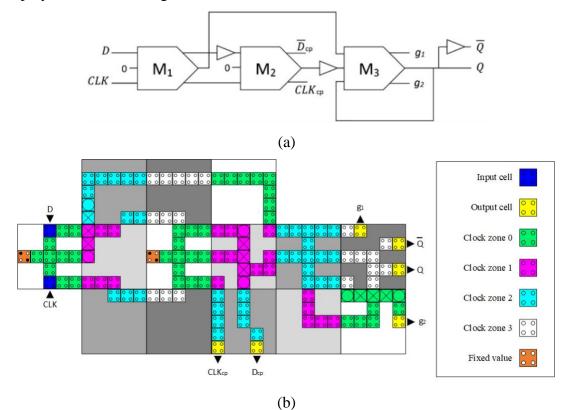

| Figure 4.4 (a) Logical synthesis design and (b) physical QCA layout of the proposed reversible QCA D flip-flop (Dcp and CLKcp indicate copies of the inputs, while g <sub>1</sub> and g <sub>2</sub> are so-called garbage outputs)                                                      |

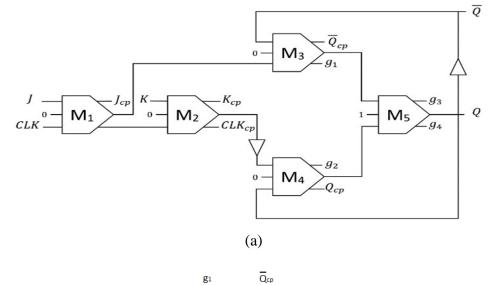

| Figure 4.5 (a) Logical synthesis design and (b) physical QCA layout of the proposed irreversible QCA JK flip-flop                                                                                                                                                                        |

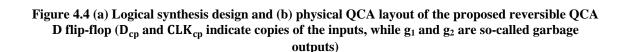

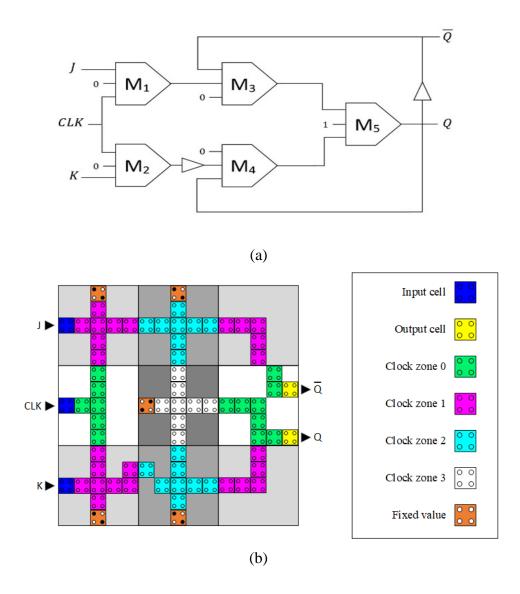

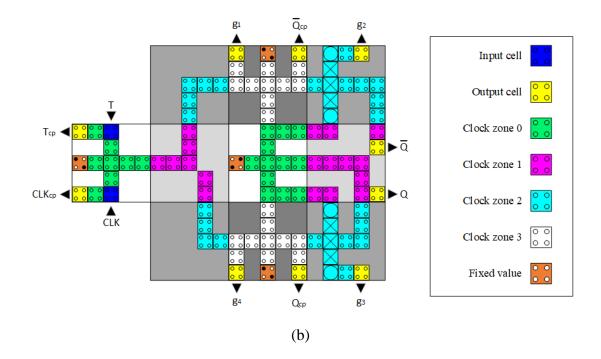

| Figure 4.6 (a) Logical synthesis design and (b) physical QCA layout of the proposed reversible QCA JK flip-flop (Jcp, Kcp, KLCcp, Qcp, and Qcp indicate copies of the inputs, while g <sub>1</sub> , g <sub>2</sub> , g <sub>3</sub> , and g <sub>4</sub> are so-called garbage outputs) |

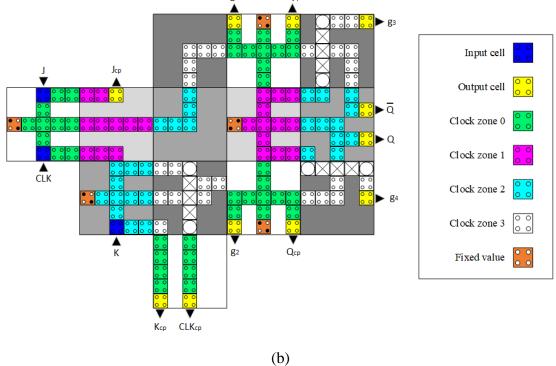

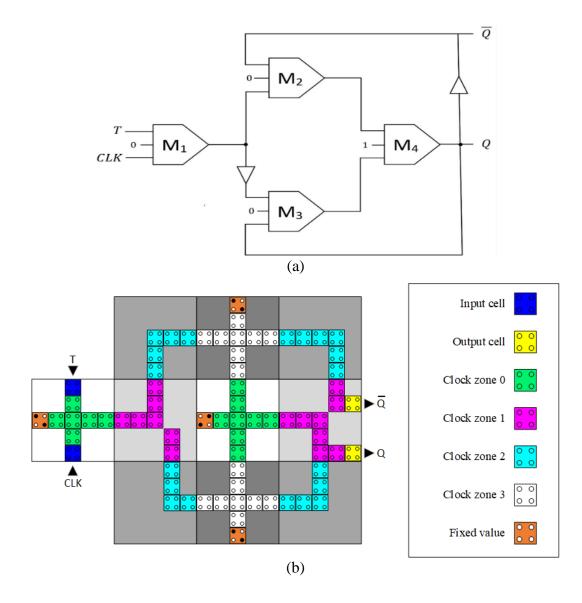

| Figure 4.7 (a) Logical synthesis design and (b) physical QCA layout of the proposed irreversible QCA T flip-flop                                                                                                                                                                         |

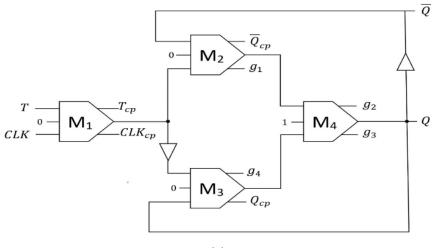

| Figure 4.8 (a) Logical synthesis design and (b) physical QCA layout of the proposed reversible QCA T flip-flop (Tcp, KLCcp, Qcp, and Qcp indicate copies of the inputs, while g1, g2, g3, and g4 are so-called garbage outputs)                                                          |

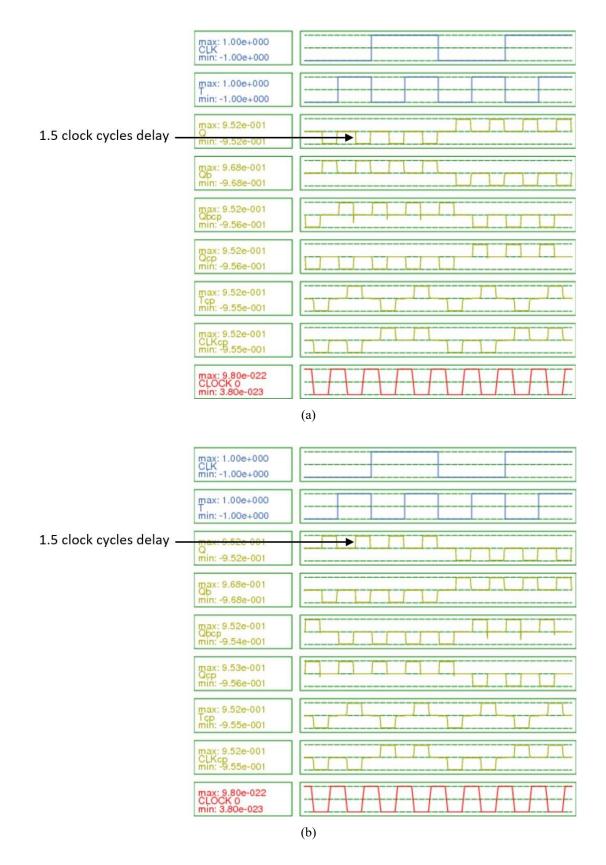

| Figure 4.9 Simulation waveforms of the proposed irreversible QCA SR flip-flop (a) for $Q_{(t-1)} = 0$ , (b) for $Q_{(t-1)} = 1$                                                                                                                                                          |

| Figure 4.10 Simulation waveforms of the proposed reversible QCA SR flip-flop (a) for $Q_{(t-1)} = 0$ , (b) for $Q_{(t-1)} = 1$                                                                                                                                                           |

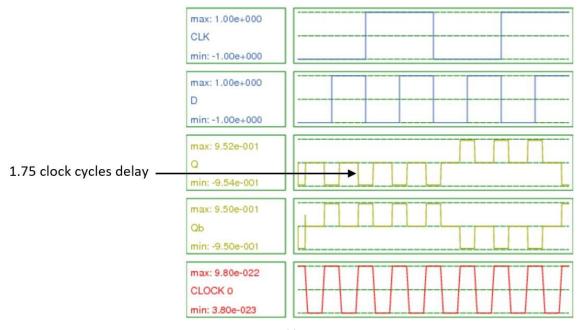

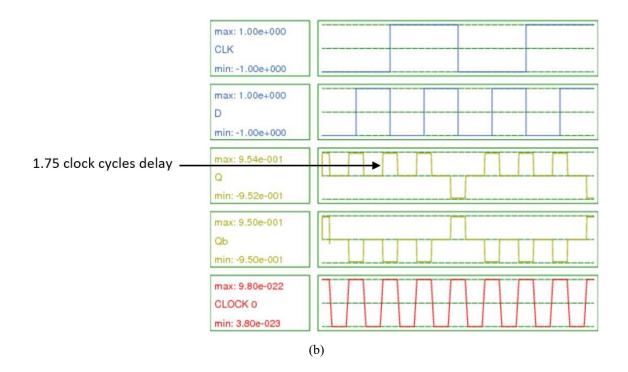

| Figure 4.11 Simulation waveforms of the proposed irreversible QCA D flip-flop (a) for $Q_{(t-1)} = 0$ , (b) for $Q_{(t-1)} = 1$                                                                                                                                                          |

| Figure 4.12 Simulation waveforms of the proposed reversible QCA D flip-flop (a) for $Q_{(t-1)} = 0$ , (b) for $Q_{(t-1)} = 1$                                                                                                                                                            |

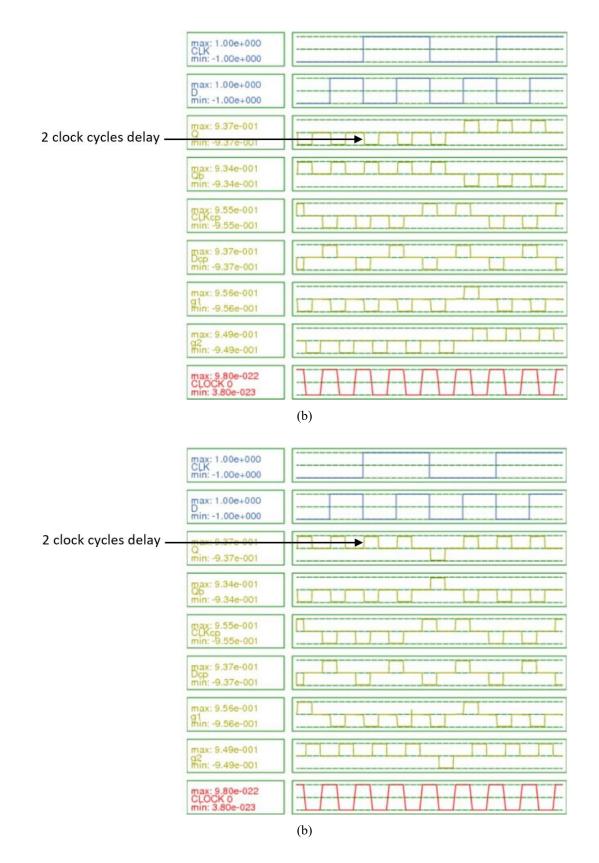

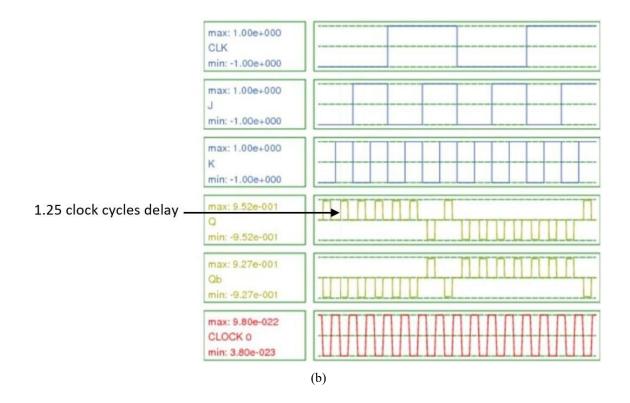

| Figure 4.13 Simulation waveforms of the proposed irreversible QCA JK flip-flop (a) for $Q_{(t-1)} = 0$ , (b) for $Q_{(t-1)} = 1$ 90                                                                                                                                                      |

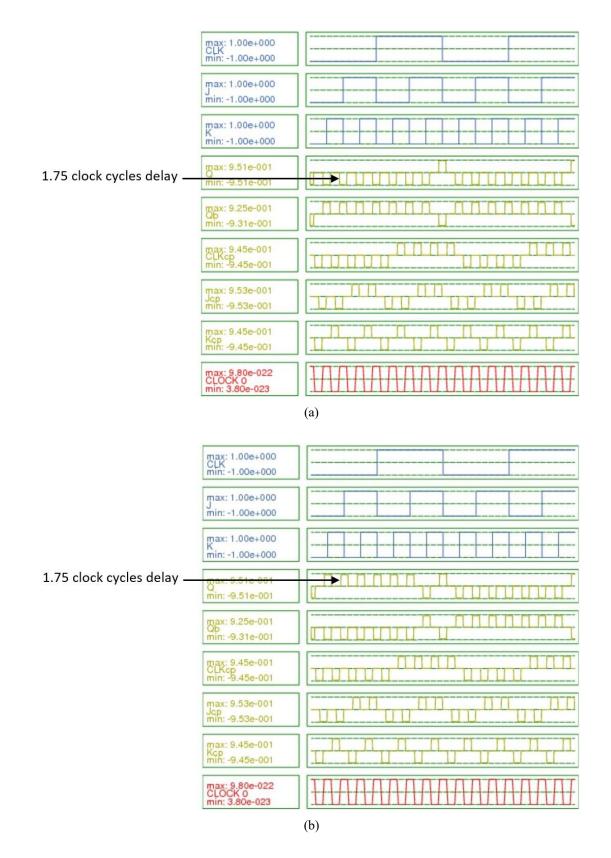

| Figure 4.14 Simulation waveforms of the proposed reversible QCA JK flip-flop (a) for $Q_{(t-1)} = 0$ , (b) for $Q_{(t-1)} = 1$                                                                                                                                                           |

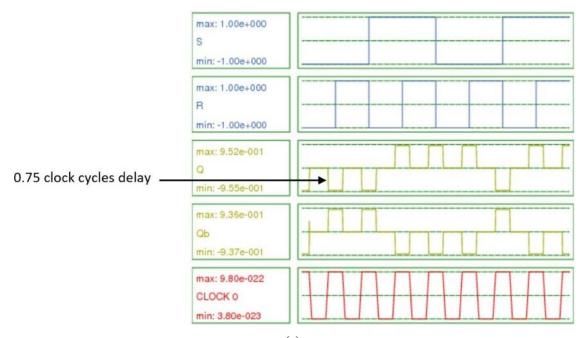

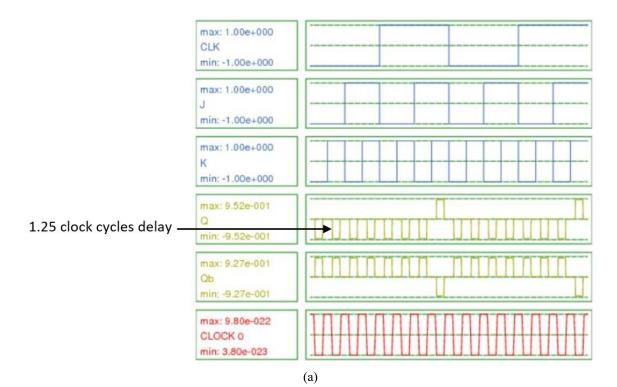

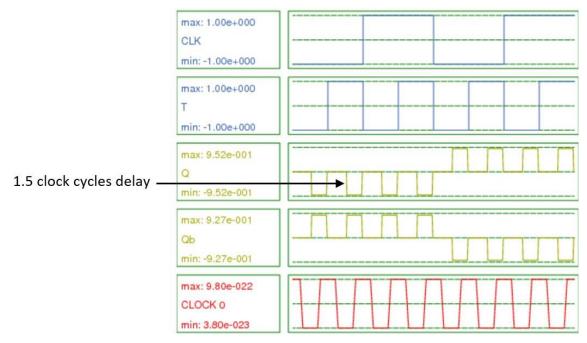

| Figure 4.15 Simulation waveforms of the proposed irreversible QCA T flip-flop (a) for $Q_{(t-1)} = 0$ , (b) for $Q_{(t-1)} = 1$                                                                                                                                                          |

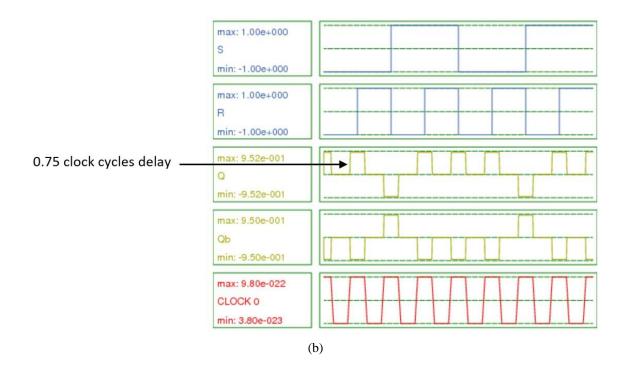

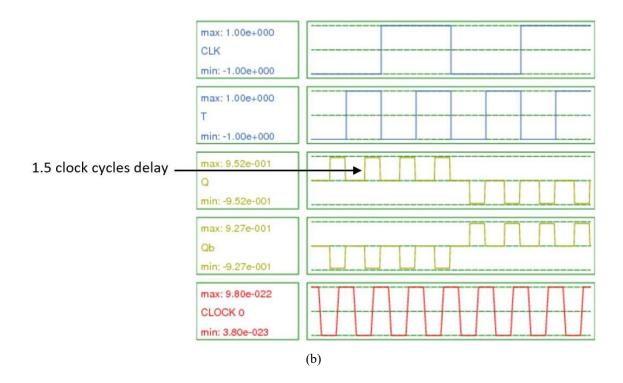

| Figure 4.16 Simulation waveforms of the proposed reversible QCA T flip-flop (a) for $Q_{(t-1)} = 0$ , (b) for $Q_{(t-1)} = 1$                                                                                                                                                            |

| Figure 4.17 Article paper: Novel ultra-energy-efficient reversible designs of sequential logic quantum-dot cellular automata flip-flop circuits104                                                                                                                                       |

| Figure 4.18 Book chapter: Novel ultra-energy-efficient reversible designs of sequential logic quantum-dot cellular automata flip-flop circuits105                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

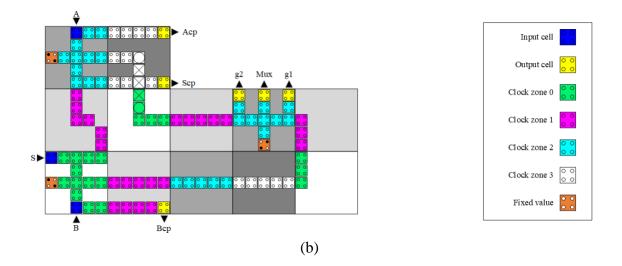

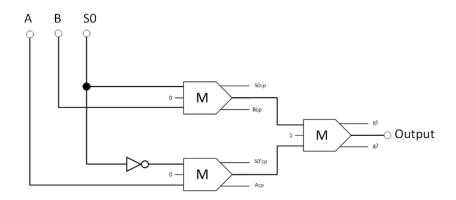

| Figure 5.1 (a) Logical synthesis design and (b) physical QCA layout of the proposed reversible QCA 2:1 multiplexer (Acp, Bcp, Scp, and Scp indicate copies of the inputs, while g1, and g2 are so-called garbage outputs)                                                                                  |

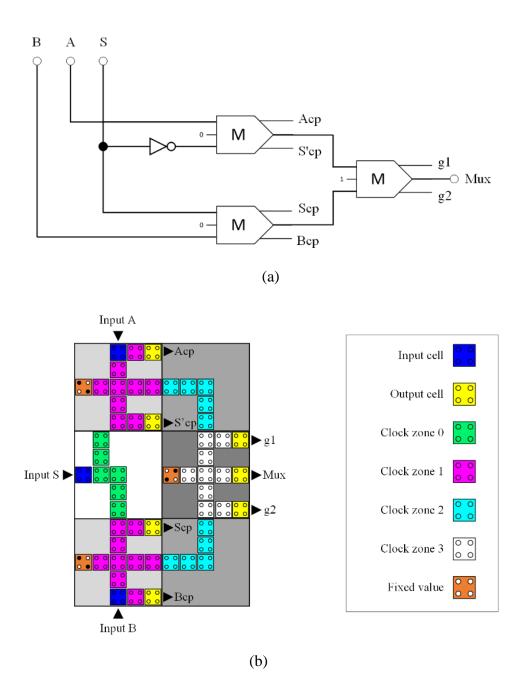

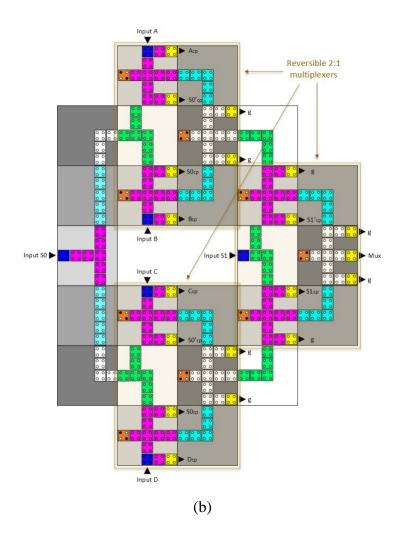

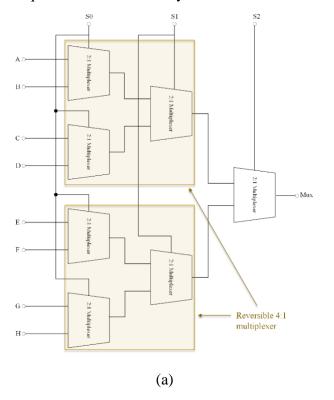

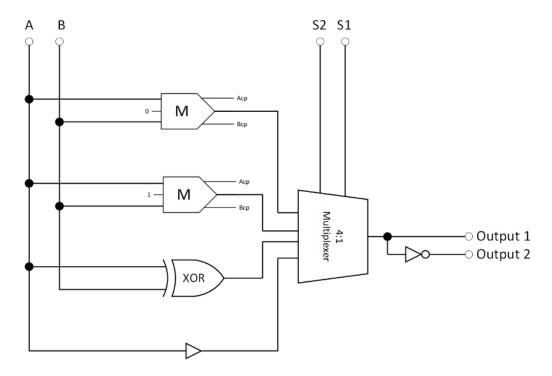

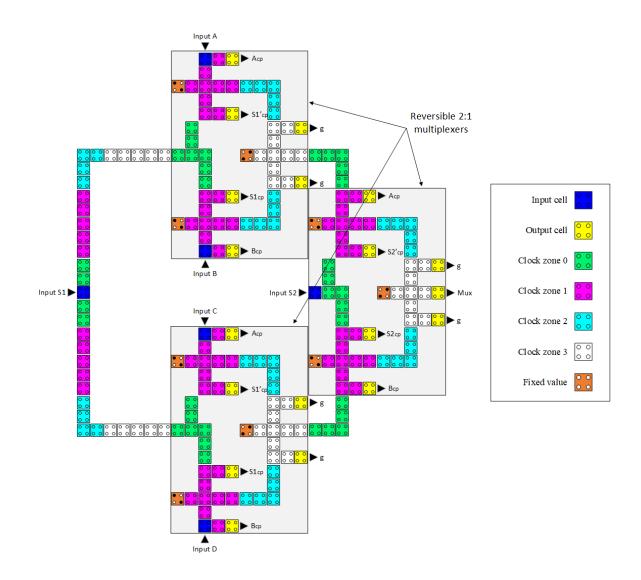

| Figure 5.2 (a) Logical synthesis design and (b) physical QCA layout of the proposed reversible QCA<br>4:1 multiplexer (Acp, Bcp, Ccp, Dcp, S0cp, S1cp, S0cp, and S1cp indicate copies of the inputs,<br>while g is so-called garbage output)                                                               |

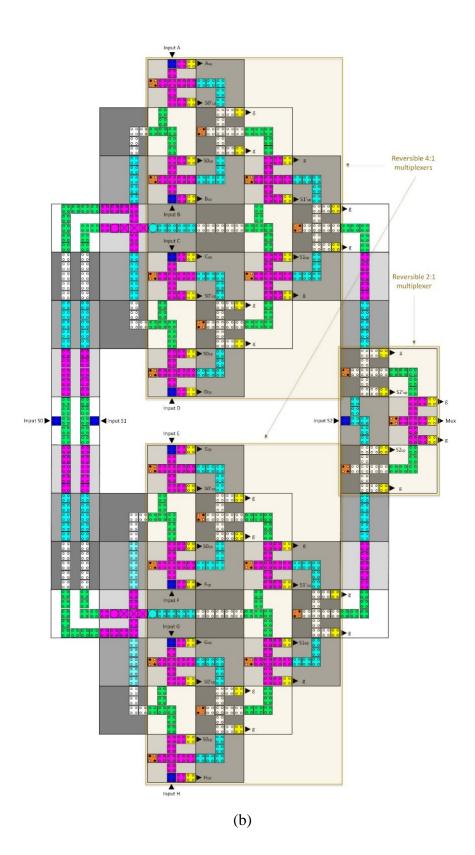

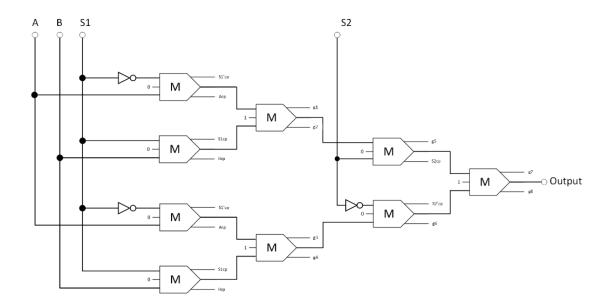

| <ul> <li>Figure 5.3 (a) Logical synthesis design and (b) physical QCA layout of the proposed reversible QCA</li> <li>8:1 multiplexer (Acp, Bcp, Ccp, Dcp, Ecp, Fcp, Gcp, Hcp, S0cp, S1cp, S2cp, S0cp, S1cp and</li> <li>S2cp indicate copies of the inputs, while g is so-called garbage output)</li></ul> |

| Figure 5.4 Energy dissipation comparison of the 2:1 multiplexer circuit.                                                                                                                                                                                                                                   |

| Figure 5.5 Energy dissipation comparison of the 4:1 multiplexer circuit                                                                                                                                                                                                                                    |

| Figure 5.6 Energy dissipation comparison of 8:1 multiplexer circuit                                                                                                                                                                                                                                        |

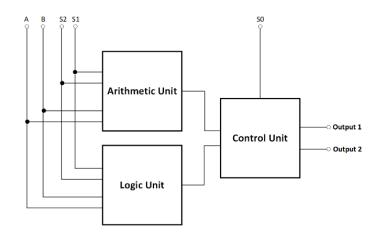

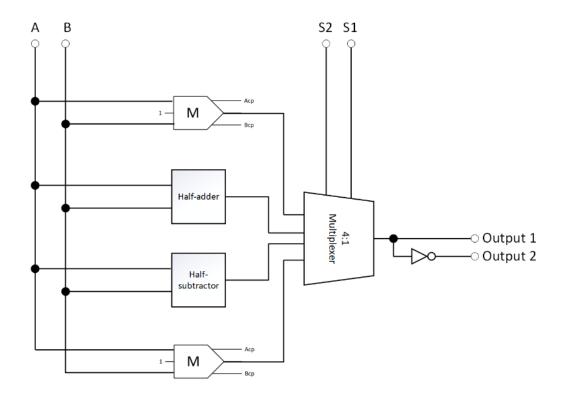

| Figure 5.7 The High-level block diagram of the proposed reversible QCA ALU119                                                                                                                                                                                                                              |

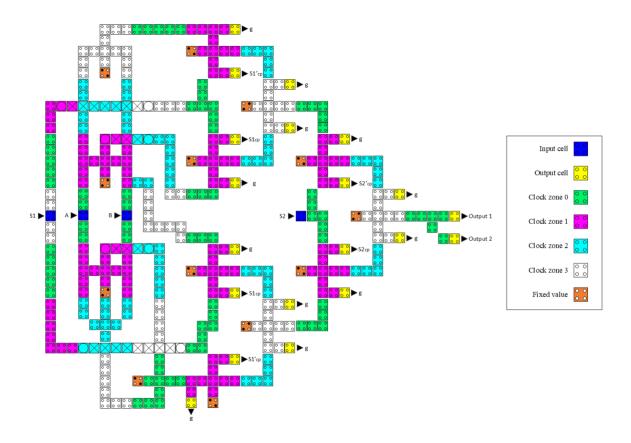

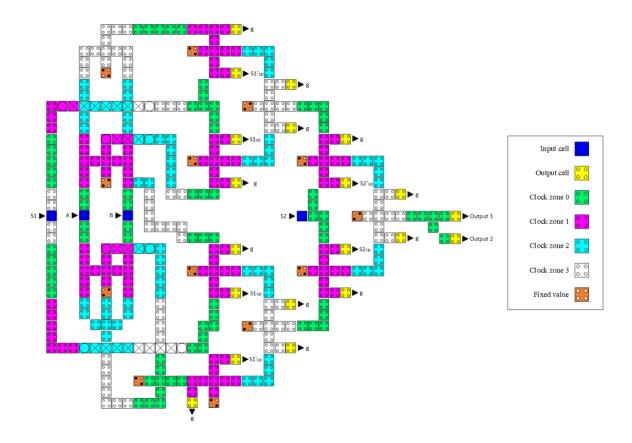

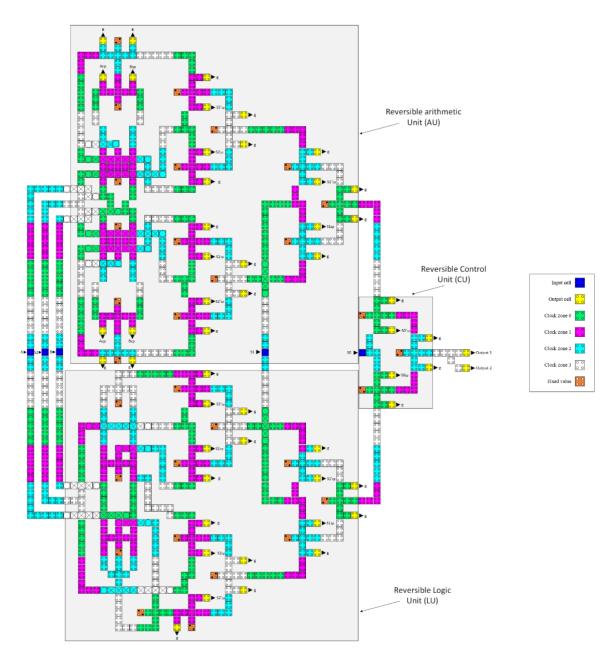

| Figure 5.8 The synthesis of the proposed reversible LU ( $A_{cp}$ and $B_{cp}$ refer to copies of the inputs). 121                                                                                                                                                                                         |