# BATTERY POWER ELECTRONICS INTEGRATION FOR MULTIPHASE EV DRIVETRAINS

MOHAMMAD UMAR KHAN

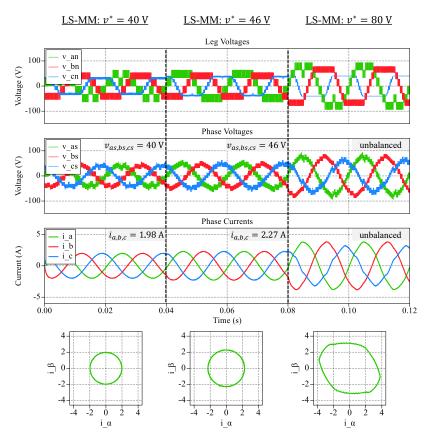

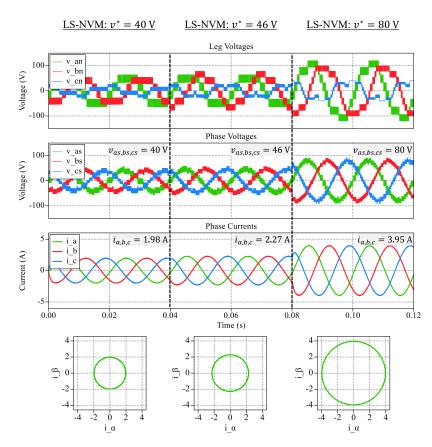

A thesis submitted in partial fulfilment of the requirements of Liverpool John Moores University for the degree of Doctor of Philosophy

April 2025

### Abstract

The battery electric vehicle (EV) is the most prominent alternative to traditional fossil fuel powered cars. Most modern EVs use three-phase machines for propulsion supplied by a standard IGBT-based two-level voltage source converter connected to a single large battery pack. The two-level inverter is well-known to suffer from several disadvantages. Moreover, recent research has indicated that most driving takes place at low speeds and the two-level converter has been shown to be inefficient in such operating conditions.

Multilevel converters have been suggested for use in EV drivetrains due to their inherent benefits compared to the two-level converters. Specifically, the cascaded H-bridge (CHB) converter retains well-known benefits of multilevel converter topologies while offering unique benefits such as simplicity, modularity and redundancy, low device count, fault tolerance, reliability, and its suitability for applications where independent dc sources are readily available. This makes it particularly suitable for traction applications, especially in EV drivetrains with a distributed battery pack. Likewise, multiphase electric machines are prime candidates for propulsion in electric transportation. They offer improved reliability, natural fault tolerance, lower current per phase, and high power density. They have also been shown to be used as current filters in on-board fast and slow charging of EV batteries with minimal hardware reconfiguration leading to weight, space, and cost savings.

Therefore, this thesis examines an alternative EV drivetrain based on the combination of these two technologies to form a multilevel multiphase drive where a battery-supplied CHB multilevel inverter is used in conjunction with a six-phase induction machine. Initially, simulation and experimental results are presented for the three-phase multilevel CHB inverter, with equal dc-source voltages, connected to an RL load under different carrierbased modulation methods and min-max based offset voltage injections for the whole modulation index range. Issue of unequal dc-source and switching device utilisation in levelshifted PWM is addressed through the appropriate rotation of the reference waveforms. The operation of the three-phase CHB inverter is also investigated under the inevitable imbalance of the dc-source voltages. Improvement in the performance of a previously suggested method is made leading to better harmonic performance of resulting currents as well as achieving enhancement in dc-source energy management. The operation of the drive is verified with the open-loop control of a three-phase induction machine. High performance control of the multilevel multiphase drive is presented with experimental validation in equal dc-source voltage conditions. The previously presented method for the operation of the CHB inverter in unequal dc-source voltage conditions is further extended to a six-phase multiphase drive with multiple neutral points. The operation of the multilevel multiphase drive is verified in simulation with high performance speed control in unequal dc-source voltage conditions.

The drive benefits from modularity, inherent fault tolerance, low THD at low switching frequencies, fast dynamic performance, and the possibility to be used in both propulsion and battery charging modes with minimal hardware reconfiguration. Additionally, smaller per phase current would require smaller sized cables as well as facilitating the use of lower rated semiconductor devices. Likewise, the suggested multilevel multiphase converter requires much smaller dc-link capacitors, which translates to savings in terms of cost and space.

### Acknowledgement

In the Name of Allah-the Most Compassionate, Most Merciful.

I would like to express sincere gratitude to my supervisor, Dr Obrad Dordevic, for his unwavering support and encouragement throughout the course of my doctoral studies, and most importantly for his friendship. He is a gem of a human being, always keen to offer help, educate, and engage in discussion. He sets an excellent example to follow. This would not have been possible without him.

Next, I am deeply grateful to my supervisor, Dr Martin Jones, for his continued support, supervision and guidance. I would also like to thank Prof Emil Levi for his words of encouragement and support over the years.

My heartfelt thanks to Dr Marko Slunjski and Dr Andrea Cervone for the brief but truly enjoyable time we spent together earlier on in my studies. I have also had the great opportunity to work with, learn from, and befriend Dr Angel González-Prieto and Mr Juan Carrillo Ríos during their short stay in Liverpool. I will fondly remember the time we spent engaged in truly enjoyable conversation.

Finally, I would like to thank my family, including my parents whose love and support has always been instrumental throughout my life. I would like to especially thank the pillar of my life, my beloved wife, Hina, for her continuous support and understanding, and my dear children, Noor and Ammaar, for bringing immense love and joy to my life.

## Contents

| Abstrac   | :t     |                                                      | i    |

|-----------|--------|------------------------------------------------------|------|

| Acknow    | vledg  | gement                                               | ii   |

| Content   | ts     |                                                      | iii  |

| List of A | Abbr   | eviations                                            | vi   |

| List of S | Symł   | pols                                                 | viii |

| Chapter   | r 1 In | troduction                                           | 1    |

| 1.1       | Р      | reliminary considerations                            | 1    |

| 1.2       | Р      | otential benefits of the proposed solution           | 2    |

| 1.3       | R      | esearch objectives and novelty                       | 4    |

| 1.4       | С      | Organisation of the report                           | 6    |

| Chapter   | r 2 Li | iterature survey                                     | 9    |

| 2.1       | Ir     | ntroduction                                          | 9    |

| 2.2       | N      | Iultilevel inverters                                 | 10   |

| 2.2       | 2.1    | Classic multilevel topologies                        | 12   |

| 2.2       | 2.2    | Cascaded H-bridge topology                           | 13   |

| 2.2       | 2.3    | Hybrid multilevel topologies                         | 14   |

| 2.3       | Ν      | Iultiphase machines and their control                | 16   |

| 2.3       | 3.1    | Modelling of multiphase machines                     | 17   |

| 2.2       | 3.2    | Features of multiphase machines                      | 17   |

| 2.2       | 3.3    | Control of multiphase machines                       | 19   |

| 2.4       | N      | Iodulation methods                                   | 22   |

| 2.4       | 4.1    | Phase-shifted (PS) PWM                               | 22   |

| 2.4       | 4.2    | Level-shifted (LS) PWM                               | 23   |

| 2.4       | 4.3    | Low switching frequency modulation                   | 25   |

| 2.4       | 4.4    | Loss comparison between modulation methods           | 26   |

| 2.4       | 4.5    | Multilevel multiphase modulation methods             | 28   |

| 2.4       | 4.6    | Space vector PWM                                     | 29   |

| 2.5       | В      | atteries – state-of-charge balancing                 | 31   |

| 2.:       | 5.1    | State-of-charge estimation                           | 32   |

| 2.:       | 5.2    | Battery SoC balancing in energy storage applications | 33   |

| 2.:       | 5.3    | Battery SoC balancing in EV applications             | 35   |

|           |        |                                                      |      |

| 2.5.4                                            | Other battery considerations                                                | 36  |  |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------|-----|--|--|--|

| 2.6                                              | Current EV drivetrain solutions                                             | 38  |  |  |  |

| 2.6.1                                            | Half-bridge two-level inverter with a multiphase machine                    | 39  |  |  |  |

| 2.6.2                                            | Cascaded H-bridge (CHB) multilevel inverter with three-phase machine        | 40  |  |  |  |

| 2.6.3                                            | Modular multilevel converter (MMC) with three-phase machine                 | 42  |  |  |  |

| 2.6.4                                            | Modular multilevel series-parallel (MMSP) inverter with three-phase machine | 44  |  |  |  |

| 2.7                                              | Summary                                                                     | 47  |  |  |  |

| Chapter 3 Cascaded H-bridge multilevel converter |                                                                             |     |  |  |  |

| 3.1                                              | Introduction                                                                | 51  |  |  |  |

| 3.2                                              | Cascaded H-bridge topology                                                  | 51  |  |  |  |

| 3.3                                              | Three-phase CHB inverter topology                                           | 53  |  |  |  |

| 3.4                                              | Modulation methods                                                          | 55  |  |  |  |

| 3.4.1                                            | Low frequency modulation                                                    | 57  |  |  |  |

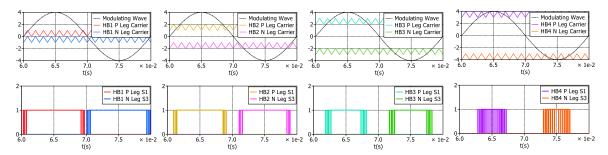

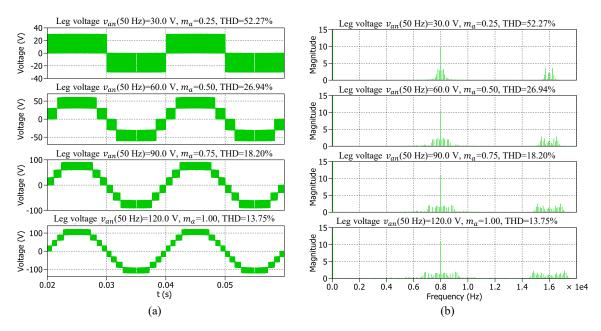

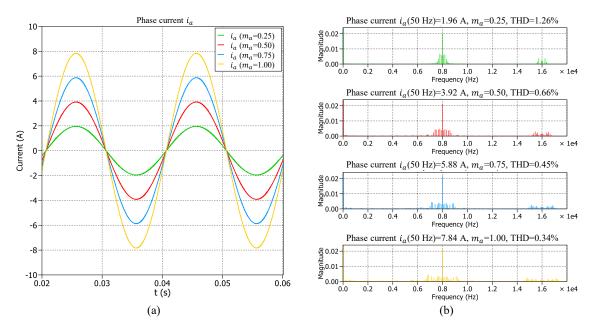

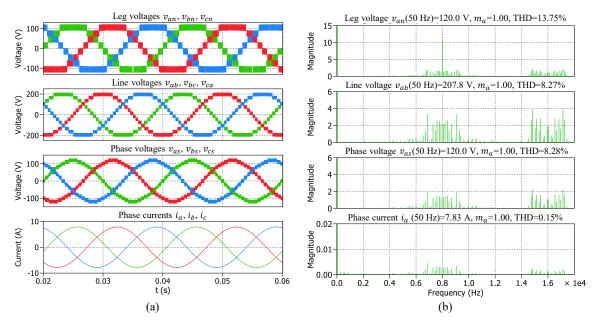

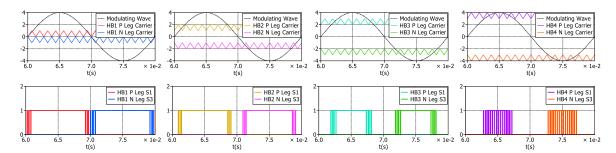

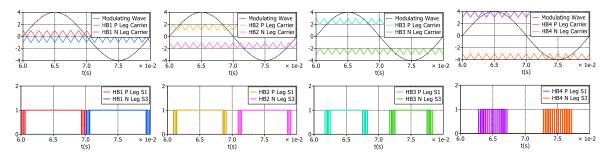

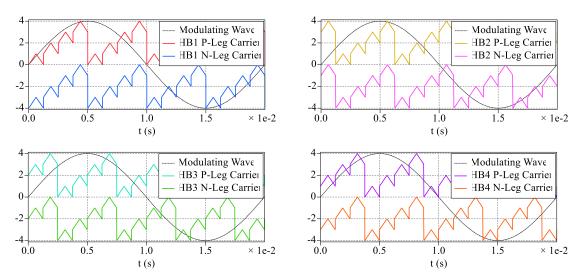

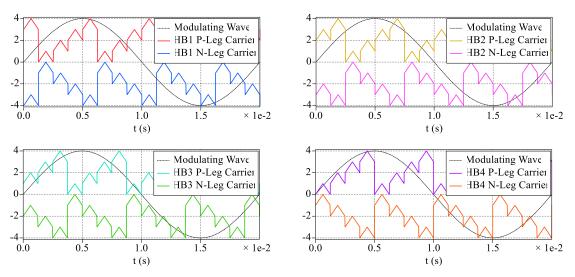

| 3.4.2                                            | Phase-shifted PWM                                                           | 66  |  |  |  |

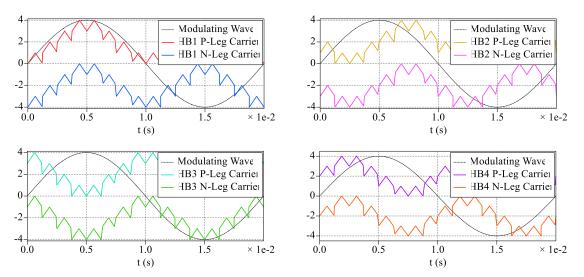

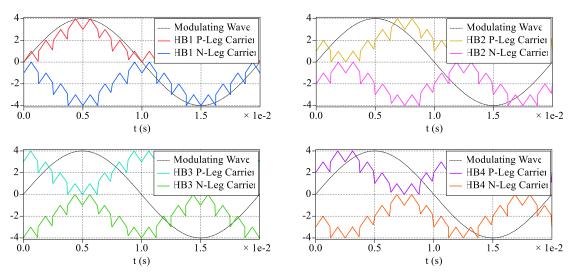

| 3.4.3                                            | Multicarrier level-shifted PWM                                              | 75  |  |  |  |

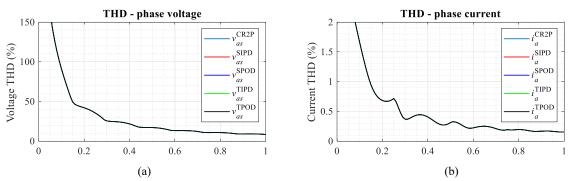

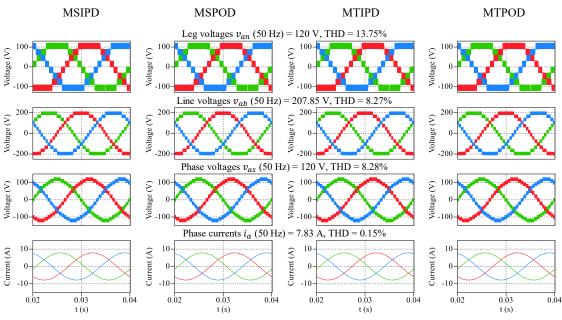

| 3.4.4                                            | Comparison between multicarrier modulation schemes                          | 85  |  |  |  |

| 3.5                                              | Power distribution and equalisation                                         | 87  |  |  |  |

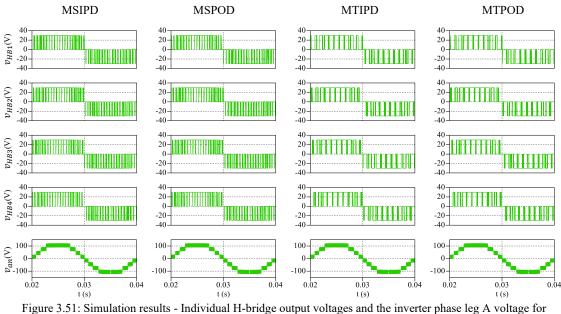

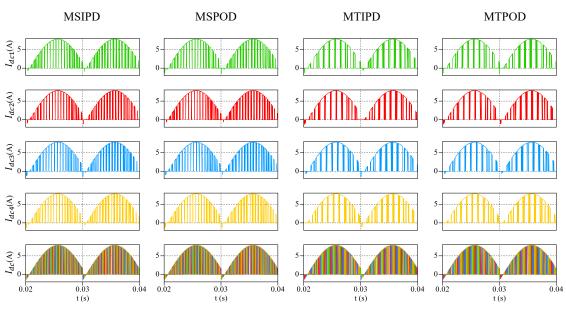

| 3.5.1                                            | DC source utilisation in PS- and LS-PWM                                     | 87  |  |  |  |

| 3.5.2                                            | Fundamental frequency level-shifting                                        | 89  |  |  |  |

| 3.5.3                                            | Carrier frequency level-shifting                                            | 89  |  |  |  |

| 3.5.4                                            | Fundamental frequency reference rotation                                    | 97  |  |  |  |

| 3.6                                              | Summary                                                                     | 100 |  |  |  |

| Chapter 4 C                                      | CHB operation with offset voltage injections                                | 104 |  |  |  |

| 4.1                                              | Introduction                                                                | 104 |  |  |  |

| 4.2                                              | Equal dc-source voltage conditions                                          | 105 |  |  |  |

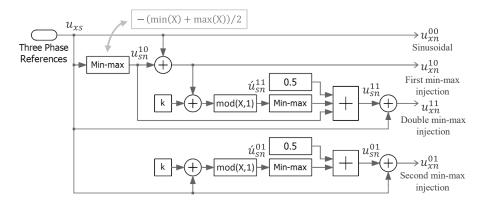

| 4.2.1                                            | Sinusoidal reference (00)                                                   | 107 |  |  |  |

| 4.2.2                                            | First min-max injection (10)                                                | 108 |  |  |  |

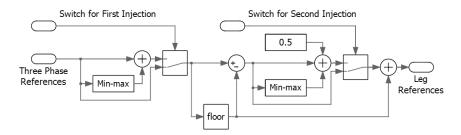

| 4.2.3                                            | Double min-max injection (11)                                               | 109 |  |  |  |

| 4.2.4                                            | Second min-max injection (01)                                               | 109 |  |  |  |

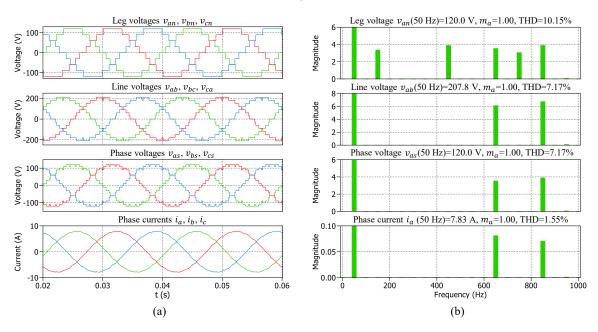

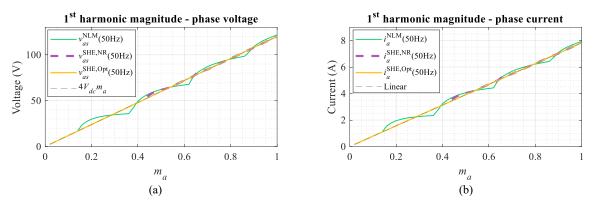

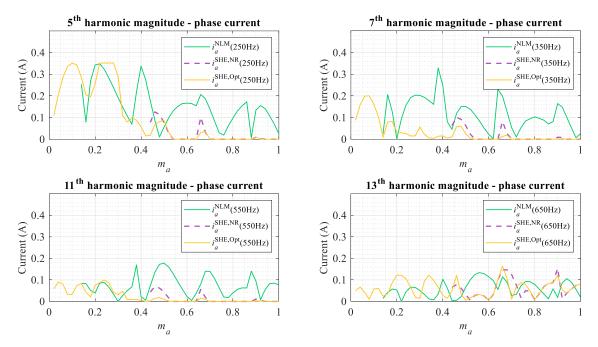

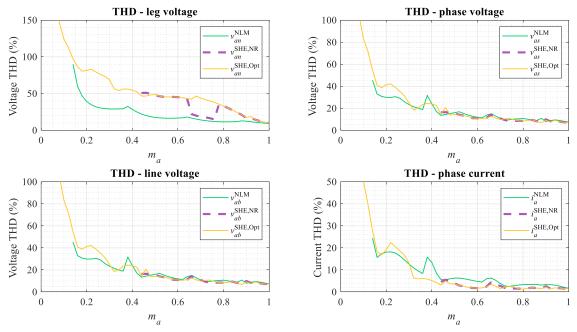

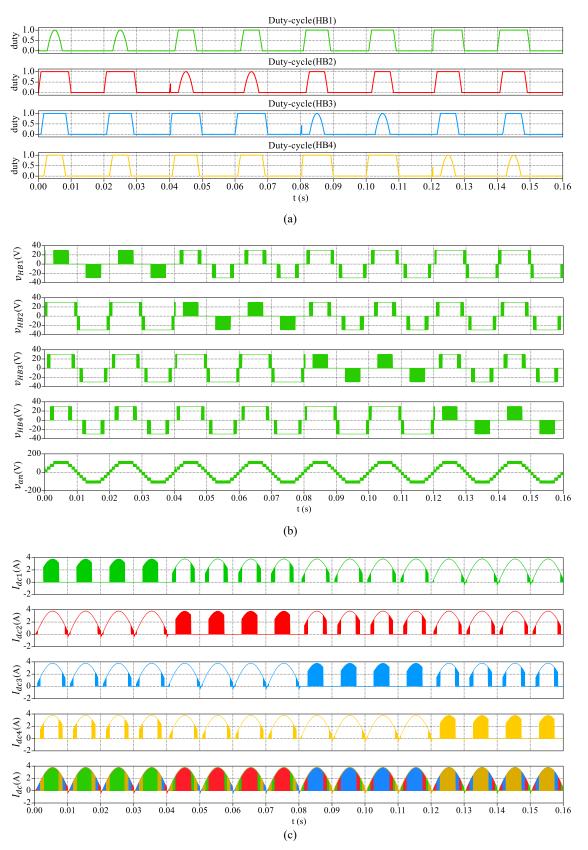

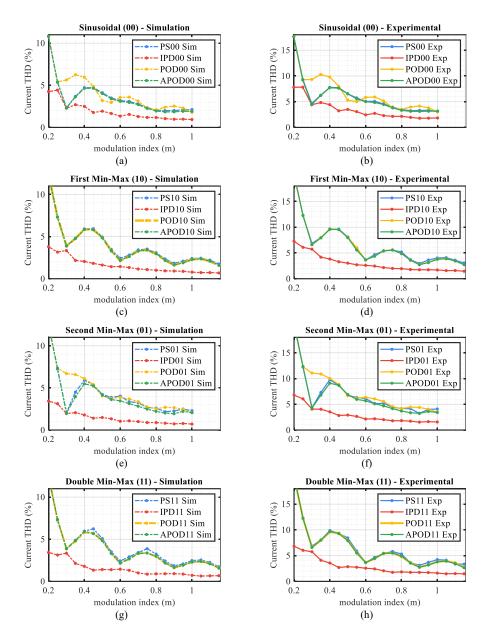

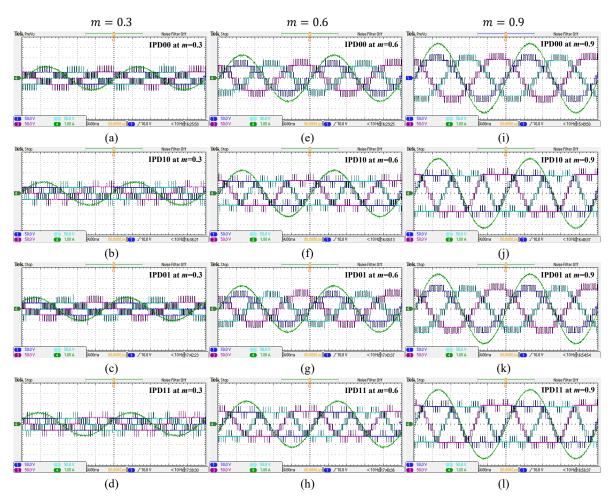

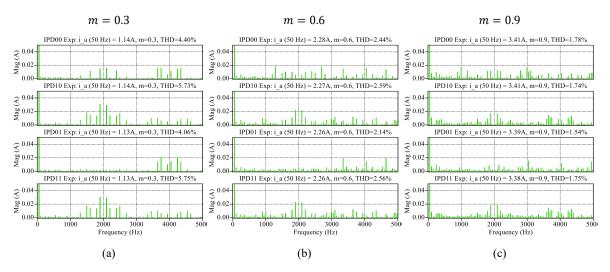

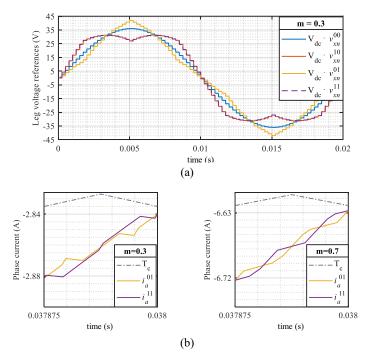

| 4.2.5                                            | Simulation and experimental results                                         | 110 |  |  |  |

| 4.3                                              | Unequal dc-source voltage conditions                                        | 120 |  |  |  |

| 4.3.1                                            | Unbalanced dc-link operation using PS-PWM                                   | 122 |  |  |  |

| 4.3.2                                            | Recommended alternative using LS-PWM                                        | 131 |  |  |  |

| 4.4                                              | Summary                                                                     | 136 |  |  |  |

| Chapter                                                   | r 5 Multiphase machine modelling and control with a multilevel inverter                    | 139       |  |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------|--|

| 5.1                                                       | Introduction                                                                               | 139       |  |

| 5.2                                                       | Modelling of multiphase induction machines                                                 | 140       |  |

| 5.                                                        | 2.1 Phase variable domain model                                                            | 141       |  |

| 5.                                                        | 2.2 Multiphase machine model in arbitrary reference frame                                  | 147       |  |

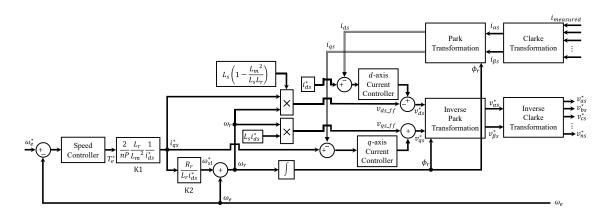

| 5.3                                                       | Rotor flux-oriented control                                                                | 151       |  |

| 5.4                                                       | Multilevel three-phase and multiphase drive                                                | 155       |  |

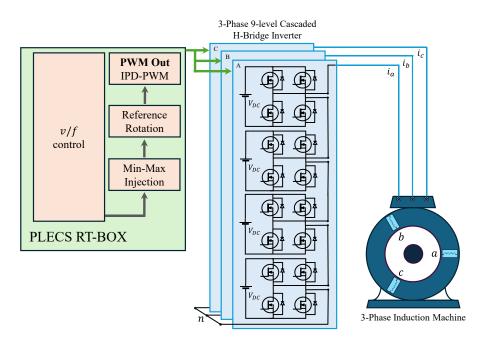

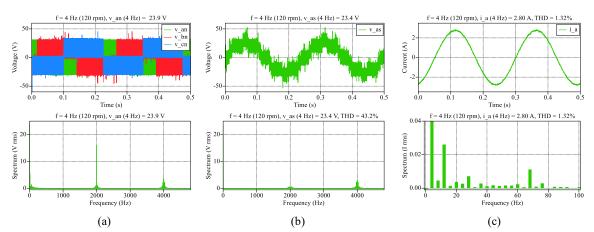

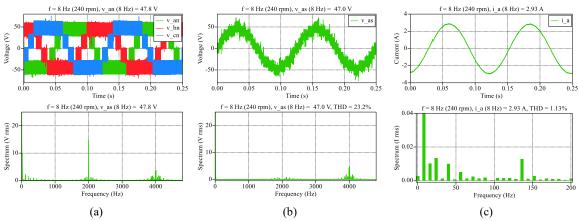

| 5.                                                        | 4.1 Three-Phase IM control using multilevel converter                                      | 156       |  |

| -                                                         | 4.2 High performance control of an asymmetrical six-phase IM using five-lev<br>HB inverter | •         |  |

| 5.                                                        | 4.3 High performance control of an asymmetrical six-phase machine under u                  | nbalanced |  |

| do                                                        | e-source voltages using NVM                                                                | 168       |  |

| 5.5                                                       | Summary                                                                                    | 179       |  |

| Chapter                                                   | r 6 Conclusion                                                                             | 181       |  |

| 6.1                                                       | Summary                                                                                    | 181       |  |

| 6.2                                                       | Future work                                                                                | 184       |  |

| Chapter 7 References                                      |                                                                                            |           |  |

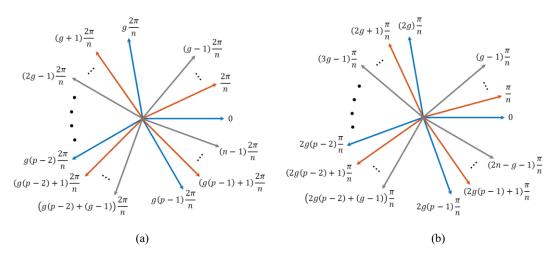

| Append                                                    | lix A Decoupling transformation                                                            | 196       |  |

| A.1 \$                                                    | Single neutral point                                                                       | 196       |  |

| A.2                                                       | Multiple Neutral points                                                                    | 199       |  |

| A.3 ]                                                     | Machine model after VSD transformation                                                     |           |  |

| Append                                                    | lix B Rotational transformation                                                            |           |  |

| Appendix C Asymmetrical six-phase induction machine model |                                                                                            |           |  |

| Appendix D List of publications                           |                                                                                            |           |  |

| D.1 Publications                                          |                                                                                            |           |  |

| D.2                                                       | Co-authored publications                                                                   |           |  |

## List of Abbreviations

- AC Alternating current

- APOD Alternate phase opposition disposition

- BESS Battery energy storage systems

- BEV Battery electric vehicle

- BMS Battery management system

- CHB Cascaded H-bridge

- CMV Common mode voltage

- DC Direct current

- DSP Digital signal processor

- DTC Direct torque control

- EMI Electromagnetic interference

- EMF Electro-motive force

- EV Electric vehicle

- FC Flying capacitor

- FOC Field-oriented control

- FACTS Flexible ac transmission systems

- FC Flying capacitor

- FSHE Fundamental selective harmonic elimination

- IGBT Insulated-gate bipolar transistor

- IGCT Integrated gate-commutated thyristor

- IM Induction machine

- IPD In-phase disposition

- IRFOC Indirect rotor flux-oriented control

- LS Level-shifted

- Li-ion Lithium-ion

- MMF Magneto-motive force

- MTPA Maximum torque per ampere

- MV Medium voltage

- MM Min-max

- MMC Modular multilevel converter

- MPC Model predictive control

- MMC Modular multilevel converter

- MMSP Modular multilevel series-parallel converter

- MOSFET Metal-oxide-semiconductor field-effect transistor

- MSIPD Multilevel sawtooth in-phase disposition

- MSPOD Multilevel sawtooth phase opposition disposition

- MTIPD Multilevel triangular in-phase disposition

MTPOD Multilevel triangular phase opposition disposition

MLI Multilevel inverter

- NLM Nearest level modulation

- NPC Neutral point clamped

- NVM Neutral voltage modulation

NEDC New European Driving Cycle

NiMH Nickel metal hydride

NPC Neutral point clamped

OEM Original equipment manufacturer

OEW Open-end winding

PMSM Permanent magnet synchronous machine

POD Phase opposition disposition

PTC Predictive torque control

PI Proportional-integral

PR Proportional-resonant

PS Phase shifted

PWM Pulse width modulation

RFOC Rotor flux-oriented control

SHE Selective harmonic elimination

SiC Silicon carbide

SV Space-vector

SoC State-of-charge

STATCOM Static synchronous compensator

- SRM Switched reluctance machine

- THD Total harmonic distortion

- THI Third harmonic injection

- V2G Vehicle to grid

- VSD Vector space decomposition

- VSC Voltage source converter

- VSI Voltage source inverter

WLTP Worldwide Harmonised Light Vehicle Test Procedure

## List of Symbols

- v Voltage in general (determined by index)

- *i* Current (determined by index)

- *n* Number of inverter or machine phases, or inverter neutral point

- *a*, *b*, *c* Inverter, machine, or load phases

- $m, m_a$  Amplitude modulation index

- *h* Harmonic number

- *k* Number of H-bridge modules per phase leg

- *l* Number of voltage levels of a waveform

- $T_m$  Fundamental period of the modulating wave

- $T_c$  Carrier wave fundamental period

- $T_s$  Switching time period

- $f_m$  Frequency of modulating wave

- $f_{sw}$  Switching frequency

- $f_{sd}$  Device switching frequency

- $f_{sd,avg}$  Average device switching frequency

- $f_{si}$  Effective inverter switching frequency

- $f_c$  Carrier frequency

- $f_m$  Frequency of the modulating or reference waveform

- $f_{smc}$  Frequency of the sawtooth multilevel carrier waveform

- $f_{tmc}$  Frequency of the triangular multilevel carrier waveform

- $t_{cd}$  device conduction times

- $V_{\rm dc}$  dc-link voltage

- $I_{dc}$  dc current of H-bridge module dc-source

- g Number of winding sets

- *p* Phases per winding set

- $\theta$ ,  $\alpha$ ,  $\phi$  Angle in radians

- $\alpha, \beta, x, y, z_+, z_-$  Indices denoting values after Clarke's transformation

- d, q Indices denoting values after Park's transformation

- $\psi$  Flux-linkage

- s In subscript denotes stator quantities, or star connected load neutral point

- r In subscript denotes rotor quantities

- $\omega$  Angular frequency in radians per second (unless stated otherwise)

- $\omega_m$  Mechanical speed of rotation

- $\omega_e$  Electrical speed of rotation

- *P* Number of magnetic pole pairs

- *T<sub>e</sub>* Electromagnetic torque

- $T_l$  Load torque

- *J* Inertia of the rotating mass

- *R* Resistance (determined by index)

- *L* Inductance (determined by index)

- *M* Maximum value of the mutual magnetising inductance

# Chapter 1 Introduction

### 1.1 Preliminary considerations

The transportation system contributes significantly to the emission of greenhouse gasses worldwide. In the UK, it is the largest contributor to the total greenhouse emissions as of 2017. With the sale of new petrol and diesel engine vehicles set to cease from 2030, the UK government's Road to Zero Strategy has outlined the transition to a more sustainable and environmentally friendly transportation system and aimed to achieve a planned target of 100% EV sales by 2035 (Dempsey and Hinson, 2020). Similar policy decisions globally have initiated a gradual shift towards the electrification of the transportation system. It is predicted that by 2030, 80% of all electrical energy will be processed by power electronics and electric vehicles are expected to play a major role in this transformation. Full or partially electric powertrains are growing significantly and by 2035 they will account for around 50% of the automotive market as projected in a report by the International Energy Agency (IEA, 2024).

The shift towards the electrification of the transportation system has stimulated significant research into finding optimum solutions for electric vehicle (EV) powertrain systems. Higher purchase price, lack of EV charging infrastructure, and battery charge time are all impediments to widespread EV adoption. However, one of the primary bottlenecks in the large-scale adoption of EVs is limited range. This issue needs to be addressed through research into improving storage density of the current battery technology at a reasonable cost. Concurrently, however, improvement in the function and efficiency of other drivetrain components also requires thorough investigation. Research into potential improvements that can be made in the design of the power electronic converter, energy storage system, and the selection of suitable electrical traction machines would contribute towards maximising the overall efficiency of the EV drivetrain and help alleviate range anxiety.

The internal combustion engine is notoriously inefficient with most cars achieving an overall efficiency in the range of 10%-20%, whereas current EVs are known to be at least three to five times more efficient (Bilgin et al., 2015). However, studies have shown that

although the inverters and electric motors operate at reasonably higher efficiencies at nominal loads, their efficiency drops considerably during partial load operation [(Agamloh, 2009); (Knischourek et al., 2012); (Chang et al., 2017); (Negahdari et al., 2019)]. Thus, there is considerable potential in terms of the savings from further optimising the performance of electric vehicle powertrain to achieve significantly higher efficiencies under all operating conditions, thereby increasing the range of an EV.

This research aims to improve the drawbacks of current EV drivetrains by introducing a novel design concept for increased overall drivetrain efficiency. It investigates an innovative approach for drivetrain design where the converter is integrated with the batteries to provide excitation to a multiphase electric machine for propulsion. Integration of the batteries with the power electronics will create a multilevel structure of the inverter output voltage with excellent output waveform quality, even at low switching frequency, while benefitting from higher multiphase machine efficiency and achieving space and weight reduction in an EV.

#### 1.2 Potential benefits of the proposed solution

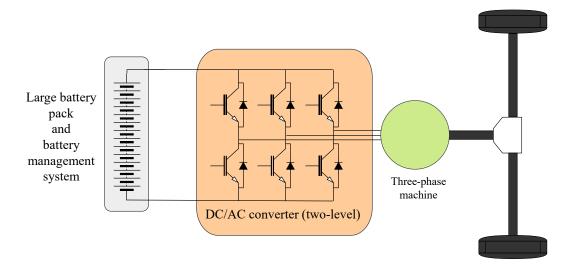

A three-phase machine primarily owes its existence to the adoption of the three-phase grid in the early twentieth century. An electric vehicle is battery powered and there is no requisite limitation on the number of phases of the propulsion machine. However, most current solutions for electric vehicle drivetrain primarily employ a single three-phase AC traction motor, a dc-ac power electronic converter and a single large battery pack, as shown in Figure 1.1. In addition, a battery management system (BMS) and an on-board (slow) battery charger are also provided for better reliability and practicality. This solution is expensive, inefficient and contains elements which are used occasionally, but constantly occupy extra space and represent extra load in an EV.

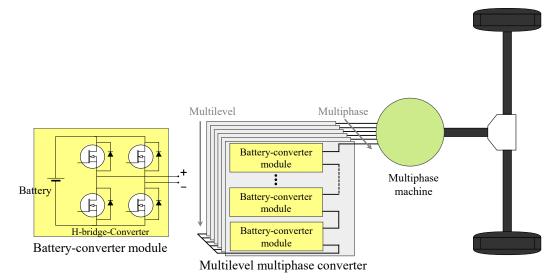

Integration of the batteries with the power electronics will simplify and improve the drivetrain because it can act as an active BMS, hence, eliminating the need for an additional BMS. The single battery pack will be broken down into multiple battery-converter modules making the system modular and distributed. In the case of a multiphase machine, these smaller battery-converter packs can then be used to individually supply each phase of the motor (see Figure 1.2). Splitting the power into smaller energy battery-converter packs would further improve the system and allow it to operate at lower voltages.

It is intended for the same system to be capable of being used in either of the two charging modes: single-phase – slow, or three-phase – fast AC charging. Consequently, usage of a multiphase machine can eliminate the need for additional charger commonly present in current EVs. A nine-phase machine albeit with a two-level inverter was shown to charge a single large battery by (Subotic et al., 2015). Lastly, the use of a multiphase machine enables the drive to have built-in fault tolerance capability (Duran and Barrero, 2016).

In addition to the above, with the battery-converter integration, the splitting of the battery pack into smaller units would result in the cables conducting much lower currents (e.g. 20-30 A) instead of the customary 300 A. Furthermore, the use of a cascaded battery structure will also significantly improve safety when an EV with modular battery packs is undergoing service or maintenance. This is because the maximum voltage in the car is equal to the battery pack voltage, which will be significantly reduced due to the splitting-up of the battery pack into multiple smaller units of lower total voltage (Chang et al., 2019). Furthermore, (Chang et al., 2019) have shown that the efficiency of the standard two-level inverter at partial loads is typically not very good, and it was shown to be considerably improved using a multilevel Si transistor-based inverter. Therefore, by splitting the battery and integrating it within a multilevel converter, the efficiency can be improved.

For propulsion, contemporary electric vehicles primarily employ either the three-phase permanent magnet or induction type motors in combination with a three-phase voltage source converter. While, for charging of the EV's battery bank, an additional charging unit is normally installed on the EV. However, since both the on-board charger and the power electronic components used during the propulsion mode are essentially similar, recent research has been directed towards the integration of the power electronics used for propulsion and charging. This would make a separate charging unit redundant and, consequently, offer potential savings in terms of cost, spare space, lesser weight, and associated savings on running fuel cost (Subotic et al., 2015). Although, not studied in this project, the designed topology is also potentially suitable to enable Vehicle-to-grid (V2G) mode of operation.

Figure 1.1: A typical EV drivetrain topology (simplified).

Figure 1.2: The proposed multilevel multiphase drivetrain topology (simplified).

### 1.3 Research objectives and novelty

This project is aimed at improving the drawbacks of currently used EV drivetrains which are primarily based on the two-level inverter drive with a three-phase machine for propulsion. An innovative approach for drivetrain design was investigated where a multilevel cascaded H-bridge converter with integrated batteries and a multiphase electric machine is used for propulsion. The following key objectives were formulated to meet the aim:

1. To investigate and compare different modulation methods applicable for a multilevel structure using a cascaded H-bridge (CHB) multilevel inverter (MLI) for the entire

modulation index range in terms of the harmonic performance of the phase voltages and currents.

- 2. To design appropriate battery state-of-charge balancing algorithm through the appropriate rotation of the reference or carrier waveforms to achieve balanced operation of the inverter (equalise dc-sources).

- 3. To develop a method that accounts for the naturally expected dc-source voltage/state-of-charge imbalance to achieve balanced operation of the machine (overcome unequal leg voltages).

- 4. To develop control algorithm for multiphase machine which includes the previously formulated algorithm, and which will enable propulsion.

- 5. To test the developed control algorithms by simulation, verify them experimentally in the laboratory conditions, and compare the performance.

The originality of the conducted research can be attributed to the achievement of the aforementioned objectives. The application and comparison of different min-max based offset voltage injections in a symmetric three-phase CHB inverter were studied in (Khan et al., 2022). It resulted in the conclusive determination of the second min-max offset injection and the double min-max offset voltage injection as the most optimal solutions among the tested injection methodologies in terms of the harmonic performance of the phase current in CHB inverters. The issue of unequal dc-source utilisation and equal power distribution in the level-shifted PWM was also discussed and a solution based on the cyclic rotation of the carriers and the resulting battery currents was presented.

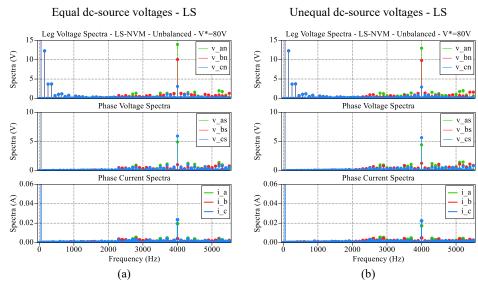

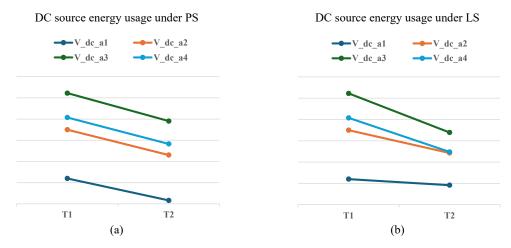

Next, the performance of the so-called neutral voltage modulation (NVM) method, developed by (Kim and Cho, 2022) using the phase-shifted (PS) PWM for unbalanced dc-source voltage conditions, was improved with an appropriate modification of the level-shifted (LS) PWM in (Khan et al., 2024b). The operation of the CHB inverter under unbalanced dc-source voltages resulted in superior harmonic performance of the inverter phase currents while achieving extension of the modulation index range. The issue of the switching harmonic ripple at twice the carrier frequency associated with the PS-PWM in unequal dc-source voltage condition was successfully mitigated with the suggested adjustment of the LS-PWM method. The suggested solutions also showed enhanced energy

management of the dc-sources for extended operation, when compared to the originally proposed method.

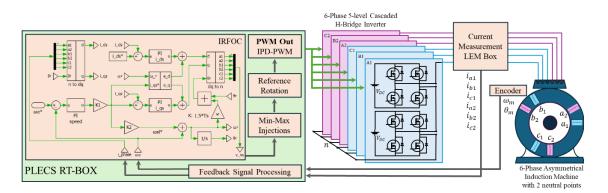

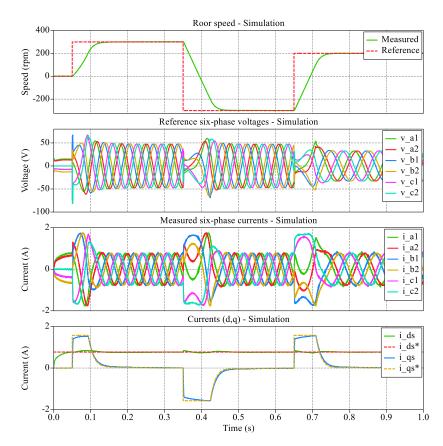

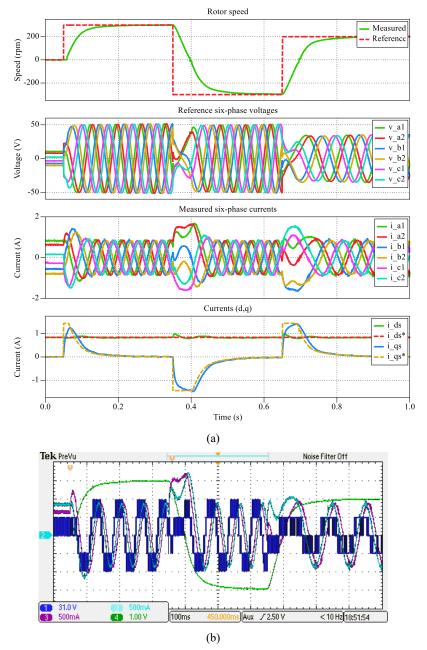

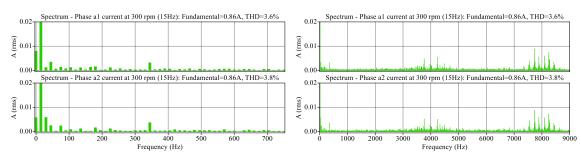

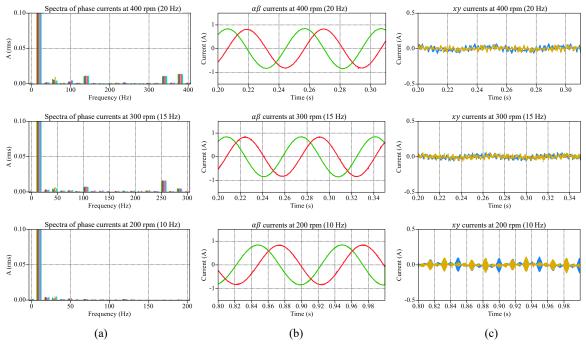

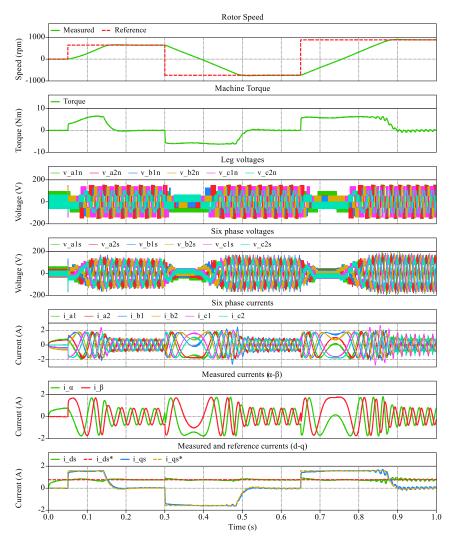

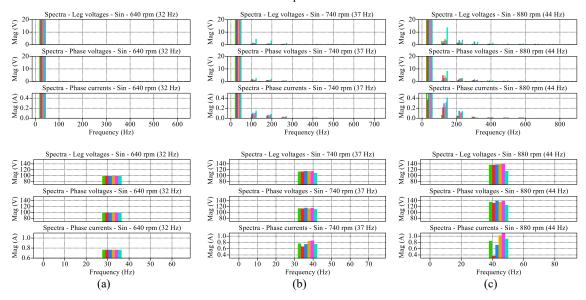

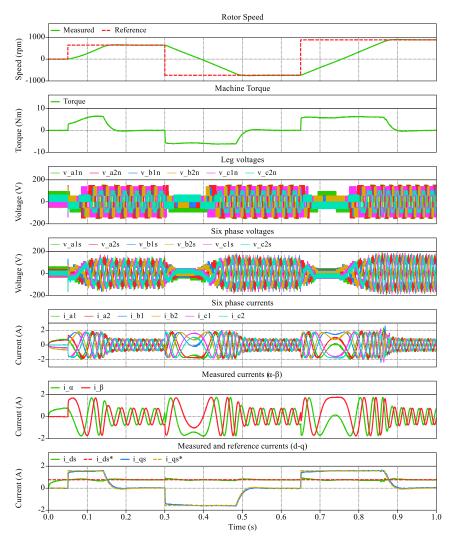

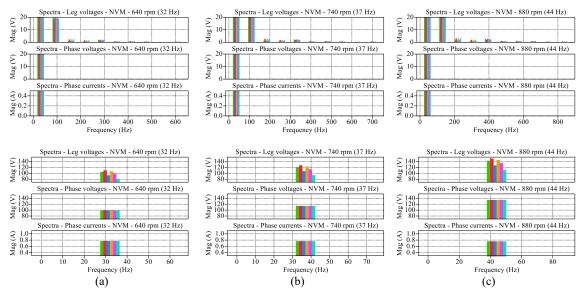

After that, the implementation of a high-performance control of a six-phase induction machine (IM) for EV application using a battery-supplied five-level CHB-MLI was shown for the first time in (Khan et al., 2024a). The validity of the designed system for the operation of the drivetrain under different reference speeds was confirmed. The obtained results showed low harmonic distortion of the machine voltages and currents at a relatively low switching frequency.

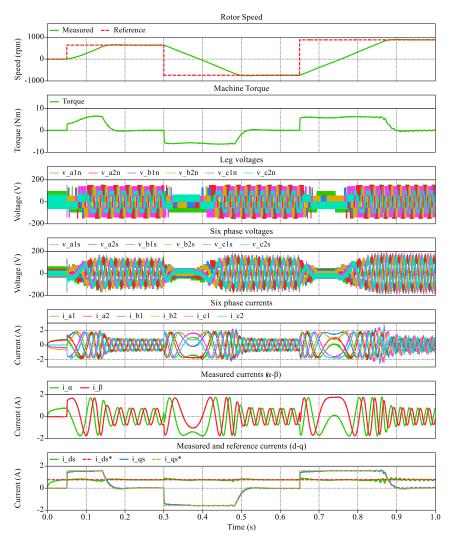

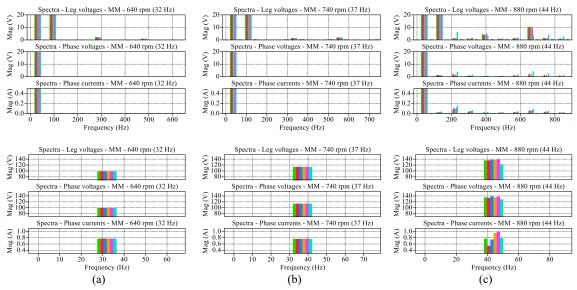

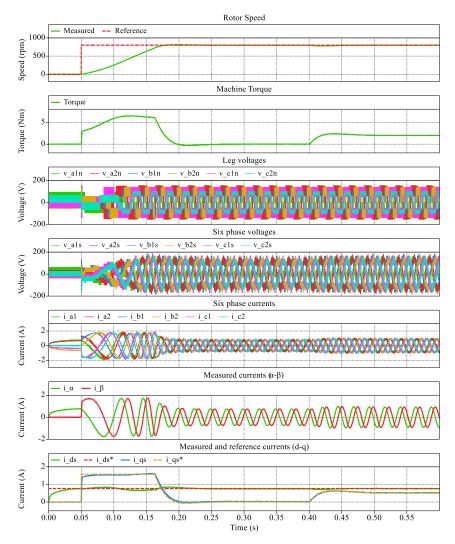

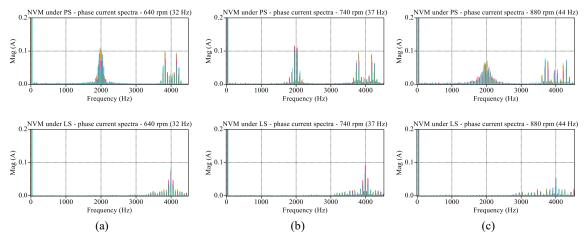

Finally, the application of the methodology developed in (Khan et al., 2024b) for three-phase systems was applied (in simulation) for the first time to the high-performance control of an asymmetrical six-phase induction machine under unequal dc-source voltages (subsection 5.4.3). The obtained results confirmed the extension of the modulation index range under dc-source voltage imbalance where the balanced operation of the six-phase machine was shown for different speeds. In this way, the inevitable total dc-source (and inverter leg) voltage imbalance was countered successfully to achieve balanced machine operation with significantly lower total harmonic distortion of the machine currents, as well as the elimination of the first harmonic ripple (and its sideband harmonics) at double the carrier frequency, seen in the application of NVM under phase-shifted PWM. The list of papers, which are the outputs of the thesis, are given in Appendix D.

#### **1.4 Organisation of the report**

This thesis is organised into seven chapters. The first chapter introduces the topic and provides the necessary background and motivation for research. A simplified description of the proposed solution and its potential benefits are compared to contemporary EV drivetrain solutions. Next, the research objectives and originality are given.

Chapter 2 provides an extensive literature survey on topics relevant to this project. The literature survey begins with a description of multilevel converters and their topologies including classic and hybrid multilevel topologies. Next, relevant literature on multiphase machine modelling, features of multiphase machines and their suitability for EV applications, and various control strategies for multiphase machines are discussed. The following section provides a substantial review on modulation methods including various low and high frequency modulation methods and their features. Relevant literature

comparing converter losses under different modulation methods is also presented. Subsequently, literature on battery state-of-charge estimation and balancing is presented, which includes relevant literature on state-of-charge balancing in energy storage and electric vehicle applications. Lastly, a literature review covering current drivetrain solutions for battery electric vehicles (BEV) is presented. This includes relevant publications on converter topologies such as half-bridge, cascaded H-bridge, modular multilevel converters, and modular multilevel series-parallel converters. The literature focuses on converter efficiency comparison between different topologies under different modulation schemes and different drive cycles.

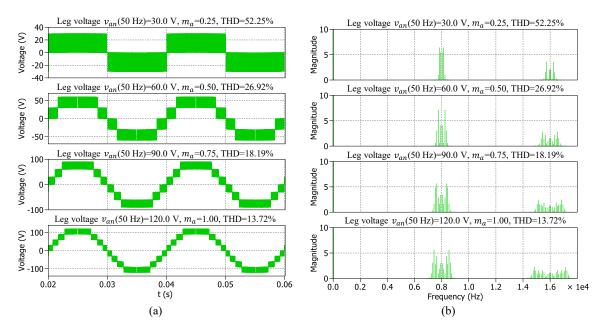

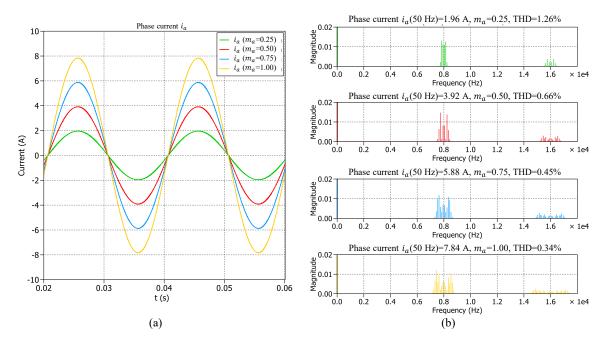

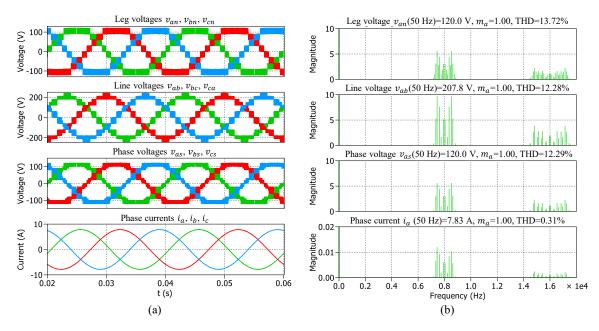

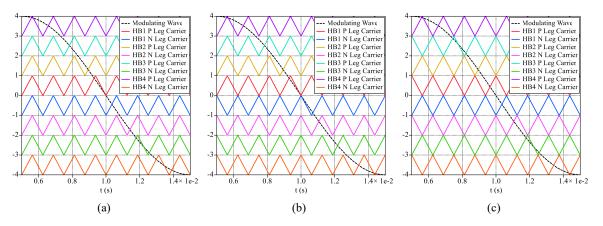

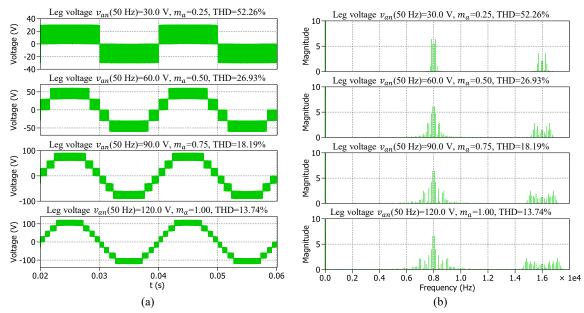

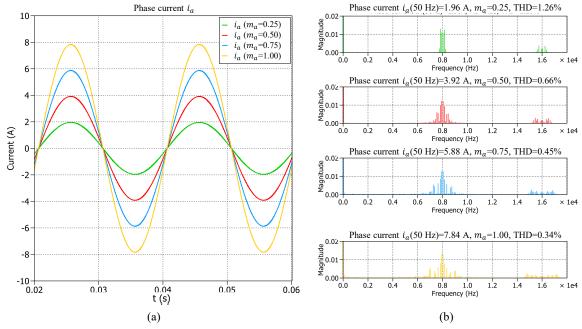

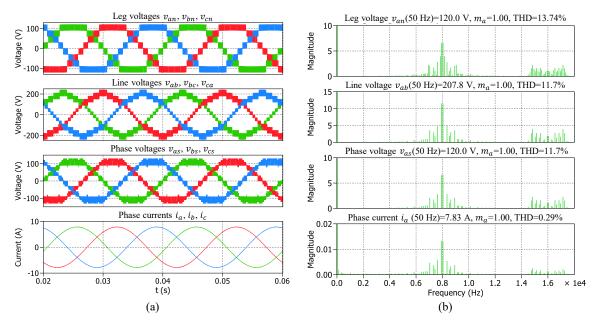

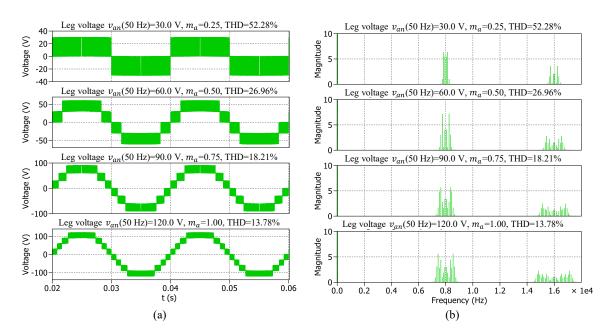

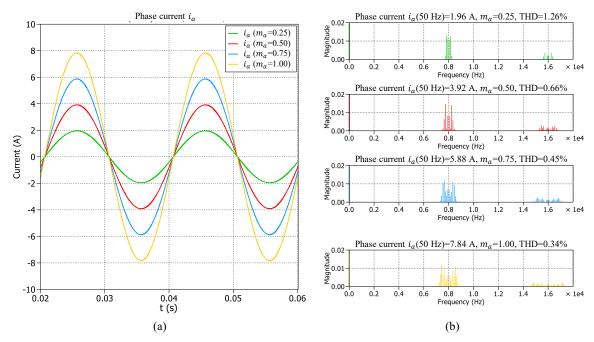

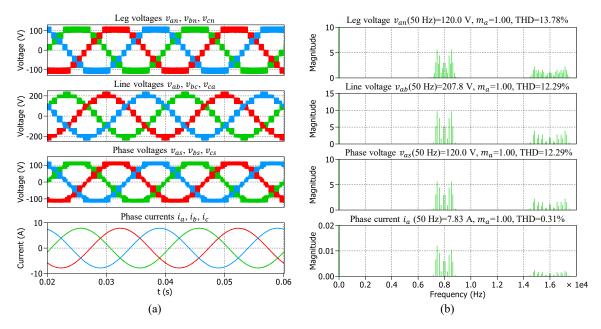

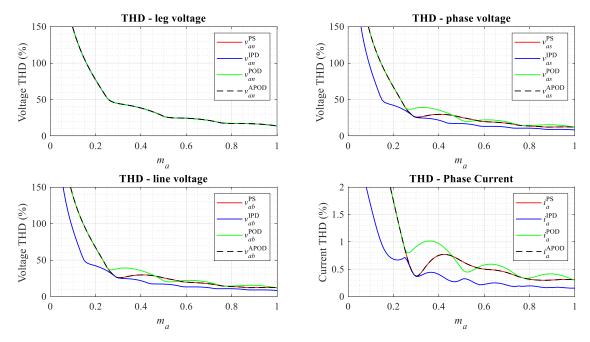

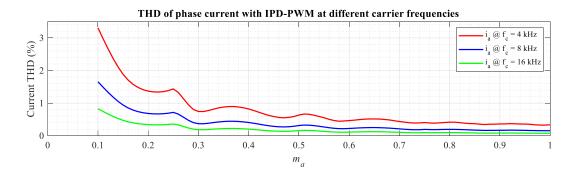

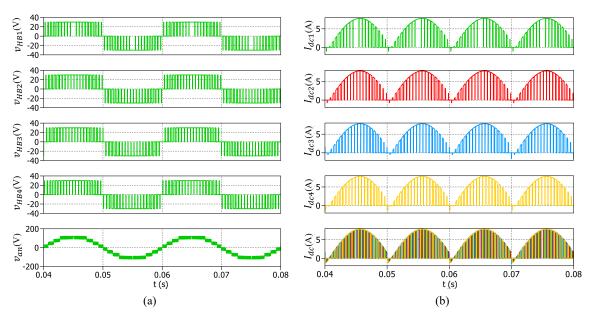

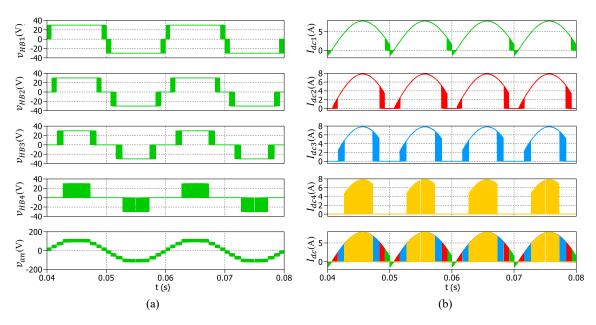

Chapter 3 describes the cascaded H-bridge (CHB) topology. Next, different low and high frequency modulation methods applicable to the CHB are described in considerable detail. Each method is implemented on a 9-level CHB converter connected to a single- and three-phase *RL* load. A comparison is made between the performance of the modulation methods in terms of the total harmonic distortion (THD) of the voltages and current waveforms over the complete modulation index range. Following that, the issue of equal power distribution in the level-shifted modulation method is discussed and appropriate carrier and reference rotation strategies are described and compared for the whole modulation index range in terms of the total harmonic distortion of the voltage and current waveforms.

Chapter 4 expands on the operation of the CHB-MLI under balanced and unbalanced dc-source voltage conditions. First, various min-max based offset voltage (zero-sequence) injections, under different carrier-based PWM methods, are described and tested in simulation and experimentally on an *RL* load, where the dc-source voltages of a CHB inverter are all considered to be equal. The described offset voltage injections are compared with each other in terms of the total harmonic distortion of the produced voltages and currents for different points of the modulation index range to determine the best choice. Next, the operation of a CHB inverter under unequal dc-source voltage conditions is investigated. Performance of the previously mentioned NVM method vis-à-vis the phase-shifted PWM method is examined for a nine-level three-phase CHB inverter. The described issues are resolved with the modification of the standard level-shifted PWM method to account for unbalanced dc-source voltage conditions and the application of the NVM for the

extension of the modulation index range. A comparison between the original and the suggested method is shown, and the improvements in the performance are highlighted.

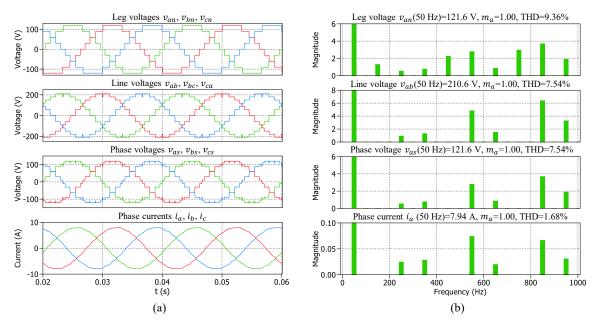

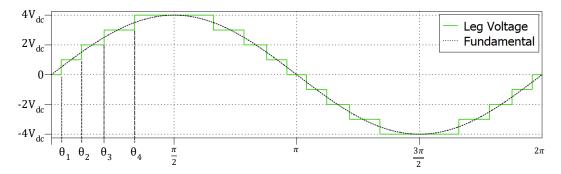

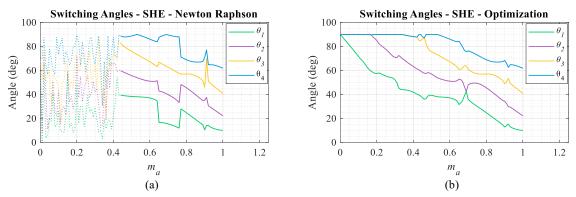

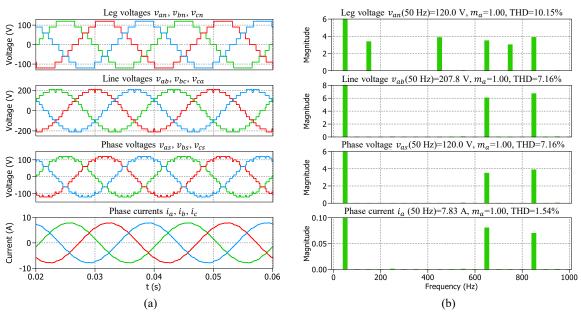

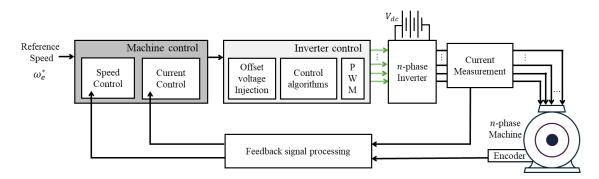

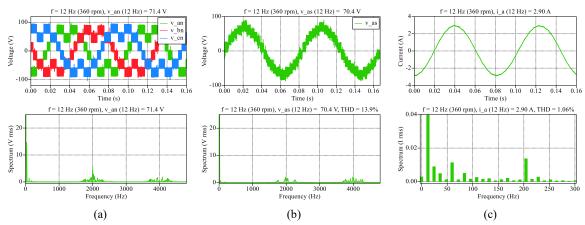

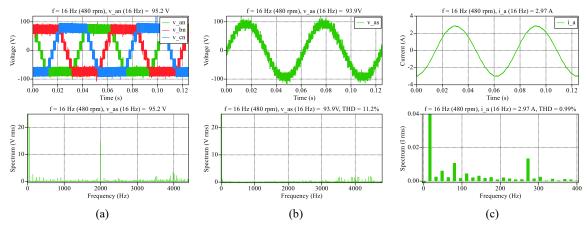

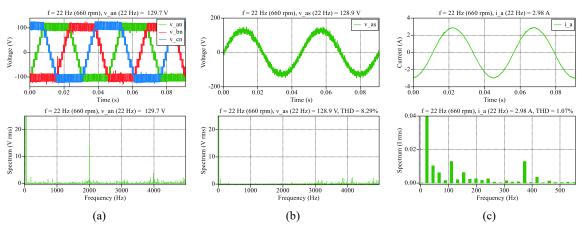

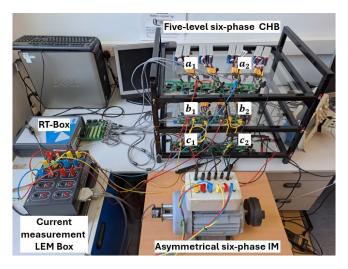

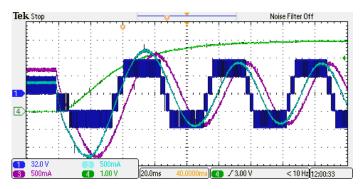

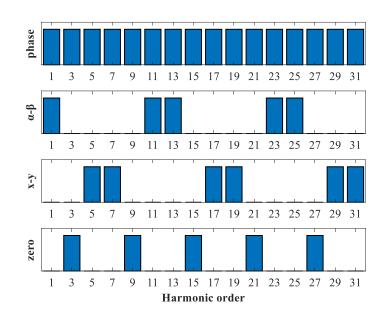

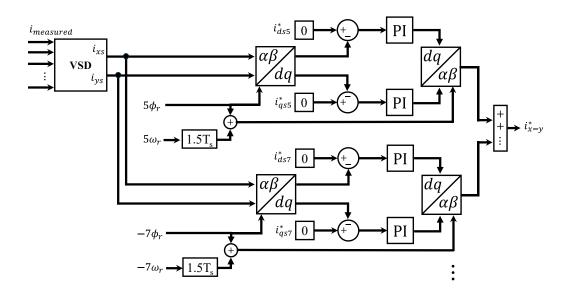

Chapter 5 starts with a discussion on multiphase machine modelling followed by a description of the field-oriented control using the rotor-flux orientation principle. Next, the operation of the multilevel CHB inverter is verified experimentally with open-loop control of a three-phase induction machine for different operating frequencies corresponding to different points on the modulation index range. This is followed by the description and implementation of the high-performance control of a multilevel (>2) multiphase (>3) drive where a battery-supplied five-level six-phase CHB inverter feeds an asymmetrical six-phase induction machine. The operation of the system is confirmed in simulation and verified experimentally for different speeds of operation. The obtained waveforms are analysed to show significantly superior performance control of the same drive is investigated in unequal dc-source voltage conditions where the previously developed methodology is successfully employed (in simulation) to a multiphase machine. The obtained results demonstrate the correctness of the developed system along with the improvement over the originally proposed method.

Chapter 6 provides a summary of the completed work and offers different research directions for future work. This is followed by a list of references in Chapter 7. Finally, the end of the thesis contains appendices, where the vector space decomposition transformation, for symmetrical and asymmetrical machines with different neutral point configurations, is given in Appendix A. Next, the rotational transformation is given in Appendix B, followed by the presentation of the model of the asymmetrical six-phase induction machine in the rotational reference frame, which was used for simulation, in Appendix C. A list of the publications resulting from the thesis are provided in Appendix D.

# Chapter 2 Literature survey

#### 2.1 Introduction

In this chapter a detailed literature survey of the topics relevant to this project is given. The chapter begins with a general discussion and review of prominent multilevel inverter topologies in section 2.2. Next, the most prominent classic multilevel inverter topologies, i.e., the neutral point clamped (NPC) and the flying capacitor (FC) are reviewed. Thereafter, the cascaded H-bridge (CHB) topology is reviewed in depth, relevant literature is presented, and early important papers that propose the use of a CHB multilevel inverters (MLI) as traction inverters are reviewed. After that, other derivative and hybrid topologies for different applications are also presented and reviewed.

In section 2.3, a review of the modelling techniques of multiphase machines using vector space decomposition (VSD) and multiple d-q approach is provided. Prominent features of multiphase machines, their relevance and application to electric vehicles are examined. Next, multiphase machine control is addressed. A review of the most prominent control techniques such as field-oriented control (FOC), direct torque control (DTC), predictive torque control (PTC), model predictive control (MPC), and their respective strengths and drawbacks are reviewed.

In section 2.4, a discussion on different modulation techniques for multilevel inverters is presented. Modulation methods discussed include the phase-shifted (PS) and level-shifted (LS) pulse width modulation (PWM) strategies, and strategies focusing on the equal power distribution associated with LS-PWM modulation method. Next, a review on the selective harmonic elimination (SHE) technique, including the known methods for solving the SHE equations, is presented. The following subsection reviews literature related to the efficiency analysis of various modulation methods for the CHB inverter. After that, a literature survey on modulation techniques applicable for two-level and multilevel multiphase inverters is presented. The section concludes with a survey on space-vector PWM.

Section 2.5 provides a review of battery technology typically utilised for EV applications. A survey on battery state of charge (SoC) estimation methods and preferred

choices for EV applications are presented. Subsequently, a detailed review on battery SoC balancing is provided. The intrinsic structure of cascaded multilevel inverters makes them particularly suitable for integration with energy storage systems and EV batteries. Therefore, most literature surveyed here relates to multilevel inverter (MLI) application in the SoC balancing in battery energy storage systems (BESS) application which is closely related to the field of this research. Next, a survey of papers discussing battery SoC balancing methods related to EV applications is given. The section concludes with a discussion on other related aspects such as battery longevity and battery losses.

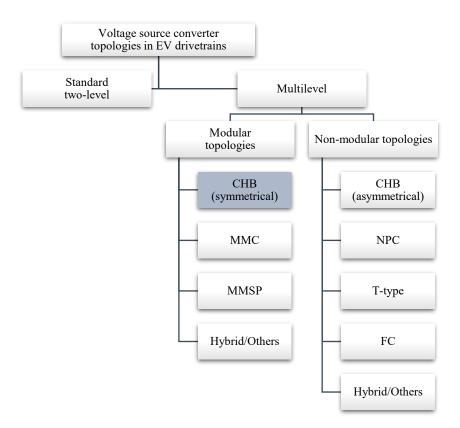

Section 2.6 begins with a general overview of the current EV drivetrain solutions. An overview of recent literature for current EV drivetrains in terms of inverter topologies and semiconductor devices is provided next. The literature surveyed here considers prominent topologies and the discussion is limited to modular and cascade topologies such as the cascaded H-bridge (CHB) multilevel inverter, modular multilevel converter (MMC), and the modular multilevel series-parallel converter (MMSP) supplying three-phase traction machines in an EV. The content of the literature survey chapter is summarised in section 2.7.

#### 2.2 Multilevel inverters

The two-level voltage source converter is the most commonly used topology in variable speed drives and in most contemporary EVs because of its simplicity and reliability (Poorfakhraei et al., 2021a). However, it produces an output voltage waveform of a square shape with sudden periodic changes of peak voltage, i.e., a very high rate of change in the voltage. This is known to cause the issues such as leakage of current through the insulation in motor windings caused by the combination of the insulation and conductors acting as a capacitance. This is generally mitigated through the use of passive LC output filters which are large and expensive (Abu-Rub et al., 2010). A high  $d\nu/dt$  is also responsible for causing electromagnetic interference with sensitive electronic equipment located around the motor-inverter connection.

An inverter that produces three or more voltage levels at the output terminals can be classified as a multilevel inverter. Multilevel converter development was initiated in response to the demand for converters capable of delivering higher power and voltages with minimal harmonic distortion in the output voltages and currents whilst operating at relatively low switching frequencies. In essence, an increase in the number of output voltage levels causes the synthesised waveform to resemble a sinusoidal waveform, and as a natural consequence, amounts to lower harmonic distortion. Therefore, multilevel converters have been in development since late 1960s (Malinowski, 2017) and have since found use in various industrial applications, such as power distribution and interfacing between renewable energy sources and the utility grid.

First known patent of multilevel inverters is from (Baker and Bannister, 1975) where a staircase ac output waveform was produced using series connected multiple full-bridge cells using isolated dc sources. This came to be known as the cascaded H-bridge (CHB) multilevel converter (Rodriguez et al., 2002). Thereafter, the capacitor clamped multilevel converter was introduced where capacitors are neither connected to the positive nor to the negative dc rails – hence, named flying capacitor (FC) topology. In 1979, clever manipulation of the cascaded converter by blocking the sources using diodes to clamp the voltage resulted in the formation of a three-level neutral point converter (NPC), also known as the diode-clamped converter (Akagi, 2017). This type of converter has traditionally been used in industrial medium-voltage (MV) drives. Consequently, these three topologies came to be classified as the classic multilevel inverter topologies due to considerable research on these topologies and their extensions.

These classic multilevel topologies were together presented in an important paper by (Lai and Peng, 1996) where the authors describe the basic operating principles, salient features, limitations and potential applications of the three primary multilevel converter types, i.e. the NPC, FC and CHB inverters. Subsequently, operating principles and control techniques of these topologies have been comprehensively covered in several notable works [(Rodriguez et al., 2002); (Rodriguez et al., 2007); (Panagis et al., 2008); (Kouro et al., 2010); (Malinowski et al., 2010); (Abu-Rub et al., 2010); (Akagi, 2017); (Leon et al., 2017); (Wu and Narimani, 2017)]. In addition, these works provide a thorough discussion of other hybrid multilevel waveform generation topologies, classification and associated features, pertinent technical characteristics, relevant modulation and control schemes, common applications, and potential future applications and technological challenges. Specifically, recent developments and research in cascaded or series connected multilevel converters were covered by (Malinowski, 2017). The author describes the cascaded connection of the three major multilevel inverter topologies, and other hybrid topologies. Although many different topologies can be cascaded, a cascaded connection of full-bridge (H-bridge) modules in the

CHB converter and half-bridge modules in the modular multilevel converter (MMC) have proven to be the most popular option.

#### 2.2.1 Classic multilevel topologies

Generally, the most commonly used multilevel converter in high power and medium voltage applications is the neutral point clamped (NPC) converter and its spin-off topologies. An early paper by (Choi et al., 1991) proposed a general circuit topology for a neutral point clamped (diode-clamped) multilevel inverter. It was shown that, in a diode-clamped topology, the inner capacitors discharge quicker than the outer capacitors that are connected to the dc-link bus. Additional voltage balancing circuitry (e.g., a buck-boost converter) can be used to facilitate transfer of energy from the outer capacitors to the inner capacitors. Alternatively, this problem can be addressed by the replacement of the capacitors with controlled constant dc voltage sources or batteries as noted by (Lai and Peng, 1996). Another important feature of the NPC MLI includes a higher rating requirement for reverse voltage blocking which necessitates the use of medium/high (higher) voltage devices such as IGCT and IGBTs (Kouro et al., 2010). In contrast, the CHB topology may use low voltage devices like low voltage MOSFETs as proposed by (Chang et al., 2017). Additionally, NPC MLI suffers from unequal conduction duration for devices that dictates the requirement for different current ratings for switching devices, resulting in loss of modularity.

The flying capacitor MLI topology was introduced initially for high voltage dc-dc conversion (Rodriguez et al., 2002). Although the FC topology has a modular structure, it requires an increasing number of energy storage capacitors, in addition to the dc-link capacitor, as the number of output levels increases. In addition to the requirement for a high number of clamping capacitors, a complicated capacitor voltage balancing control strategy is required to mitigate the problem of the voltage imbalance. For instance, the control of a five-level FC converter is noted to be much more complex than that of a four-level FC inverter (Akagi, 2017). The flying capacitors also need to be pre-charged prior to operation. Another significant issue for the FC topology is the inverse relationship between the switching frequency and the required capacitor inverter at relatively higher switching frequencies leading to increased switching losses. Alternatively, larger capacitances are needed to operate at lower frequencies to achieve proper voltage balancing.

#### 2.2.2 Cascaded H-bridge topology

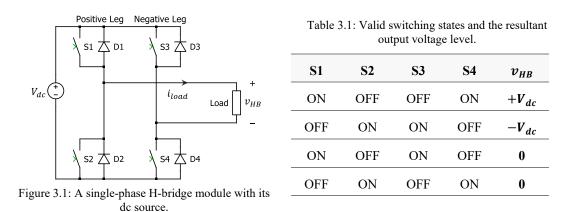

The cascaded H-bridge configuration is inherently well suited for use with multiple isolated dc sources. In the topology analysed in this thesis, the breakdown of the battery pack into separate smaller battery units can be used in conjunction with H-bridges to generate a multilevel waveform for the multiphase machine. This can be achieved by connecting each of the smaller battery unit to power each cell of the H-bridge inverter. Multiple phases can be generated by replicating the same structure to supply multiple phases of a multiphase machine.

Since a CHB-MLI is composed of multiple H-bridges, this leads to a reduction in manufacturing costs due to the modular design. A CHB structure intrinsically allows for the synthesis of a multilevel voltage waveform of higher ac voltage levels without having the issue of equal voltage sharing associated with series connected devices. Lower rated semiconductor devices can be used to form a modular structure which enables high voltage and high-power operation. A component requirement comparison between the three primary topologies (Lai and Peng, 1996) shows that CHB-MLI requires the least number of components from among the three primary MLI types for the same number of output levels. Furthermore, the structure of the CHB-MLI allows for a modular design with convenient packaging. And, as already mentioned, by virtue of having a multilevel structure of the output ac voltage, there is much lower dv/dt stress and total harmonic distortion. A high transistor count and respective gating drivers do raise cost and reliability concerns.

A cascaded multilevel voltage source inverter (VSI) with separate dc sources (using capacitors) was proposed by (Peng et al., 1996) for use as a static VAr generator for power transmission systems. The authors argued that, practically, a diode-clamped inverter was limited to 7 or 9 levels due to the substantial increase in the requirement of clamping diodes. Similarly, flying capacitor inverters were known to be plagued by problems such as: large capacitance requirement, complicated control, and higher switching frequency for balancing capacitor voltages. Therefore, a multilevel inverter based on the CHB topology was a suitable alternative. Features such as lower switching frequency, no requirement for voltage balancing circuits, simple layout and structure, and decreased component count were cited as advantages. Simulation and experimental verification confirmed the viability of the proposed cascaded inverter, its suitability for flexible ac transmission systems (FACTS)

applications and its potential for other applications requiring isolated dc sources such as electric vehicles with several battery modules.

In (Tolbert et al., 1999), the authors anticipated the use of CHB multilevel converters as a suitable option for automotive electric drives as they generate near-sinusoidal voltage waveforms with low switching frequencies and produce minimal electro-magnetic interference (EMI) and common mode voltages. For an all-electric vehicle, the authors built a compelling case for the use of a CHB- MLI since it requires the use of multiple dc voltage sources, which could be obtained from a set of batteries, fuel cells, or super-capacitors. Subsequently, (Tolbert et al., 2002) proposed the use of a CHB-MLI for automotive electric drives. The basic structure and mode of operation of a MLI based on the CHB topology was described, where operation at high and low modulation indices was considered.

The CHB topology can be realised with either equal or unequal dc voltages as noted earlier. A generalised structure of an asymmetric CHB-MLI is presented by (Corzine and Familiant, 2002) where multiple H-bridges are connected in series to form an H-bridge module using unequal dc sources. The number of voltage levels achievable by the cascaded H-bridge inverter are maximised by setting the dc voltages in a certain ratio. In this way, power quality can be significantly improved with the use of different dc voltages (asymmetric CHB). An asymmetrical configuration of the CHB is useful in minimizing inverter losses and improved efficiency in certain applications. However, it suffers from drawbacks from loss of structural modularity such as the requirement for devices and components of different ratings and different thermal solution for each H-bridge module. Furthermore, dc sources of identical values are preferred for voltage isolation. Therefore, the asymmetric CHB is unsuitable for EV applications, as proposed in this thesis.

#### 2.2.3 Hybrid multilevel topologies

Although not selected as a direct choice to be used in this thesis, due to mentioned complexity and non-modularity, it is worth stating that there are various other hybrid multilevel topologies. Some of these topologies are briefly reviewed in this subsection.

A dc-ac cascaded H-bridge multilevel boost inverter, without the use of inductors, for EV traction application was presented by (Du et al., 2009). The hybrid topology used a traditional three-phase two-level inverter where each leg of the inverter is connected in series

with an H-bridge using a capacitor as a dc power source. This type of converter is useful when high power is required by an EV motor; however, it requires several capacitors and a higher number of switches to realise. Similarly, an asymmetric CHB configuration (unequal dc sources) was proposed by (Tsang and Chan, 2014) with a three-phase multilevel inverter, using reduced number of switches, based on CHB topology with a single dc source and capacitors acting as the remaining dc sources. In this way, the requirement of multiple dc sources is mitigated and a better efficiency at nominal load compared to the standard two-level inverter is achieved. It was noted, however, that the voltage across the capacitors acting as dc sources, require proper regulation due to unequal current drawn from each capacitor. Additionally, since some of the inverter states do not support voltage regulation, larger capacitors were required to ensure acceptable voltage levels for inverter operation under these states.

Another MLI with a reduced component count was proposed by (Hota et al., 2017) where an optimised three-phase multilevel inverter topology is presented. This is achieved by splitting the inverter into a level generation part and a phase sequence generation part, which are cascaded together to form the MLI. In a symmetrical configuration, for a three-phase nine-level inverter output, the proposed topology requires 36 switches as compared to 48 for a conventional CHB-MLI. However, for the same number of output levels, the CHB-MLI requires only 12 voltage sources as compared to 14 required by the proposed topology. It is obvious that a reduction in the number of switches results in lower conduction and switching losses, but the requirement for a higher number of de sources is problematic.

A paper by (Lee et al., 2018) extends the work of (Hota et al., 2017) for reducing the switching count in multilevel inverters. They have achieved this by modifying the voltage level generating basic units by replacing the half-bridge submodules with a four-level submodule with six switches. The proposed topology achieves reduction in the number of dc sources required as compared to the topology presented by (Hota et al., 2017) for both the three-phase and single-phase inverter cases. The paper shows graphically the number of switches and dc sources required. The topology requires an equal number of dc sources as that of CHB-MLI and significantly reduces number of power switches. However, a significant disadvantage of this topology for high voltage applications, and that of (Hota et al., 2017), when compared to CHB-MLI is that the maximum blocking voltage required for

each switch is equal to the sum of all dc sources. This would require switches with a significantly higher voltage rating thus increasing the price. However, this would not be a problem for low voltage applications.

In recent years, new topologies have emerged such as the modular multilevel converter (MMC), active neutral point clamped, neutral point piloted converter, several multilevel matrix converter topologies, various hybrid multilevel topologies based on the CHB and NPC topologies, which have been presented in (Kouro et al., 2010). An example of such a hybrid topology is presented in an interesting work by (Samadaei et al., 2018). The authors have introduced a topology with a reduced number of switching components using a square T-type module – a modified version of an H-bridge configuration – for an asymmetrical (unequal dc sources) multilevel inverter, for use in high power applications. Two T-type connections, each with two unidirectional and two bidirectional switches, are joined to form a square module which was shown to generate up to 17 voltage levels with 12 switches and 4 unequal dc sources. However, the use of unequal dc sources would not be a practically suitable solution for EV application due to loss of modularity and increased complexity, as the system would require batteries of different capacities and sizes.

### 2.3 Multiphase machines and their control

A machine with more than three phases on the stator is commonly referred to as a multiphase machine. Both the induction and synchronous type machines can be designed with multiple phase windings. The phase shift of the supply voltages in that case should match the angular shift between the individual phases. Multiphase machines can be broadly demarcated into either those that have a prime number of phases or those that have an even number of phases or a composite odd number of phases. Since three-phase machines are prevalent and their control is generally well analysed and understood, multiphase machines with phase number equal to an integer multiple of three are preferred for various applications due to similarities in their construction and control. One such machine will be analysed in this thesis. Therefore, references related to the modelling, various advanced features of multiphase machines, and their control, are reviewed in this section.

#### 2.3.1 Modelling of multiphase machines

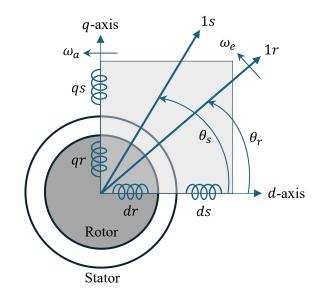

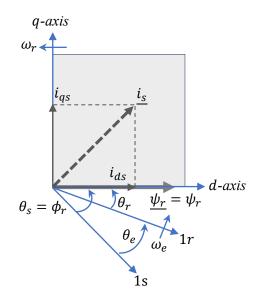

Multiphase machines can be modelled in the phase-variable domain using voltage equilibrium equations for the stator and the rotor windings, mechanical and torque equations, algebraic equations describing the relationship between the flux linkages and the machine currents, and the integral equation relating instantaneous rotor position with the angular electrical speed of rotation (Duran et al., 2017). In the case of a three-phase machine, transformation is carried out using the combined Clarke and Park transformation to obtain a model in a common reference frame rotating at an arbitrary angular speed. Similarly, multiphase machines may be described by transformation from a physical phase model into a dq model in the common reference frame using decoupling (or the vector space decomposition, VSD) and rotational transformation [(Zhao and Lipo, 1995); (Levi et al., 2007); (Rockhill and Lipo, 2009)]. Multiphase machine modelling has been covered in [(Levi, 2011a); (Duran et al., 2017); (Tessarolo, 2009); (Rockhill and Lipo, 2015)]. A simplified VSD transformation algorithm for any type of multiphase machine - symmetrical or asymmetrical - with a sinusoidally distributed magneto-motive force (MMF) was presented by (Zoric et al., 2017). A novel transformation technique was presented by (Rubino et al., 2021) for the modelling of a modular (multiple sets of three-phase stator windings) permanent magnet synchronous machine (PMSM) using a combination of the VSD transformation and the multiple d-q approach. This transformation allows for decoupled regulation and control of the torque developed by each of the winding sets of a modular multiphase machine.

#### 2.3.2 Features of multiphase machines

A prominent feature of multiphase machines is the reduction in power per phase as the current is distributed over a larger number of phases. The inversely proportional relationship between the number of machine phases and per-phase current allows for the use of lower rated semiconductor devices in the power electronic converter. Another feature relates to the improvement in the distribution of the MMF in the machine airgap resulting in lower torque pulsations.

A comprehensive review paper by (Levi, 2016) reveals various innovative uses of the extra degrees of freedom enabled by the use of multiphase machines. These extra degrees of freedom stem from the requirement of only two independent currents for flux and torque

control of a machine irrespective of the total number of phases. The remaining variables can be utilised for numerous other useful purposes. For instance, the torque and power density of a multiphase machine with a concentrated winding can be enhanced by the injection of specific current harmonics, making use of the additional degrees of freedom.

Another important feature is the application of the multiphase machines in integrated on-board battery chargers in EVs. The combination of propulsion and charging components provides a positive economic benefit. This is achieved using the propulsion machine stator winding as a filter and the inverter as a rectifier during EV charging mode. An onboard integrated three-phase battery charger for EVs using only components necessary for propulsion was presented by (Subotic et al., 2015). The neutral points of the three isolated three-phase windings of an asymmetrical nine-phase machine were connected to the threephase grid during the charging process with the current passing through a nine-phase halfbridge propulsion inverter operating as a rectifier to charge the EV batteries. The charging currents passing through each of the three-phase windings are equal and do not produce any flux or torque. The viability of the system in propulsion, charging and vehicle-to-grid (V2G) modes were investigated and confirmed. Similarly, a topology with the capability of operation both in propulsion mode and three-phase charging using the same powertrain components was presented by (Subotic et al., 2016) using a machine with a prime number of phases greater than three.

A key feature of multiphase drives is the fault tolerant capability. Fault tolerant operation is frequently a requirement in critical applications. Fault tolerant operation of a multiphase machine is made possible by the availability of additional degrees of freedom. Methodologies for the fault tolerant control of multiphase motor drives has been discussed in great detail by (Duran and Barrero, 2016). Different types of machine and inverter faults are surveyed, such as different open circuit and short circuit faults. Fault tolerant operation of a multiphase machine is achieved by the reconfiguration of the software upon fault detection and corrective post-fault control. A modification to the FOC scheme for post fault operation of the six-phase induction machine (IM) has been studied by (Che et al., 2014). Subsequently, it has been demonstrated that natural fault tolerance in a multiphase machine is possible through minimal adjustment to the FOC strategy through open-loop control of the x-y currents in case of open-phase fault conditions (Prieto et al., 2020). Although fault

tolerant operation of a multiphase machine is an important consideration for EVs, it is outside the scope of this thesis and will not be covered.

#### 2.3.3 Control of multiphase machines

Ever growing industrial automation is primarily responsible for a continuous increase in the number of variable speed applications, and, as a consequence, an increase in the requirement for high performance applications such as robotics, machine tools, spindles, rolling mills, elevators. Multiphase machines, in particular, have found applications in high power compressors, electric ship propulsion, more-electric aircrafts, extruder pumps, high speed elevators, traction systems, electrical vehicles, and energy conversion systems (Levi, 2008).

The control system of a machine generally consists of an outer speed control loop, with a controller, generally of the proportional-integral (PI) type. The output of the speed controller is generally a reference current signal which is fed to the inner current control loop. The inner control can be realised using various control strategies. A common control technique employed in the industry for the control of ac machines is the open loop v/f control. This normally suffices for simple applications, but the dynamic speed and torque response is poor and consequently unsuitable for high performance variable-speed applications.

High performance applications require rapid, almost instantaneous, response from the motor in terms of acceleration, deceleration, and speed reversals and quick start/stop routines, all under abrupt variations in torque. Two popular high performance control methods are the direct torque control (DTC) and field-oriented control (FOC). DTC offers a fast dynamic response and low computational complexity due to simple implementation. An example of DTC scheme for EV application was presented by (Khoucha et al., 2010) where an asymmetrical CHB inverter was used to control a three-phase induction motor. However, implementation of direct torque control is rather challenging when it comes to control of multiphase drives. Additionally, DTC suffers from issues such as variable switching frequency, larger torque and current ripples, difficult control at low speed.

Field-oriented control of multiphase ac machines is prevalent and can be achieved in different ways but the most commonly used is the rotor flux-oriented control (RFOC)

methodology, which is covered in depth by (Levi, 2011b). The rotor flux-oriented control entails the use of inner current control loops and an outer speed control loop. A modified version of the RFOC scheme for the control of a five-phase induction motor drive (with sinusoidal magneto-motive force, MMF) is presented by (Jones et al., 2009). It shows that n-1 current controllers are required for the control of an n-phase drive to account for the low order current harmonics present due to inherent asymmetries and inverter dead time. Indirect RFOC is normally used, and various synchronization methods are applied to avoid the misalignment between the controller reference and motor reference coordinate systems. The misalignment would result in the loss of efficiency because of loss of torque and flux decoupling (Levi, 2011b).

With regard to the FOC in multilevel multiphase drives, most papers are focused on the neutral point clamped (NPC) three-level converter (Levi, 2016). For example, an FOC of a six-phase permanent magnet synchronous machine (PMSM) drive using a three-level NPC, based on space vector modulation (SVM) was presented by (Wang et al., 2016). FOC of other multilevel multiphase drives include an FOC of a fifteen-phase concentrated tooth winded PMSM (Gliese et al., 2022). Here each stator phase winding was connected to a single H-bridge module resulting in a three-level output voltage. A similar solution was suggested by (Bayati et al., 2023) but instead a reconfigurable battery is used. Each phase of a nine-phase IM was supplied by individual H-bridge modules and battery charging capability was demonstrated. In (Zaidi et al., 2019) a simulation comparison has been made between the performance of the sliding mode controller and the standard PI-based speed control of a multiphase drive with a hybrid cascaded multilevel converter with FOC applied separately to each three-phase winding set, with no x-y current control considered.

Limited literature is available on the combination of a CHB converter and a multiphase machine. An early study of a multilevel multiphase space vector pulse width modulation (PWM) of a five-level CHB converter was presented in (López et al., 2008) but an RL load was used. A simulation study showing a closed-loop v/f control of a five-phase IM drive based on a five-level CHB inverter under bipolar modulation for different load torque conditions was presented by (Rahman et al., 2019). A comprehensive study of the post fault operation of a medium voltage multiphase drive based on a CHB with a software-based x-y component voltage injection, for maximizing the dc-link voltage utilization in case of a bypassed H-bridge module, was presented in (López et al., 2024). However, none of these

papers are using FOC. On the other hand, FOC of a six-phase PMSM drive based on a five-level CHB converter was investigated for an electric aircraft powertrain in (Tedeschini et al., 2021), but the study was restricted to simulation only.

Other control methods include predictive torque control (PTC) and methods based on artificial neural networks, and other modified forms of v/f control methods. For example, the viability of predictive torque control application for the propulsion of an EV using a fivephase induction machine was established by (Riveros et al., 2010). Similarly, other alternatives using predictive current control have been proposed, as detailed in the survey by (Barrero and Duran, 2016), where inner current controllers are implemented using model predictive control (MPC) instead of classic PI controllers. MPC-based current control methodology requires no tuning for different operating points and features better dynamic performance as compared to PI controllers. However, PI controllers perform better in steadystate with a significantly smaller computational cost due to the presence of current components in non-torque/flux producing sub-planes in multiphase machines (Lim et al., 2014). Additionally, the computation cost of MPC increases with the number of output voltage levels. The reduction of computation cost of MPC has been addressed; for instance, a model predictive control method for a three-phase cascaded H-bridge multilevel converter was presented by (Chan et al., 2017) for fast dynamic applications with a reduced computation load compared to the standard MPC. Similarly for multiphase machines, efforts have been put in to achieve better quality and improved efficiency through the use of virtual voltage vectors in the finite control set model predictive control (Gonzalez-Prieto et al., 2018) or through the dynamic selection of appropriate voltage vectors due to switching stateredundancies under certain constraints (González-Prieto et al., 2019). However, these studies have been conducted for two-level multiphase converters and the implementation of model predictive control is quite challenging for multilevel multiphase systems.

Since it is an industry standard and is easily expandable to multiphase drives, rotor flux-oriented control will be used for the machine control in this thesis. Simplicity of vector control implementation will leave the microcontroller resources for implementation of other more complex algorithms related to battery monitoring, SoC and voltage balancing, etc.

#### 2.4 Modulation methods

MPC and DTC do not require a modulation stage as gating signals for the inverter switches are directly created. But a modulation stage is needed for the implementation of scalar or field-oriented control. The inner-most control entails the generation of gating pulses with a modulator for the inverter switches to produce the inverter output voltage waveform.

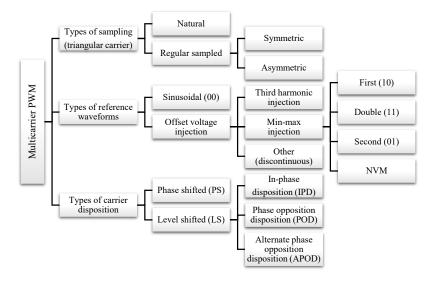

Various modulation and control strategies have been devised for multilevel inverters, and they can be classified based on the switching frequency. For low/fundamental switching frequencies, the multilevel selective harmonic elimination (SHE) and nearest level modulation (NLM) are the primary modulation methods. For high switching frequencies, the classic carrier-based sinusoidal PWM including the phase- and level-shifted multicarrier PWM along with the space vector PWM (SV-PWM) are typically the preferred modulation methods (Franquelo et al., 2008). Although SV-PWM allows exploitation of additional degrees of freedom for several useful purposes, it generally requires more complex calculations as the number of levels and the number of phases increase. It is also preferable to use modulation methods which minimise switching losses by reducing the switching frequencies for high power applications. High dynamic range applications requiring enhanced output power quality are better served by a higher switching frequency algorithm [(Abu-Rub et al., 2010); (Kouro et al., 2010)].

The complexity of modulation methods usually increases with an increase in the number of the converter levels. Also, different modulation methods can significantly affect the losses of the converter, which is of considerable importance in battery powered EVs. Hence, various multilevel converter modulation methods are reviewed next.

#### 2.4.1 Phase-shifted (PS) PWM

The standard phase-shifted carrier-based PWM (PS-PWM) is the modulation method of choice for industrial applications. The multicarrier phase-shifted PWM is an intrinsically suitable methodology for a CHB-MLI due to the modular structure of the topology (Townsend et al., 2015). Phase-shifted carrier-based PWM works by comparison of several phase-shifted carrier waveforms with a reference (modulating) signal to produce appropriate switching signals. An analytical solution of the carrier-based PWM was used by (Holmes and McGrath, 2001) to identify the opportunities for harmonic cancellation in carrier-based PWM. The authors established the ideal phase shift required between the carrier waveforms to achieve best harmonic cancellation within each phase-leg of a cascaded MLI. For a cascade connection of k full-bridge modules, phase-shifted carrier signals with a phase shift angle of  $180^{\circ}/k$  are required.

A major advantage of PS-PWM is that it shifts the spectrum to a higher frequency which can be filtered out using smaller filters. Moreover, PS-PWM features the equal distribution of power among all the CHB modules, equal losses between the devices within a module, and between different modules within a certain phase (Kouro et al., 2010). For these reasons, this modulation strategy finds use in most commercial applications of CHB based multilevel converters. The PS-PWM does produce some slight unwanted voltage distortion at the inverter output due to the phase-shift between different carriers (McGrath and Holmes, 2002). In the case of slight imbalances between dc-link voltages of different CHB modules, which is quite likely, increased lower order harmonic distortion is seen in the synthesised voltage waveform of CHB-MLI operating under PS-PWM. This could be reduced by making use of variable-shift angle PS-PWM as shown by (Marquez et al., 2017) but at the cost of increased complexity, especially for a higher number of CHBs.

#### 2.4.2 Level-shifted (LS) PWM

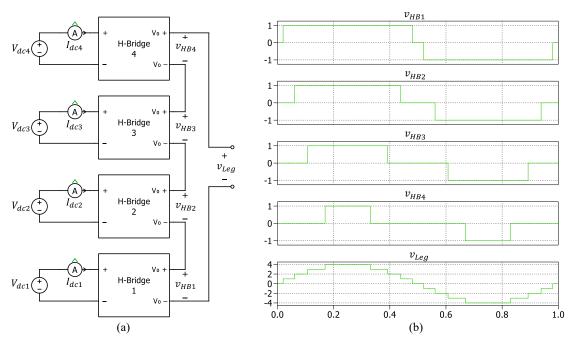

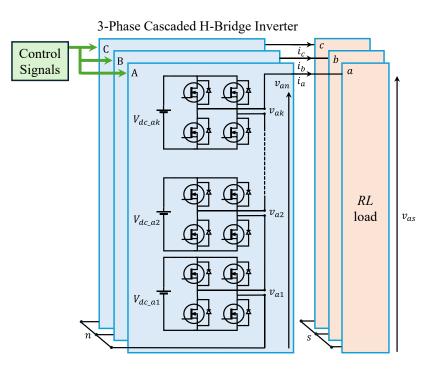

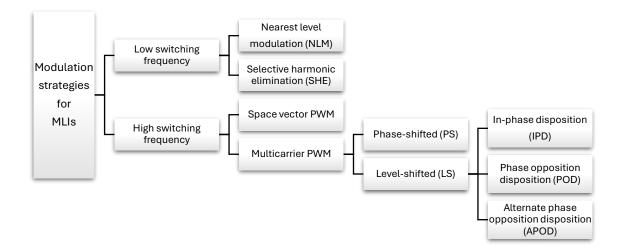

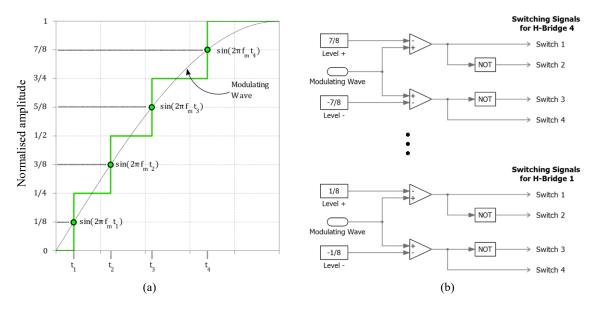

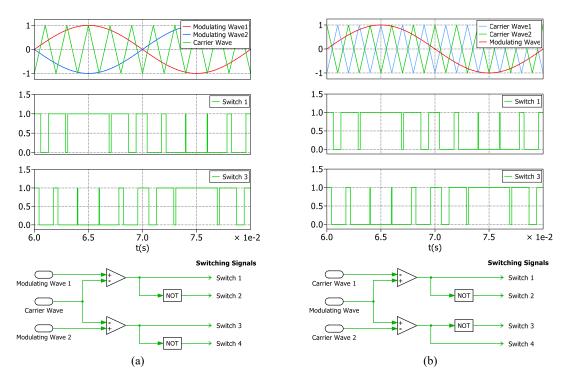

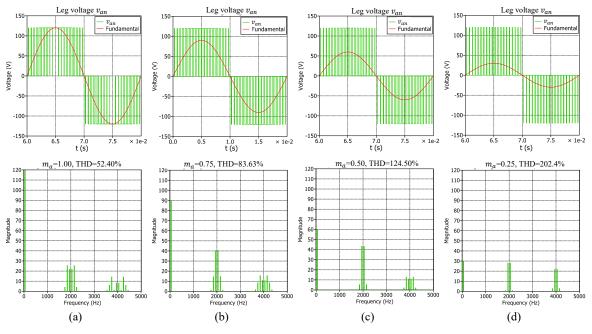

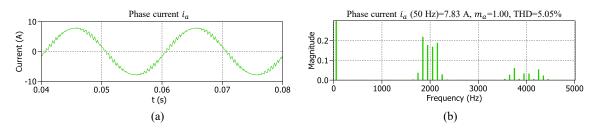

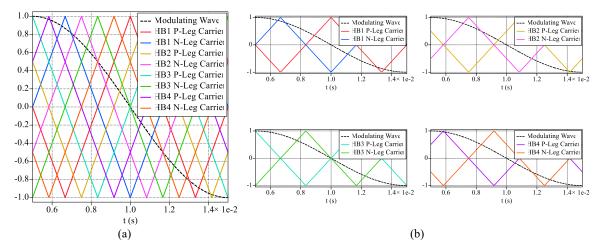

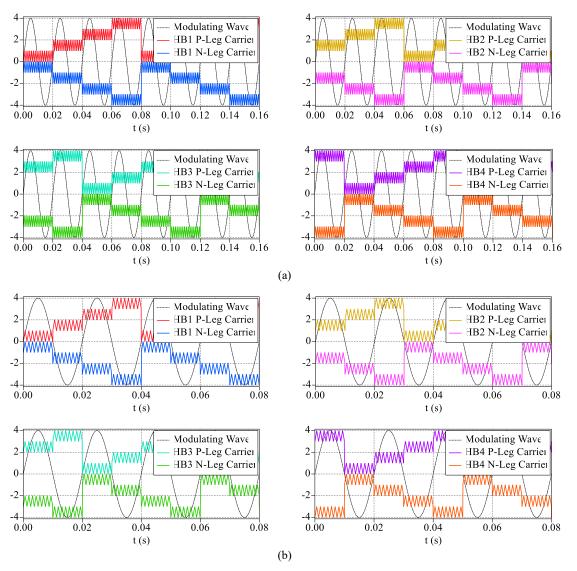

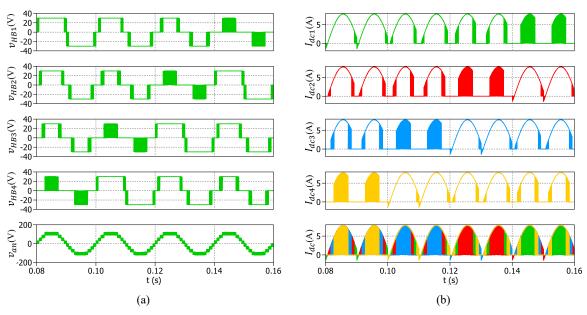

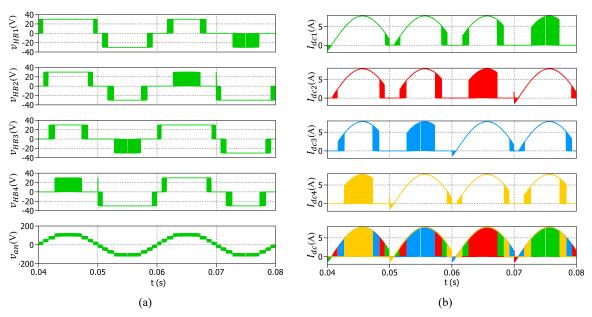

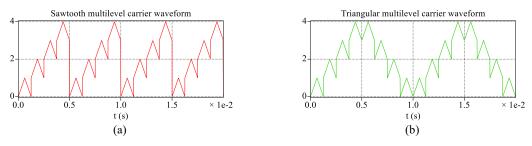

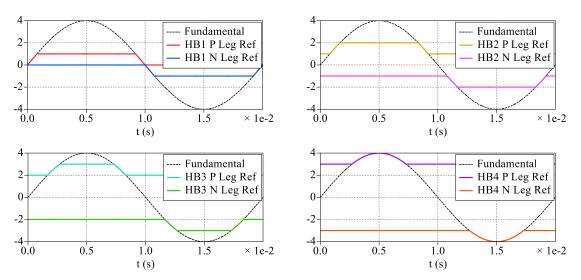

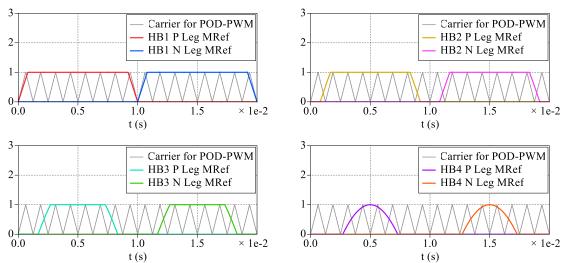

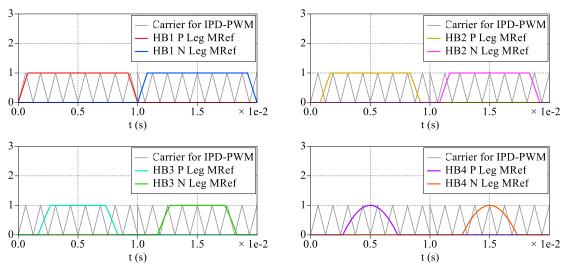

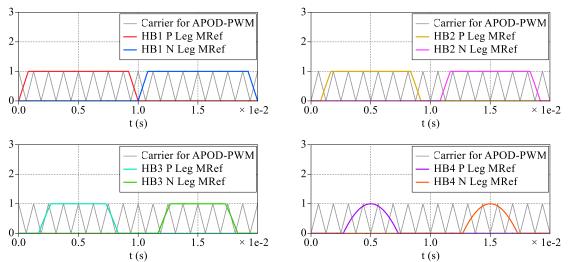

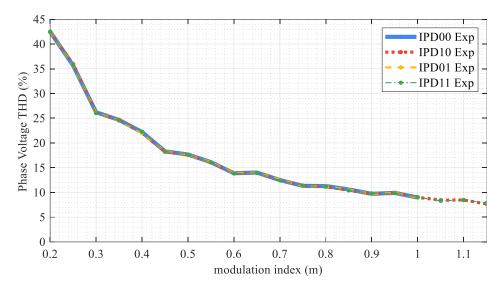

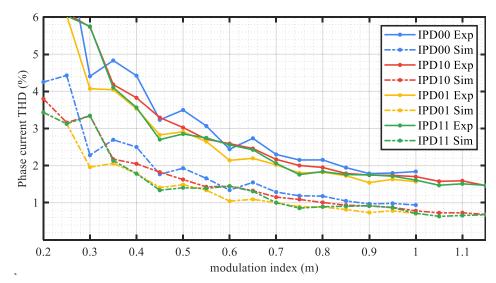

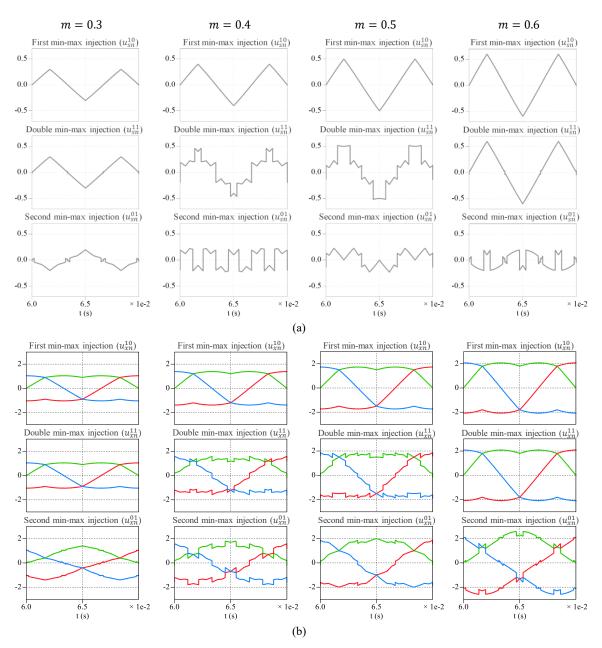

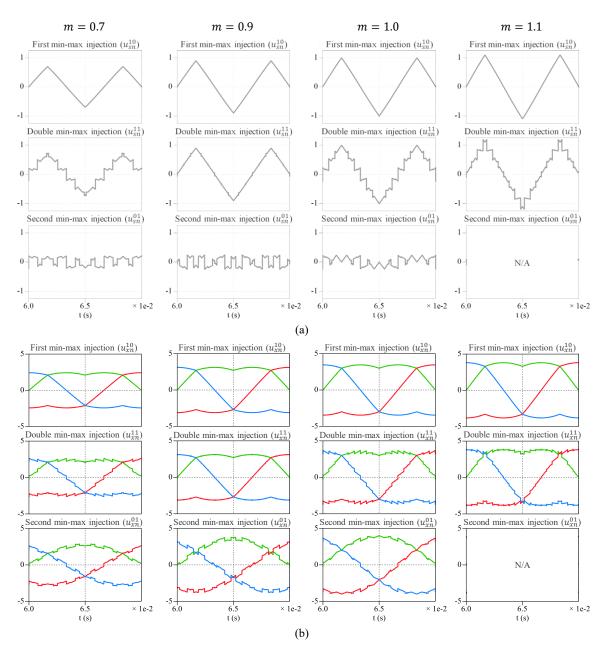

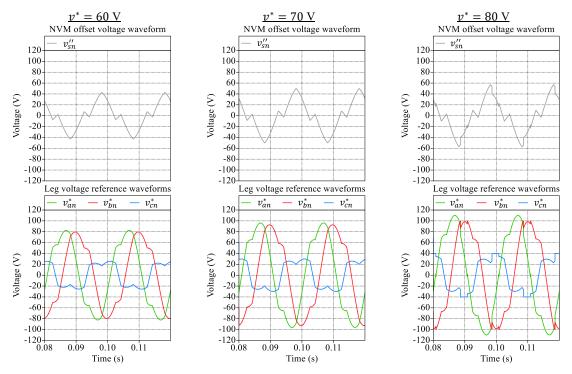

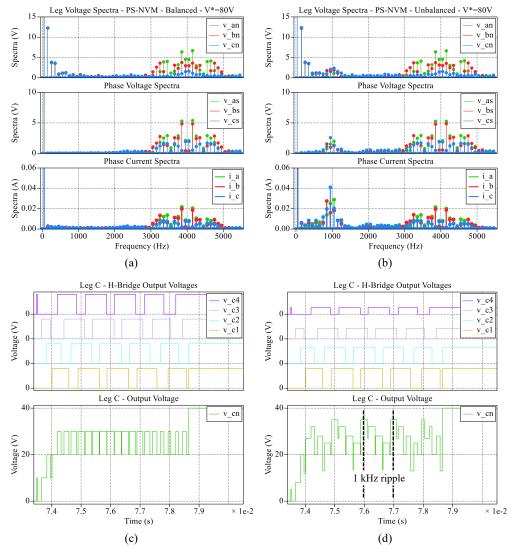

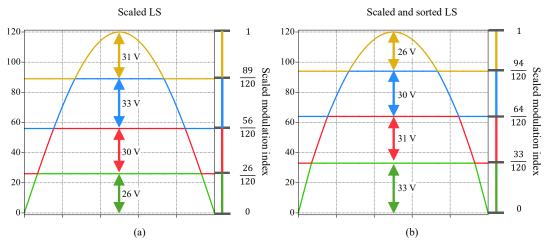

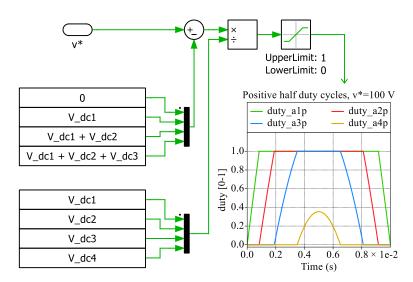

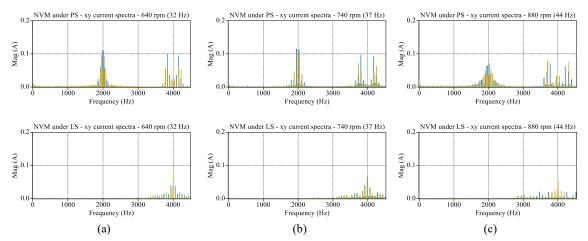

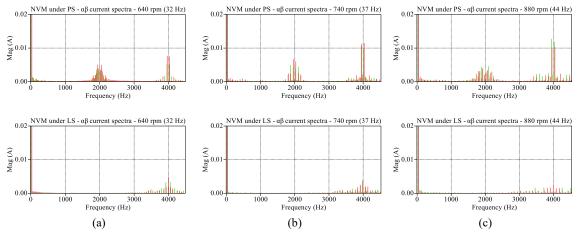

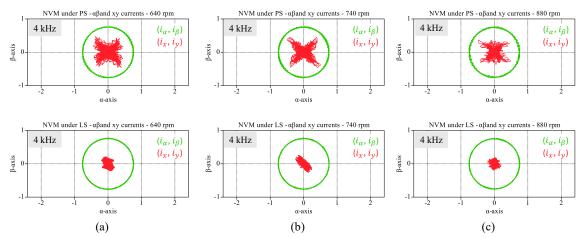

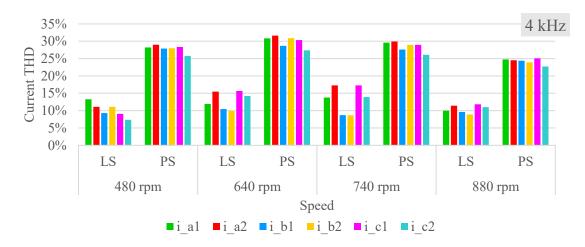

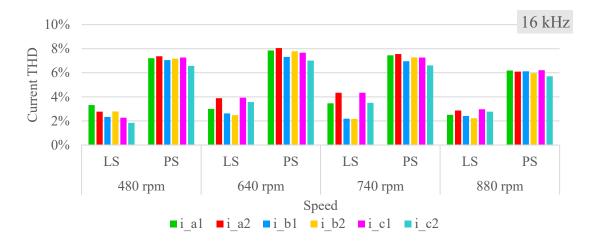

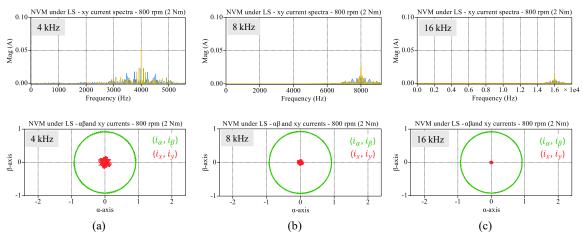

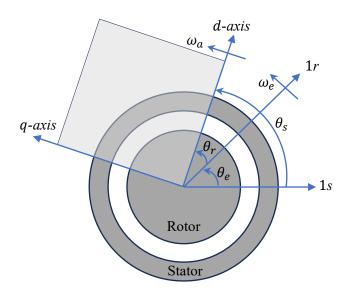

The other popular PWM methodology is the level-shifted PWM (LS-PWM), also sometimes referred to as the phase-disposition PWM, and it has several variants depending on the phase difference between each of the carrier signals (Carrara et al., 1990). In the case of a level-shifted PWM scheme known as the in-phase disposition (IPD) or simply phase disposition (PD) PWM, multiple carrier signals of the same frequency, phase, and amplitude — but vertically shifted — are compared with a modulating reference to produce a multilevel phase voltage waveform. For the phase-opposition disposition (POD), the carriers above the zero reference are in phase-opposition with those below the zero reference. Finally, for the alternative phase-opposition disposition (APOD), adjacent carriers are in phase-opposition. It has been noted (McGrath and Holmes, 2002) that the THD for the line-to-line voltages is better for the level-shifted modulation scheme as compared to the phase-shifted modulation technique. However, the level-shifted modulation methods cause an uneven distribution of device conduction times and causes unbalanced power distribution among CHB modules (Rodriguez et al., 2007). This causes a variation in the switching frequency of different devices in different H-bridge cells. Hence, there is a need to ensure that the switching pattern cyclically rotates between different H-bridge cells in order to provide balanced device switching and conduction times, which adds to the complexity of the scheme.