# Device and Circuit Performance of the Future Hybrid III-V and Ge based CMOS Technology

Brahim Benbakhti, Kah Hou Chan, Ali Soltani and Karol Kalna, Senior Member, IEEE

Abstract—The device and circuit performance of a 20 nm gate length InGaAs and Ge hybrid CMOS based on an implant free quantum well (QW) device architecture is studied using a multiscale approach combining ensemble Monte Carlo simulation, drift-diffusion simulation, compact modelling, and TCAD mixed-mode circuit simulation. We have found that the QW and doped substrate, used in the hybrid CMOS, help to reduce short channel effects by enhancing carrier confinement. The QW also reduces the destructive impact of a low density of states (DoS) in III-V materials. In addition, the calculated access resistance is found to be a much lower than in Si counterparts thanks to a heavily doped overgrowth source/drain contact. We predict an overall low gate capacitance and a large drive current when compared to Si-CMOS that leads to a significant reduction in a circuit propagation time delay (~5.5 ps).

*Index Terms*—III-V, Ge, CMOS, Monte Carlo, drift-diffusion, compact modeling, TCAD.

#### I. Introduction

Lternative channel materials to improve CMOS performance is a rapidly growing area of research [1][2]. III-V and Ge based CMOS offers attractive possibilities for a high performance and a low power circuit implementation [3]. In addition, this device can be manufactured onto the existing Si substrate technology, allowing co-integration with conventional Si-CMOS. A high electron mobility and a low effective mass in III-V materials result in a very high injection velocity and a low back-scattering promising a high device performance and a large switching speed at a low supply voltage [4][5]. On the other hand, the investigation of Ge as an alternative channel material and a potential technology booster has experienced a revived impetus, especially for p-channel MOSFETs [6][7], where a higher carrier mobility and drive current compared to conventional Si devices have already been successfully demonstrated [8].

The high mobility and the high injection velocity of III-V and Ge materials require transistor architectures which can be readily incorporated into Si CMOS technology while

Manuscript received MMM DDD, 2016. The review of this paper was arranged by Editor XXX.

- B. Benbakhti was with School of Engineering, University of Glasgow, Glasgow, G12 8LT, U.K. He is now with the School of Engineering, Liverpool John Moores University, Liverpool, L3 3AF, U.K. (e-mail:b.benbakhti@ljmu.ac.uk).

- K. H. Chan is with School of Engineering, University of Glasgow, Glasgow G12 8LT, U.K.

- A. Soltani is with IEMN, Université de Lille 1, 59650 Villeneuve d'Ascq, France. He is also with LN2, Université de Sherbrooke, 3000 boul. de l'Université, J1K 0A5 Sherbrooke, Canada

- K. Kalna is with Electronics Systems Design Centre, College of Engineering, Swansea University, Bay Campus, Swansea, SA1 8EN, U.K.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier xx.xxxx/TED.2016.xxxxxxx

simultaneously neutralizing some of detrimental effects of low density of states (DoS) [9]. The implant free quantum well (IFQW) device structure [10][11] offers such attractive technological and performance advantages. The IFQW has a better scalability, lower sensitivity to  $D_{\rm it}$  in the tails compared to other MOSFET architectures [11], and is highly resistant to the band-to-band tunnelling (BTBT) since it is free of heavily doped source/drain (S/D) regions [12]. Combined variability simulations including random discrete dopants (RDD), line edge roughness and metal gate granularity have shown that IFQW-CMOS has a better immunity to threshold voltage ( $V_{\rm th}$ ) variability than equivalent bulk Si MOSFETs [13].

In this work, we report on the device and circuit performance of the IFQW-CMOS that is based on nIFQW III-V and pIFQW Ge device architectures using a multi-scale modelling approach by hierarchy of ensemble Monte Carlo (MC) simulation, drift-diffusion (DD) simulation, compact modelling, and TCAD mixed-mode circuit simulation techniques. The IFQW-CMOS architecture is summarised in Section II, while Sections III and IV outline the simulation methodology and device/circuit performance together with macroscopic parameters extraction. Conclusions are drawn in Section V.

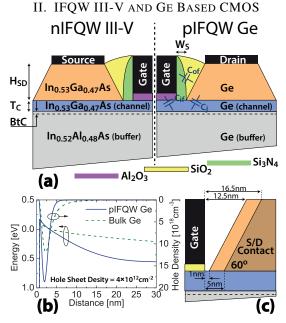

Fig. 1. (a) Cross-sections of IFQW-CMOS made of implant free quantum well device (IFQW) architectures (nIFQW III-V and pIFQW Ge). The doping concentration is low in a channel ( $T_C$ ) and a buffer-to-channel (BtC) layer indicated by a dash line and is high in the rest of a buffer. (b) Valence band energy and hole density profiles across the middle of the gate for pIFQW Ge and bulk Ge MOSFETs for comparison. (c) Geometry of a tilted S/D contact that helps to reduce the effect of outer fringing capacitance ( $C_{nf}$ ).

| TABLE I                                                |

|--------------------------------------------------------|

| DIMENSIONS AND DOPING CONCENTRATIONS OF THE IFQW-CMOS. |

|                                                             | n <b>IFQW III-V</b>    | p <b>IFQW</b> Ge        |  |  |  |  |  |

|-------------------------------------------------------------|------------------------|-------------------------|--|--|--|--|--|

| Dimensions [nm]                                             |                        |                         |  |  |  |  |  |

| Gate length (Lg)                                            | 20.0                   | 20.0                    |  |  |  |  |  |

| Lateral spacer width (W <sub>S</sub> )                      | 1.0 or 5.0             | 1.0 or 5.0              |  |  |  |  |  |

| S/D height (H <sub>SD</sub> )                               | 20.0                   | 20.0                    |  |  |  |  |  |

| S/D length                                                  | 45.0                   | 45.0                    |  |  |  |  |  |

| Gate dielectric                                             | 1.6                    | 1.6                     |  |  |  |  |  |

| Channel thickness (T <sub>C</sub> )                         | 5.0                    | 5.0                     |  |  |  |  |  |

| Buffer-to-Channel (BtC)                                     | 1.0                    | 1.0                     |  |  |  |  |  |

| EOT                                                         | 0.7                    | 0.7                     |  |  |  |  |  |

| Doping Concentrations [×10 <sup>17</sup> cm <sup>-3</sup> ] |                        |                         |  |  |  |  |  |

| Background                                                  | 1.0 ( <i>p</i> -type)  | 1.0 ( <i>n</i> -type)   |  |  |  |  |  |

| Buffer                                                      | 20.0 ( <i>p</i> -type) | 20.0 (n-type)           |  |  |  |  |  |

| S/D Contacts                                                | 500.0 (n-type)         | 500.0 ( <i>p</i> -type) |  |  |  |  |  |

The cross section of the IFQW-CMOS is illustrated in Fig. 1a. The nIFQW III-V part consists of In<sub>0.52</sub>Al<sub>0.48</sub>As buffer, 5 nm thick In<sub>0.53</sub>Ga<sub>0.47</sub>As channel, 1 or 5 nm Si<sub>3</sub>N<sub>4</sub> lateral spacer width  $(W_S)$ . The p-type buffer is uniformly doped to  $2\times10^{18}$ cm<sup>-3</sup> to reduce leakage current. At 1 nm below the channel, the p-type buffer doping concentration is reduced to  $1 \times 10^{17} \text{cm}^{-3}$  (background doping) and remains low in the channel. The raised S/D contacts are uniformly n-type doped to  $5\times10^{19}$  cm<sup>-3</sup>. The pIFQW Ge structure is similar to the nIFQW III-V with highly p-type doped  $(5\times10^{19} \text{cm}^{-3})$  Ge S/D contact, a 5 nm Ge channel. The QW of the pIFQW Ge is created by having a low n-type doping concentration in the channel and in the buffer till 1 nm below the channel. At the 1 nm below the channel till the rest of the buffer (see Fig. 1b), ntype doping is a much larger  $(2 \times 10^{18} \text{cm}^{-3})$ . A common gate stack is used for the both n and pIFQWs with 1.6 nm  $Al_2O_3$ dielectric layer giving an equivalent oxide thickness (EOT) of 0.7 nm. As a requirement for the CMOS co-integration, a dual metal work function of 4.6 eV and 4.2 eV is used for n and pIFQW, respectively [14], [15]. All devices have raised contact regions angled at 60°. Only a small degradation (<5%) in the drive current has been observed for the  $60^{\circ}$ S/D contacts in respect to the vertically raised contacts [16]. The dimensions and doping concentrations of both devices are optimised using DD simulations [17] whilst accounting for technological limitations as summarised in Table I.

### III. SIMULATION METHODOLOGY

In this study, we have employed a set of device simulation techniques:

- Ensemble 2D finite-element MC device simulator in order to realistically predict supra-threshold characteristics (drive currents) of the IFQW-CMOS.

- For sub-threshold characteristics, 2D DD simulations calibrated against the MC data are used to assess device electrostatic like the subthreshold slope (SS) and the drain induced barrier lowering (DIBL). This is because MC simulations require extremely long runs due to inaccurate resolution of small currents. The DD calibration process consists on adjusting the I<sub>D</sub>-V<sub>G</sub> characteristics at low and high drain voltages via a physically based mobility

model. The low drain voltage  $I_{\rm D}\text{-}V_{\rm G}$  characteristics are used to adjust a low-field mobility (accounting for phonon scattering and impurity scattering) while a high-field mobility is tuned via a saturation velocity and a critical field to the high drain voltage  $I_{\rm D}\text{-}V_{\rm G}$  characteristics.

- An industry standard compact model (PSP) is used to match the DD results and to extract the DC and AC macroscopic parameters such as gate capacitances, short channel effects, access resistances,...etc. The PSP calibration starts by adjusting the device electrostatics to match the SS and DIBL parameters from the DD. A twostage compact model calibration and parameter extraction strategy have been employed [18].

- Finally, a full mixed-mode TCAD simulation is used to calculate the circuit propagation time delay in an inverter based on the IFQW-CMOS.

In this hierarchy of simulation techniques, the 2D MC device simulations, including quantum corrections and Fermi-Dirac statistics, employed for III-V and Ge IFQW transistors have well-recognised performance predictive power [12][19]-[22]. In the past, the III-V MC device simulator has been validated against measured I-V characteristics of a 120 nm gate length In<sub>0.2</sub>Ga<sub>0.8</sub>As pseudomorphic [20], lattice matched metamorphic HEMTs [23], and a 50 nm gate length In<sub>0.7</sub>Ga<sub>0.3</sub>As/InP HEMT [24]. The details on the III-V MC simulator can be found in [4], [12], [20]. The Ge MC device simulator employs a 6-band kop full-band structure including Fermi-Dirac statistics [25]. Optical and acoustic phonon scatterings of holes are compared against the experimental velocity-field characteristics for relaxed, bulk Ge demonstrating a good agreement [22]. Moreover, these two MC simulation tools have been adapted to deal with the IFQW with a new treatment required for the raised S/D contacts to accurately model carrier injection velocity [12][21].

#### IV. DEVICE AND CIRCUIT PERFORMANCE

In order to get a good estimation of device and circuit performance of the IFQW-CMOS at the end of the roadmap, we have selected two different  $W_{\rm S}$  in the devices (1 nm and 5 nm). Ensemble MC simulations are thus ideal to predict drive currents, while the DD technique is employed to simulate the sub-threshold currents. The latest helps to better understand the benefit of the good IFQW electrostatic integrity which can counterbalance the problem of low DoS and dark space (DS) in III-V materials.

# A. I<sub>D</sub>-V<sub>G</sub> Characteristics

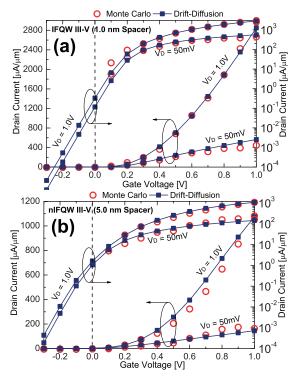

The  $I_D$ - $V_G$  characteristics obtained from the MC and calibrated DD simulations of nIFQW III-V and pIFQW Ge are shown in Figs. 2 and 3, respectively. For the nIFQW III-V, there is an increase in the drive current from  $\sim 1000$   $\mu A/\mu m$  to  $\sim 3000$   $\mu A/\mu m$  when  $W_S$  is reduced from 5 nm to 1 nm. A quantum confinement modulated potential barrier in the channel below the lateral spacer at the source side increases back-scattering rate for thicker lateral spacers ( $\sim 5$  nm). As a result, the carrier concentration in this channel reduces which, consequently, limits the drive current [26].

Fig. 2.  $I_D$ - $V_G$  characteristics of the nIFQW III-V at  $V_D=50$  mV and  $V_D=1$  V. DD simulations have been calibrated against MC results. (a) Lateral spacer width  $W_S$ =1 nm (SS=71.0 mV/Dec, DIBL=35.0 mV/V,  $I_{OFF}$ =0.1  $\mu$ A/ $\mu$ m) and (b)  $W_S$ =5 nm (SS=76.0 mV/Dec, DIBL=27.0 mV/V,  $I_{OFF}$ =1  $\mu$ A/ $\mu$ m).

For the pIFQW Ge, the drive current increases from  $\sim 500$  $\mu A/\mu m$  to  $\sim 1300 \ \mu A/\mu m$  when W<sub>S</sub> is reduced from 5 nm to 1 nm. The calibrated DD simulations indicate that W<sub>S</sub> has relatively a small impact on electrostatic integrity (SS and DIBL) for both nIFQW III-V and pIFQW Ge devices.  $I_{OFF}$ values of the nIFQW III-V are about two orders of magnitude higher than of the pIFQW Ge. This is the consequence of a larger leakage in III-V materials, which is related to the low DoS. The DIBL and SS are smaller than those of the 18 nm gate length Si or the 24 nm gate length FDSOI counterparts [30], [31], [32] but comparable to those of the 16-28 nm gate length SOI FinFETs by the 14 nm technology [33]. The DD simulations are then used to generate continuous output I<sub>D</sub>-V<sub>D</sub> characteristics (not shown) needed for macroscopic parameters extraction for the IFQW-CMOS. The latest are vital information for the overall performance predictions of IFQW-CMOS at short gate lengths.

# B. Gate Capacitances

The gate capacitance ( $C_G$ ) and its different components (dynamic charge distributions) are central parameters in determining the circuit performance of nano-transistors. In this context, we have used an industry standard compact models (PSP) to extract the AC behaviour of the IFQW-CMOS. The PSP has attracted significant attention because of its capability for a good physical description of device characteristics, especially for advanced technology nodes [27].

In this section, we have first calibrated the PSP models against the DD simulated characteristics ( $I_D$ - $V_G$  and  $I_D$ -

Fig. 3.  $I_D$ - $V_G$  characteristics of the pIFQW Ge biased at  $V_D=-50$  mV and  $V_D=-1$  V. The DD simulations have been calibrated against MC results. (a) Lateral spacer width  $W_S=1$  nm (SS=91.0 mV/Dec, DIBL=74.0 mV/V,  $I_{OFF}=4.5\times10^{-3}~\mu\text{A}/\mu\text{m}$ ) and (b)  $W_S=5$  nm (SS=95.0 mV/Dec, DIBL=65.0 mV/V,  $I_{OFF}=5.1\times10^{-3}~\mu\text{A}/\mu\text{m}$ ).

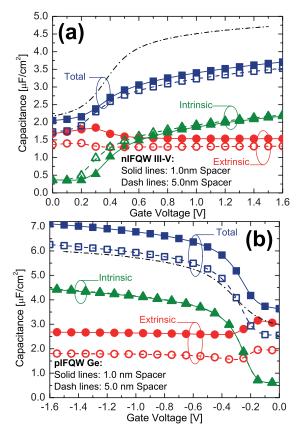

$V_{\rm D}$ ). Then, we have employed the split CV method [28] to distinguish the extrinsic gate capacitance (C<sub>GEXT</sub>) from the intrinsic gate capacitance ( $C_{\rm GINT}$ ).  $C_{\rm GEXT}$  includes both inner and outer fringe capacitances as shown in Fig. 1a. In contrast to the conventional MOSFETs with implanted S/D junctions, C<sub>GEXT</sub> of the IFQW does not include the overlap capacitance:  $C_G = C_{GINT} + C_{GEXT}$ . In the first order, the gate-to-channel capacitance is proportional to the metallurgical gate length (L<sub>g</sub>) but C<sub>GEXT</sub> remains virtually constant. Varying L<sub>g</sub>, which will not change C<sub>GEXT</sub> contribution, the intrinsic gate-tochannel capacitance can be extracted. Different devices were simulated at a single frequency 1 MHz at each DC bias during a sweep of V<sub>G</sub> performed in the AC simulation analysis. Results for gate lengths of 100 nm and 200 nm were used to cross-check accuracy of the results for the 20 nm gate length devices investigated here, although those are not shown here.

Fig. 4 compares the total, intrinsic and extrinsic capacitances versus the gate voltage ( $V_{\rm G}$ ) for the nIFQW III-V and pIFQW Ge ( $W_{\rm S}{=}1$  nm and  $W_{\rm S}{=}5$  nm), respectively.  $W_{\rm S}$  has a relatively small impact on  $C_{\rm GEXT}$ . This can be explained by geometrical shape of the S/D, particularly the large horizontal distance between the top of metal-gate and the S/D contact that reduces the effect of the outer fringing capacitance. Fig. 1c illustrates that at the bottom of the S/D contact, a relative difference between the 1 nm and 5 nm  $W_{\rm S}$  devices is 80 % while it is just 24 % at the top. Note that shrinking  $W_{\rm S}$  leads to lowering potential barrier in the channel and, consequently, to lowering of the inner fringing capacitance.

Fig. 4. Capacitance-voltage characteristics per unit area  $(L_g \times W_g)$  of the IFQW-CMOS: (a) nIFQW III-V and (b) pIFQW Ge. The "dash dot" lines represent the  $C_G$  of the 18 nm gate length bulk Si devices (pMOSFET and nMOSFET).

The gate capacitance of the pIFQW Ge is larger than that of the nIFQW III-V. This difference can be explained by a low inversion layer capacitance in the  $In_{0.53}Ga_{0.47}As$  channel due to a combination of low DoS and a larger equivalent gate dielectric thickness in inversion ( $T_{\rm INV}$ ). Note that the quantum capacitance is proportional to the DoS of channel material [29]. The overall  $C_{\rm G}$  of the nIFQW transistor is lower than that of the 18 nm gate length Si counterpart [30][31]. However, the  $C_{\rm G}$  of pIFQW transistor is comparable to that of the Si devices.

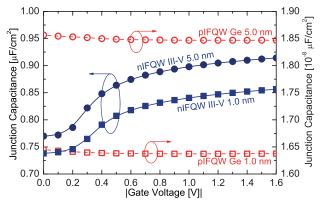

Fig. 5. Junction capacitance per unit area ( $L_g \times W_g$ ) versus  $V_G$  of the 20 nm gate length IFQW-CMOS (nIFQW III-V and pIFQW Ge) for a lateral spacer width  $W_S{=}5$  nm (circle symbols) and  $W_S{=}1$  nm (square symbols).

Junction capacitances that originate from the p-n junctions formed by the S/D contacts to the channel depletion region (as illustrated in Fig. 1a) have been also extracted using the PSP model. Unlike the  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  nIFQW, there is no heterojunction in the pIFQW Ge between the Ge channel and the buffer, which explains a small junction capacitance in comparison to the nIFQW III-V. The junction capacitance reduces when reducing  $W_S$ . This is related to the electrostatic potential under the lateral spacer. Shrinking  $W_S$  will result in lowering of potential barrier in the channel (just under the spacer) and leads to a lower junction capacitance near the contact edges.

## C. Short Channel Effects

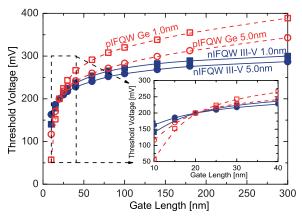

To estimate the short channel effect (SCE), a relationship between  $V_{\rm th}$  and  $L_{\rm g}$ , a set of DD simulations was done in order to extract the behaviour of  $V_{\rm th}$  for different gate lengths as shown in Fig. 6. For both  $n{\rm IFQW~III-V}$  with  $W_{\rm S}=1$  nm and  $W_{\rm S}=5$  nm, the  $\Delta V_{\rm th}$  is less than 100 mV. A sharp decrease of  $V_{\rm th}$  for gate lengths ranging from 32 nm down to 10 nm is observed. This can enhance the line edge roughness induced variability for  $L_{\rm g}<50$  nm. On the other hand, we have found that the  $p{\rm IFQW}$  Ge suffers from larger SCEs due to a relatively weak quantum confinement in the Ge channel in comparison to the  $n{\rm IFQW~III-V}$ .

Fig. 6. Threshold voltage versus the gate length of the IFQW-CMOS for two different lateral spacer widths ( $W_S=1~\mathrm{nm}$  and  $5~\mathrm{nm}$ ).

The confinement of carriers in the QW in a combination with the high p-type doping concentration in the nIFQW III-V (n-type doping for the pIFQW Ge) below the channel provides excellent electrostatic integrity. From the point of view of short channel control, the QW acts similarly to thin-body SOI structures preventing carriers from spilling into buffer or substrate and provides immunity to punch-trough and DIBL which occurs when the drain current starts to be partially controlled by the drain terminal [35]. The QW also helps to relax the SCEs in the nIFQW III-V. In contrast, a weak confinement in the pIFQW Ge is responsible of the SCEs enhancement in respect to the 24 nm gate length FDSOI counterparts [32] or the 16-28 nm gate length SOI FinFETs by the 14 nm technology [33]. In general, the SCEs have a less impact on the SS and DIBL of IFQW devices when compared

to equivalent conventional 18 nm gate Si-MOSFETs [30][31] exhibiting a SS $\simeq$ 93 mV/Dec and a DIBL $\simeq$ 90 mV/V.

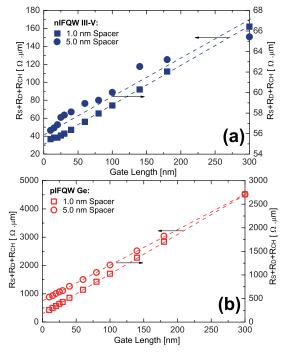

#### D. Access Resistances

We have employed the transmission line method (TLM) to calculate the access resistances. The calibrated DD simulations are used to simulate devices with different gate lengths in a linear regime. The total resistance of a device includes the S/D contact resistances ( $R_{\rm S}+R_{\rm D}$ ) and the channel resistance ( $R_{\rm CH}$ ). The access resistance,  $R_{\rm S}+R_{\rm D}$ , can be extracted by extrapolating the total resistance ( $R_{\rm S}+R_{\rm D}+R_{\rm CH}$ ) at  $L_{\rm g}=0$  nm as shown in Fig. 7. In the case of nIFQW III-V, increasing the  $W_{\rm S}$  by a factor of 5 (from 1 nm to 5 nm) leads to an increase in the access resistance by a factor of 2 only. This demonstrates a weak dependence of the access resistance on  $W_{\rm S}$ . The calculated access resistance of the pIFQW Ge for both 1 nm and 5 nm spacers are larger than those observed for the nIFQW III-V. This can be explained by a low mobility in the Ge channel below the spacer area.

Fig. 7. Total resistances ( $R_S+R_D+R_{CH}$ ) versus gate length of the IFQW-CMOS for  $W_S=1$  nm and  $W_S=5$  nm. (a) The nIFQW III-V and (b) the pIFQW Ge FETs.

The formation of the S/D regions using overgrowth, when dopants are incorporated and activated during the regrowth process, has technological advantages compared to implanted junctions. The drawbacks of implantation are: (i) the need for activation results in intermixing and inter-diffusion of spacers, which may result in a mobility reduction, and (ii) a relatively low S/D doping concentration that can be activated after implantation in the range of  $5\times10^{18} {\rm cm}^{-3}$  to  $1\times10^{19} {\rm cm}^{-3}$ , resulting in a higher access resistance. A summary of the extracted macroscopic parameters of the IFQW-CMOS is shown in Table II. There, the "effective source velocity" is a measure of the average velocity at the source end of the

channel [36], a product of classical injection velocity and ballistic ratio [37].

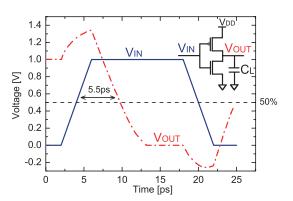

#### E. Circuit Propagation Time Delay

Circuit speed is one of the most critical figures of merit in the VLSI design. The transient behaviour of a CMOS inverter, as a basic circuit element, is simulated using a mixed-mode technique involving device and circuit simulations. The IFQW-CMOS is physically simulated, subject to time-dependent bias conditions, employing the macroscopic parameters such as capacitances and access-resistances.

The IFQW-CMOS inverter has been constructed as show in the inset of Fig. 8. The drain terminals of the inverter are connected to a load capacitor, an important factor in determining a propagation delay. This load includes a wire load capacitance and input capacitances of following inverters. The edge time for an input  $V_{\rm IN}$  (0 V  $\rightarrow$  1 V or 1 V  $\rightarrow$  0 V) is 4 ps. A propagation delay, the time difference between the 50% transition points of the input and output signals, estimated from such simulations is  $\sim 5.5$  ps. The reduced overall  $C_G$ of the IFQW-CMOS (Figs.4 and 5) in conjunction with the expected increase in the drive current (Figs. 2 and 3) significantly reduces the propagation delay. The good electrostatic control of the IFQW-CMOS with  $W_S = 1$  nm makes its circuit performance to be a much better compared to Si or FDSOI devices [32] and to be close to SOI FinFETs by 14 nm technology [33], while the structure with  $W_S = 5$  nm becomes largely degraded.

Fig. 8. Propagation time delay of an inverter based on the IFQW-CMOS ( $W_{\rm S}{=}1$  nm). The inset shows the schematic configuration of the inverter.

Finally, the lower DoS in III-V materials leads to a larger DS compared to Si devices, and thus to a larger  $T_{\rm INV}$  [29]. This can impact the performance in a triple way: (i) via a decrease of the  $C_{\rm OX} = \kappa_{\rm OX}/T_{\rm INV}$  capacitance and thus a decrease of electron density in inversion layer; (ii) via a SS relaxation and; (iii) via a DIBL relaxation [38]. The low DoS in III-V channels significantly affects the gate drivability when the gate-to-channel separation is aggressively reduced. Consequently, a part of the gate voltage overdrive that must support the inversion layer charge is consumed by the corresponding movement of Fermi level relative to a conduction band edge. A well optimised QW channel thickness can neutralize this DoS induced drawback by widening a distribution of the charge in the channel. The widely distributed charge in the channel

| > MANUSCRIPT ID: TO BE ASSIGNED | 6 |

|---------------------------------|---|

|---------------------------------|---|

|                                                         | nIFQW III-V      |                    | pIFQW Ge              |                       |  |

|---------------------------------------------------------|------------------|--------------------|-----------------------|-----------------------|--|

|                                                         | $W_{\rm S}=1$ nm | $W_{\rm S}{=}5~nm$ | $W_{\rm S}{=}1~nm$    | $W_{\rm S}{=}5~nm$    |  |

| Drain Induced Barrier Lowering [mV/V]                   | 35.0             | 27.0               | 74.0                  | 65.0                  |  |

| Short Channel Effect [V]                                | 0.1              | 0.087              | 0.16                  | 0.20                  |  |

| Sub-threshold Slope [mV/Dec]                            | 71.0             | 76.0               | 91.0                  | 95.0                  |  |

| Effective Source Velocity [ $\times 10^7$ cm/s]         | 8.0              | 6.5                | 4.1                   | 3.7                   |  |

| Saturation Velocity [ $\times 10^7$ cm/s]               | 0.9              | 0.9                | 0.6                   | 0.6                   |  |

| Access Resistance $[\Omega.\mu m]$                      | 15.0             | 28.0               | 100.0                 | 375.0                 |  |

| Gate-to-Channel Capacitance [ $\mu$ F.cm <sup>2</sup> ] | 1.85             | 1.85               | 4.147                 | 4.163                 |  |

| Fringing Capacitance [ $\mu$ F.cm <sup>2</sup> ]        | 1.50             | 1.30               | 2.635                 | 1.767                 |  |

| Junctions Capacitance [μF.cm <sup>2</sup> ]             | 0.90             | 0.82               | $1.63 \times 10^{-8}$ | $1.85 \times 10^{-8}$ |  |

| Short Channel Mobility [cm <sup>2</sup> /V.s]           | 472.0            | 276.0              | 125.4                 | 71.83                 |  |

TABLE II FIGURES OF MERIT FOR THE IFQW-CMOS WITH TWO DIFFERENT LATERAL SPACER WIDTHS (1 NM AND 5 NM).

will lower  $V_{\rm G}$  required to move the channel potential thus quickly achieving a carrier concentration for effective channel transport.

#### V. CONCLUSION

Hierarchical multi-scale simulations of the InGaAs/Ge hybrid CMOS technology using MC technique, DD method, compact modelling approach, and TCAD mixed-mode circuit modelling have shown that a destructive impact of the low DoS (a large DS) in III-V materials can be partially neutralized by a design of QW channel. In addition, the QW and the buffer doped a 1 nm below the channel reduce short channel effects by enhancing carrier confinement. The simulations demonstrate a small effect of W<sub>S</sub> on the electrostatic integrity (SS and DIBL) and access resistances in the IFOW-CMOS thanks to the device structure and the heavily doped overgrowth S/D. The calculated access resistances are lower than those in Si counterparts. W<sub>S</sub> has also a relatively small impact on C<sub>GEXT</sub> due to a geometrical shape of the S/D that reduces the effect of the outer fringing capacitance. Shrinking W<sub>S</sub> has led to a smaller inner fringing capacitance and a larger drive current. The good electrostatic control of the IFQW-CMOS with W<sub>S</sub>=1 nm makes its circuit performance to be a much better compared to Si or FDSOI devices, even if a DIBL degradation is observed [32], similarly to SOI FinFETs by 14 nm technology [33]. The reduced overall gate capacitance of the InGaAs/Ge hybrid IFQW-CMOS in conjunction with the large drive current have led to a significant reduction in the circuit propagation delay ( $\sim 5.5$  ps).

In summary, we have demonstrated that an excellent electrostatic control can be designed into a III-V/Ge hybrid CMOS by taking advantage of the channel confinement, thanks to a heterostructure transistor architecture. Such heterostructure design can be tuned for optimal performance delivering a very fast switching and a short propagation delay thus decisively reducing energy dissipation and further reducing device self-heating. This high mobility dual channel CMOS thus offers a high performance boost for the sub-16 nm technology nodes creating a competitive advantage for nano-electronics industry players.

# REFERENCES

S. Takagi, R. Zhang, S. H. Kim, N. Taoka, M. Yokoyama, J. K. Suh, R. Suzuki, and M. Takenaka, "MOS interface and channel engineering

- for high-mobility Ge/III-V CMOS," in *Proc. IEEE IEDM Tech. Dig.*, pp. 23.1.1–23.1.4, 2012.

- [2] J. A. Del Alamo, "Nanometre-scale electronics with III-V compound semiconductors," *Nature*, vol. 479, pp. 317–323, 2011.

- [3] K. J. Kuhn, "Considerations for Ultimate CMOS Scaling," *IEEE Trans. Electron Devices*, vol. 59, no. 7, pp. 1813–1828, 2012.

- [4] K. Kalna, N. Seoane, A. J. Garcia-Loureiro, I. G. Thayne, and A. Asenov, "Benchmarking of Scaled InGaAs Implant-Free NanoMOSFETs," *IEEE Trans. Electron Devices*, vol. 55, no. 9, pp. 2297—2306, 2008.

- [5] J. D. Bude, "MOSFET modelling into the ballistic regime," in *Proc. SISPAD*, pp. 23–26, 2000.

- [6] G. Nicholas, B. De Jaeger, D. P. Brunco, P. Zimmerman, G. Eneman, K. Martens, M. Meuris, and M. M. Heyns, "High-Performance Deep Submicron Ge pMOSFETs With Halo Implants," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2503–2511, 2007.

- [7] S. J. Whang, S. J. Lee, F. Gao, N. Wu, C. X. Zhu, J. S. Pan, L. J. Tang, and D. L. Kwong, "Germanium p- & n-MOSFETs fabricated with novel surface passivation (plasma-PH<sub>3</sub> and thin AlN) and TaN/HfO<sub>2</sub> gate stack," in *Proc. IEEE IEDM Tech. Dig.*, pp. 307–310, 2004.

- [8] D. Kuzum, A. Pethe, T. Krishnamohan, Y. Oshima, Y. Sun, J. P. McVittie, P. A. Pianetta, P. C. McIntyre, and K. C. Saraswat, "Interface-Engineered Ge (100) and (111), N- and P-FETs with High Mobility," in *Proc. IEEE IEDM Tech. Dig.*, pp. 723—726, 2007.

- [9] T. Skotnicki and F. Boeuf, "How can high mobility channel materials boost or degrade performance in advanced CMOS," in *Proc. IEEE VLSI Symp. Tech. Dig.*, pp. 153–154, 2010.

- [10] G. Hellings, G. Eneman, and M. Meuris, "Scalable Quantum Well Device and Method For Manufacturing the Same," US Patent application no. 2009/0283,756, European Patent Application 08168648.7.

- [11] B. Benbakhti, J. S. Ayubi-Moak, K. Kalna, D. Lin, G.Hellings, G. Brammertz, K. De Meyer, I. Thayne, and A. Asenov, "Impact of interface state trap density on the performance characteristics of different III—V MOSFET architectures," in *Microelectron. Reliab.*, vol. 50, pp. 360—364, 2010.

- [12] B. Benbakhti, A. Martinez, K. Kalna, G. Hellings, G. Eneman, K. De Meyer and M. Meuris, "Simulation study of performance for a 20 nm gate length In<sub>0.53</sub>Ga<sub>0.47</sub>As Implant Free Quantum Well MOSFET," *IEEE Trans. Nanotechnol.*, vol. 11, no. 4, pp. 808–817. 2012.

- [13] E. Towie, K. H. Chan, B. Benbakhti, C. Riddet, and A. Asenov, "Statistical Variability in Implant Free Quantum Well MOSFETs with InGaAs and Ge: A comparative 3D simulation study," in *Proc. Intel European Research and Innovation Conference*, 2011.

- [14] D. Lin, G. Brammertz, S. Sioncke, C. Fleischmann, A. Delabie, K. Martens, H. Bender, T. Conard, W. H. Tseng, J. C. Lin, W. E. Wang, K. Temst, A, Vatomme, J. Mitard, M. Caymax, M. Meuris, M. Heyns, and T. Hoffmann, "Enabling the high-performance InGaAs/Ge CMOS: a common gate stack solution," in *Proc. IEEE IEDM Tech. Dig.*, pp. 327 330, 2009.

- [15] G. Eneman, D. P. Brunco, P. J. Roussel, G. Hellings, S. Kubicek, N. Horiguchi, N. Collaert, and A. Thean, "Quantum Well Band Calculations and Their Impact on Device Isolation and Work Function Requirements for SiGe and III/V Strained Heterostructure FinFETs," in *Proc. IEEE VLSI Symp. Tech. Dig.*, pp. 92-93, 2013.

- [16] B. Benbakhti, K. H. Chan, E. Towie, K. Kalna, C. Riddet, X. Wang, G. Eneman, G. Hellings, K. De Meyer, M. Meuris, and A. Asenov, "Numerical analysis of the new Implant-Free Quantum-Well CMOS:

DualLogic approach, "Solid-St. Electron., vol. 63, no. 1, pp. 14–18, 2011.

- [17] Sentaurus sdevice A-2008.09, Synopsys, Inc., Mountain View, CA, 2008

- [18] B. Cheng, S. Roy, G. Roy, F. Adamu-Lema and A. Asenov, "Impact of intrinsic fluctuations in decanano MOSFETs on yield and functionality of SRAM cells," in *Solid-State Electronics*, vol. 49, pp. 740-746, 2005.

- [19] S. Babiker, A. Asenov, N. Cameron, S. P. Beaumont, and J. R. Barker, "Complete Monte Carlo RF analysis of real short-channel compound FETs," *IEEE Trans. Electron Devices*, vol. 45, no. 8, pp. 1644–1652, 1998.

- [20] K. Kalna, S. Roy, A. Asenov, K. Elgaid, and I. Thayne, "Scaling of Pseudomorphic High Electron Mobility Transistors to Decanano Dimensions," *Solid-St. Electron.*, vol. 46, no. 5, pp. 631–638, 2002.

- [21] J. R. Watling, C. Riddet, M. K. H. Chan, and A. Asenov, "Simulation of hole-mobility in doped relaxed and strained Ge layers," *J. Appl. Phys.*, vol. 108, p. 093715, 2010.

- [22] C. Riddet, J. R. Watling, K. H. Chan, and A. Asenov, "Monte Carlo simulation study of the impact of strain and substrate orientation on hole mobility in Germanium," *Journal of Physics: Conference Series*, vol. 242, p. 012017, 2010.

- [23] D. A. J. Moran, K. Kalna, E. Boyd, F. McEwan, H. McLelland, L. Zhuang, C. R. Stanley, A. Asenov, and I. Thayne, "Self-aligned 0.12 μm T-gate In.<sub>53</sub>Ga.<sub>47</sub>As/In.<sub>52</sub>Ga.<sub>48</sub>As HEMT technology utilising a non-annealed ohmic contact strategy," in *Proc. 29th ESSDERC*, pp. 315–318, 2003.

- [24] K. Kalna, K. Elgaid, I. Thayne, and A. Asenov, "Modelling of InP HEMTs with high Indium content channels," in *Proc. 17th Indium Phosphide Related Materials*, pp. 61–65, 2005.

- [25] E. Ungersboeck and H. Kosina, "The Effect of Degeneracy on Electron Transport in Strained Silicon Inversion Layers," in *Proc. SISPAD*, pp. 311–314, 2005.

- [26] B. Benbakhti, K. Kalna, K. Chan, E. Towie, G. Hellings, G. Eneman, K. De Meyer, M. Meuris, and A. Asenov, "Design and analysis of the In<sub>0.53</sub>Ga<sub>0.47</sub>As implant-free quantum-well device structure," *Microelectron. Eng.*, vol. 88, pp. 358–361, 2011.

- [27] G. Gildenblat, X. Li, H. Wang, W. Wu, R. Langevelde, A. J. Scholten, G. D.J. Smit and D. B. M. Klaassen, "Introduction to PSP MOSFET Model," *Nanotech.*, 2005.

- [28] J.-C. Guo, C. C. H. Hsu, P.-S. Linz, and S. S. Chung, "An Accurate "Decoupled C-V" Method for Characterizing Channel and Overlap Capacitances of Miniaturized MOSFET," in *Proc. VLSITSA*, pp. 256–260, 1993.

- [29] W. Wang, J. C. M. Hwang, Y. Xuan, and P. D. Ye, "Analysis of Electron Mobility in Inversion-Mode Al<sub>2</sub>O<sub>3</sub>/In<sub>X</sub>Ga<sub>1-X</sub>As MOSFETs," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 1972–1978, 2011.

- [30] X. Wang, A. R. Brown, N. Idris, S. Markov, G. Roy and A. Asenov, "Statistical Threshold-Voltage Variability in Scaled Decananometer Bulk HKMG MOSFETs: A Full-Scale 3-D Simulation Scaling Study," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2293–2301, 2011.

- [31] S. Markov, X. Wang, N. Moezi and A. Asenov, "Drain Current Collapse in Nanoscaled Bulk MOSFETs Due to Random Dopant Compensation in the Source/Drain Extensions," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2385–2393, 2011.

- [32] N. Planes et al, "28nm FDSOI technology platform for high-speed low-voltage digital applications," *IEEE VLSI Symp. Tech. Dig.*, pp. 133–134, 2012.

- [33] C. H. Lin et al., "High performance 14nm SOI FinFET CMOS technology with  $0.0174\mu\text{m}^2$  embedded DRAM and 15 levels of Cu metallization," in *Proc. IEEE IEDM Tech. Dig.*, pp. 74–76, 2014.

- [34] X. Wang, A. R. Brown, B. Cheng and A. Asenov, "Statistical variability and reliability in nanoscale FinFETs," in *Proc. IEEE IEDM Tech. Dig.*, pp. 103-106, 2011.

- [35] J. Mitard, L. Witters, G. Eneman, G. Hellings, L. Pantisano, A. Hikavyy, R. Loo, P. Eyben, N. Horiguchi and A. Thean, "85nm-Wide 1.5mA/µm-ION IFQW SiGe-pFET: Raised vs Embedded Si<sub>0.75</sub>Ge<sub>0.25</sub> S/D Benchmarking and In-Depth Hole Transport Study," in *Proc. IEEE VLSI Symp. Tech. Dig.*, pp. 163–164, 2012.

- [36] M.S. Lundstrom and Z. Ren, "Essential Physics of Carrier Transport in Nanoscale MOSFETs," *IEEE Trans. Electron Devices*, vol. 49, no. 1, pp.133–141, 2002.

- [37] V. Barral, T. Poiroux, J. Saint-Martin, D. Munteanu, J.-L. Autran, and S. Deleonibus, "Experimental Investigation on the Quasi-Ballistic Transport: Part I Determination of a New Backscattering Coefficient Extraction Methodology," *IEEE Trans. Electron Devices*, vol. 56, no. 3, pp. 408–419, 2009.

[38] M. H. Na, E. J. Nowak, W. Haensch, and J. Cai, "The effective drive current in CMOS inverters," in *Proc. IEEE IEDM Tech. Dig.*, pp. 121–124, 2002.

Brahim Benbakhti received the MSc and PhD degrees in microwave and microtechnology from Lille University, Lille, France, in 2003 and 2007, respectively. He is currently with the Electronics and Electrical Engineering Department, Liverpool JMU, UK. His current research interests include the reliability characterization and simulation of III-nitrides-based devices, transistor structure engineering, nanoscale III-V and Ge channel MOSFETs.

Kah Hou Chan was born in Tawau, Malaysia in 1975. He received the MEng degree in Electronics Communication Engineering from University of Hull, UK, in 2001. He is currently writing-up his PhD thesis on Ge-based channel nano transistors from University of Glasgow, UK, while pursuing his part-time hobby of data science using Microsoft-based education platform in Canada.

Ali Soltani has received the BSc degree in theoretical physics and MSc in optoelectronic from Lorraine University in 1994 and 1996, respectively. He obtained his PhD degrees in electrical engineering from Metz University & Supelec, Metz, in 2001. He joined IEMN, Lille-France in 2002 as a assistant professor of the Lille 1 University. Since 2006, his activities include the Al(Ga)N/GaN resonant tunneling diodes, X-UV photodetectors, elastic wave sensors, the design and fabrication of wide bandgap, high-power, and high frequency devices.

Karol Kalna received MSc (Hons.) in Solid-State Physics and PhD in Condensed Matter from Comenius University, Bratislava, Czechoslovakia, in 1990 and in 1998, respectively. He is Associated Professor in Electronic Systems Design Centre at Swansea University, UK. He held an EPSRC Advanced Research Fellowship and pioneered III-V MOSFETs from 2002. His current research interests are simulations of nanoscale transistors for digital applications, GaN HEMTs, and ZnO nanowires.