# Key issues and solutions for characterizing hot carrier aging of nano-meter scale nMOSFETs

M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, and A. Asenov

Abstract—Silicon bandgap limits the reduction of operation voltage when downscaling device sizes. This increases the electrical field within a device and hot carrier aging (HCA) is becoming an important reliability issue again for some CMOS technologies. For nano-devices, there are a number of challenges for characterizing their HCA: the random charge-discharge of traps in gate dielectric causes 'within-a-device-fluctuation (WDF)', making the parameter shift uncertain after a given HCA. This can introduce errors when extracting HCA time exponents and it will be shown that the lower envelope of the WDF must be used. Nano-devices also have substantial device-to-device variation (DDV) and multiple tests are needed for evaluating their standard deviation,  $\sigma$ , and mean value,  $\mu$ . Repeating the time-consuming HCA tests is costly and a voltage-step-stress method is applied to reduce the number of tests by 80%. For a given number of devices under tests (DUTs), there is little information on the accuracy of the extracted  $\sigma$  and  $\mu$ . We will develop a method to provide this information, based on the defect-centric model. For 40 DUTs with an average of 10 traps per device, the extracted  $\mu$  and  $\sigma$  has an accuracy of  $\pm 14\%$  and  $\pm 24\%$ respectively with a 95% confidence.

Index terms: Hot carriers, Aging, Device-to-device variations, Time dependent variations, BTI, Random Telegraph Noise, Instabilities, Fluctuation, Reliability, Defects.

# I. INTRODUCTION

In 1980s, hot carrier aging (HCA) was the most important reliability issue as downscaling device size without reducing operation voltage, Vdd, increases electrical field within the device [1]-[3]. HCA was alleviated since 1990s, because of the reduced Vdd. As Vdd approaches the limit imposed by the silicon bandgap, downscaling the channel length leads to a rapid rise of HCA [4]-[6]. It has been reported that, for some CMOS technologies, HCA can even be more severe than bias temperature instabilities [4]-[6] and HCA has been revisited by many researchers recently [4-17]. There are important differences between the HCA of nano-devices and the classical HCA in 1980s. For example, the worst HCA used to occur under Vg~Vdd/2, but HCA of nano-devices under

Manuscript received MMM DDD, 2016. This work was supported by the Engineering and Physical Science Research Council of UK under the grant no. EP/L010607/1. The test samples were supplied by David Vigar of Cambridge Silicon Radio. The review of this paper was arranged by Editor W. WWW. M. Duan, J. F. Zhang (J.F.Zhang@ljmu.ac.uk), Z. Ji, and W. Zhangare with the Department of Electronics and Electrical Engineering, Liverpool John Moores University, Liverpool L3 3AF, U.K.

B. Kaczer is with Imec, Leuven B-3001, Belgium.

A. Asenov is with the Department of Electronics and Electrical Engineering, University of Glasgow, Glasgow G12 8QQ, U.K.

Vg=Vd=Vdd is substantially higher than that under Vg~Vdd/2 [5,9,11]. It is proposed that the HCA of nano-devices is driven by carrier energy and carrier-carrier interaction [11,14,16,17] and multi-vibration excitation [11] play important roles. The objective of this work is to investigate some key issues in characterizing the HCA of nano-nMOSFETs.

The HCA kinetics follows a power law against both stress time and biases [1,18],

$$HCA = C V^m t^n$$

. (1)

where C is a constant. To predict the long term HCA under operation Vdd, it is important to extract the exponent, m and n, accurately, but there are a number of challenges for this extraction from nano-devices. In our recent iedm work [5], we addressed two key issues:

- (i) In the presence of 'within-a-device-fluctuation (WDF)' [19,20] for nano-devices, one must use the lower envelope of the WDF when extracting the time exponent.

- (ii) The device-to-device variation (DDV) requires repeating the tests many times to obtain the statistical properties [21,22]. Aging tests are time consuming and its repetition is costly. The voltage step stress technique can reduce the number of tests by 80%.

In this work, in addition to describe the above two issues in more details, we extend the iedm work [5] by addressing another two key issues:

- (iii) The accuracy of the evaluated standard deviation,  $\sigma$ , and the mean value,  $\mu$ , of DDV increases with the number of devices under tests (DUTs). In practice, however, the number of DUTs is limited by test time. When a limited number of DUTs is used for evaluating  $\sigma$  and  $\mu$ , there is little information on their accuracy. For the first time, we will develop a method for estimating their accuracy against the number of DUTs.

- (iv) During HCA, positive bias temperature instability (PBTI) occurs near the source [12]. The effect of PBTI on the kinetics of HCA will be assessed.

# II. DEVICES AND EXPERIMENTS

The MOSFETs used were fabricated by a 28 nm planar CMOS technology. The channel length and width are 27 ×90 nm with HK/metal gate. A wide channel length of 900 nm was also used, reducing the device-to-device variation to <±8%. The gate dielectric stack consists of a Hafnium oxide and a SiON interfacial layer with a 1.2 nm equivalent oxide thickness.

The HCA was carried out under Vg=Vd at 125 °C, rather than room temperature, as it was reported that HCA increases

with temperature for modern CMOS nodes [12,23]. The threshold voltage, Vth, was monitored from the Vg shift under a fixed drain current of 100 nA×W/L [5,24]. The nano-meter devices have an as-fabricated DDV at time zero. Some researchers reported no correlation between the time-zero DDV and time-dependent DDV [22], while others observed a weak correlation [25]. In this work, the effect of this time-zero DDV on the follow-on time-dependent DDV is taken into account by using the time-zero Id-Vg of each device as its own reference. For the planar CMOS process used in this work, HCA is more severe for nMOSFETs than for pMOSFETs when stressed under |Vg|=Vd| [11], so that this work will focus on the HCA of nMOSFETs.

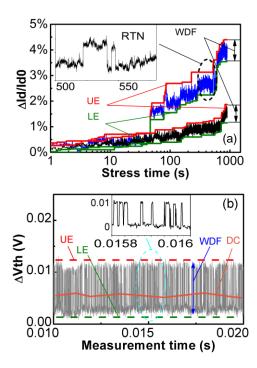

Fig. 1(a) shows a typical aging process for a  $27 \times 90$  nm device, where the data were recorded by an oscilloscope at a sampling rate of  $10^6$  points/sec, giving a time resolution of 1  $\mu$ s, which is fast enough to capture the charge-discharge of traps in gate dielectric [26].

Fig. 1. (a) HCA(Vg=Vd=1.3V) of two W=90nm devices shows large DDV. WDF, UE, and LE is 'within-a-device-fluctuation', the upper- and the lower-envelope. (b) shows the simplest form of WDF: a two level RTN. The 'DC' marked out the average value within 10 ms, as used in a typical SMU.

# III. RESULTS AND DISCUSSIONS

# A. Extraction of time exponents, n

Some typical HCA results are plotted against stress time for two nano-devices in Fig. 1(a). In addition to a substantial DDV, there is a considerable within-a-device-fluctuation (WDF) [19,20]. This fluctuation is not caused by the soft breakdown of the gate dielectric, since the gate current is two orders of magnitude less than the fluctuation in the drain current. Moreover, in its simplest form, the WDF only has two-levels, a signature of random telegraph noise rather than breakdown, and

one example is given in Fig. 1(b). This supports that the fluctuation in Fig. 1(a) originates from the random charge/discharge of traps in gate dielectrics.

The large DDV of WDF in Fig. 1(a) can have two sources: a large variation of trap number per device and a large variation of the impact of one trap on devices. To explain the latter, one should note that the current flow in the device is not uniform [21]. The trap will have a larger impact on a device when the local current beneath it is high [27]. It has been shown that the impact of a trap on the device follows an exponential distribution [21].

The WDF introduces uncertainty to the HCA after a given stress: the parameter shifts can be anywhere between the upper envelope (UE) and lower envelope (LE) of the WDF [19,20]. LE is caused by the defects that do not discharge. Fig. 1(a) shows that LE increases with HCA stress levels, so that these defects were charged by the HC stress. Once they are charged, they remain charged during the measurement. In contrast, 'UE' is the upper-envelope of the fluctuation. It contains two components: LE and the fluctuation. It represents the 'total' degradation level. When a commercial 'DC' source-and-measure unit is used, it effectively takes the average within, for example, 10 ms, as the 'DC' line marked out in Fig. 1(b).

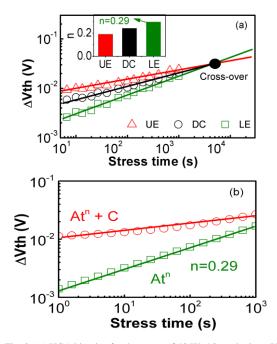

Fig. 2. (a) HCA kinetics for the mean of 40 W=90nm devices. UE, DC, and LE have different 'n' (inset). (b) Incorrect inclusion of an as-grown component, 'C', gives an apparent lower 'n'.

Given this uncertainty, the challenge is how to extract the time exponent, n, reliably for nano-devices. One effective method for suppressing the fluctuations in Fig. 1 is to use the mean value of multiple devices. Fig. 2(a) shows that smooth data are obtained for the UE, LE and DC, when the mean of 40 devices was used. The n extracted from these three, however, are different, with UE giving the lowest and LE having the highest n. This leads to the cross-over of LE from UE, when

extrapolating ahead, which is not physically meaningful, as the LE should never be higher than UE [19,20].

To investigate whether UE or LE should be used for extracting n, we examine their dependence on HCA. Fig. 3(a) clearly shows that LE increases progressively with HCA time, but the WDF=UE-LE remains the same. As a result, LE is caused by HCA, while WDF is not. WDF originates from the 'as-grown' defects in fresh devices [27,28]. To further support this, Fig. 3(b) shows that the mean of WDF for 40 devices is a constant against HCA time.

Since WDF is not caused by HCA, it should not be included when extracting the HCA time exponent [27]-[29]. In another word, n should be extracted from LE, rather than UE. UE gives a lower apparent n, because it contains as-grown traps. This can be demonstrated in Fig. 2(b): adding a constant to a power law leads to an apparent lower n.

Fig. 3. (a) For L×W=27×90nm, LE increases with HCA, but WDF=UE-LE does not. (b) The  $\mu$ \_WDF of 40 devices and its sigma do not increase with stress time.

### B. The contribution of PBTI

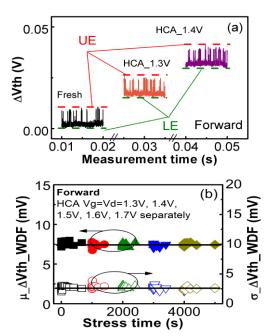

When stressed under Vg=Vd, the electrical field over the gate dielectric is not uniform. At the source end, the device suffers from positive bias temperature instability (PBTI) [12], while HCA dominates at the drain end for short channel. For long channel nMOSFETs (e.g. 1.5  $\mu$ m), it is well known that HCA reduced for higher temperature [30]. Both HCA and PBTI, however, rise with temperature for modern CMOS nodes [12,23]. PBTI is process-dependent [31] and we now assess the relative contribution of PBTI to the aging for our devices under 125 °C. Two test sequences were used in Fig. 4:

- (i) HCA(1st stress)-PBTI(2nd stress)-HCA(3rd stress);

- (ii) PBTI(1<sup>st</sup> stress)-HCA(2<sup>nd</sup> stress)-PBTI(3<sup>rd</sup> stress).

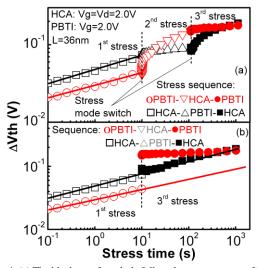

The same Vg were used for all stresses. A comparison of the two '1st stress' in Fig. 4(a) shows that the HCA is clearly stronger than PBTI. The PBTI ( $2^{nd}$  stress, the symbol ' $\Delta$ ' in Fig.

4(a)) after the HCA (1<sup>st</sup> stress) only produces modest further aging. In Fig. 4(b), we remove the  $2^{nd}$  stress period, so that the HCA (3<sup>rd</sup> stress, ' $\blacksquare$ ') is joined together with the HCA (1<sup>st</sup> stress, ' $\square$ '). It can be seen that two HCA essentially follows the same kinetics, so that the impact of the PBTI (2<sup>nd</sup> stress) on the HCA kinetics is modest. As a result, the HCA kinetics reported in this work is dominated by the hot carrier aging process.

On the other hand, when the HCA ( $2^{nd}$  stress, ' $\nabla$ ') was applied after the PBTI ( $1^{st}$  stress), Fig. 4(a) shows  $\Delta V$ th rises substantially above the level extrapolated from the power law line of the PBTI ( $1^{st}$  stress), confirming the dominance of HCA. When HCA ( $2^{nd}$  stress) was removed and the PBTI ( $3^{rd}$  stress) is joined with the PBTI ( $1^{st}$  stress), Fig. 4(b) shows that the two PBTIs do not follow the same kinetics.

It should be pointed out that, although HCA dominates the aging kinetics under our test conditions (Vg=Vd and channel length less than 36 nm), the relative strength of PBTI against HCA will increase for longer channel and higher Vg/Vd.

Fig. 4. (a) The black set of symbols follow the test sequence of HCA(1<sup>st</sup> stress), PBTI(2<sup>nd</sup> stress), and HCA(3<sup>rd</sup> stress). The red set of symbols follow the test sequence of PBTI(1<sup>st</sup> stress), HCA(2<sup>nd</sup> stress), and PBTI(3<sup>rd</sup> stress). (b) The 2<sup>nd</sup> stress periods were removed for both test sequences. The HCA kinetics is hardly affected by the preceding PBTI, but PBTI kinetics is substantially affected by the preceding HCA.

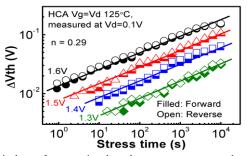

Fig. 5. Typical tests for extracting the voltage exponent repeats the tests under several different biases. The forward and reverse  $\Delta V th$  measured under Vd=0.1V agrees well here. The drain for stress and measurement is the same for the forward measurement, while the drain was swapped with the source after stress for the reverse measurement.

### C. Extraction of voltage exponent, m

The voltage exponent, m, is conventionally extracted by repeating the HCA under several (e.g. 4~6) different stress biases with one new device used for each bias, as shown in Fig. 5. This is acceptable for large devices where the DDV is negligible and only one test is needed for each bias. For nano-meter devices, however, multiple tests have to be carried out to take their considerable DDV into account [21,22]. The test time becomes costly and there is a need to reduce it.

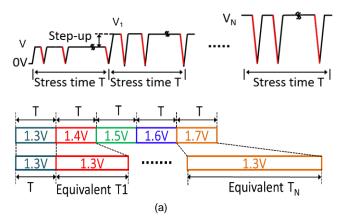

A voltage-step-stress (VSS) technique has been proposed for negative bias temperature instability [32] that allows m being extracted from just one device and reduces the number of tests by ~80%. We investigate the applicability of VSS to HCA here, first on a large device (27×900 nm) and then on nano-devices.

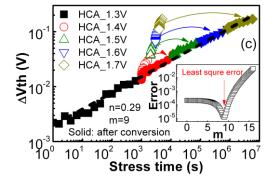

Fig. 6. Voltage-Step-Stress (VSS) technique for HCA. (a) One device was stressed for a time T and the stress Vg=Vd was then stepped up.  $\Delta Vth$  is plotted against linear (b) and log (c) stress time. The stress time under high bias is converted to an equivalent longer time at low bias by fitting the voltage exponent 'm' (inset of (c)), based on eq. (2) in Table 1. The dashed line has n=0.29 and m=9.

The principle of VSS is given in Fig. 6(a). The stress bias was applied for a given time and then raised in steps, so that different stress biases were applied to the same device. For the same stress time, HCA is higher under higher biases and typical results are given in Fig. 6(b). A HCA under a higher bias is equivalent to a HCA under a lower bias for a longer time, as illustrated in Figs. 6(a)&6(c) and this equivalent time can be evaluated by [32],

$$T_N = T(V_N/V)^{m/n}. (2)$$

With n extracted from the 1<sup>st</sup> stress step, m can be extracted by converting the data in Fig. 6(b) to a power law in Fig. 6(c). m is fitted here by minimizing the least square error between the test data and the power law, as shown by the inset of Fig. 6(c).

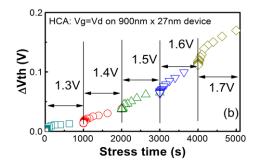

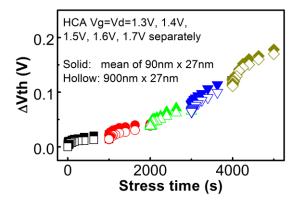

We now apply the VSS technique to nano-devices. Although there is a large DDV, Fig. 7 shows that their mean value agrees well with that of a large device. As a result, the time and voltage exponents for the mean value of nano-devices can be extracted in the same way as that used for a large device: the n can again be extracted by fitting the first stress step and m is extracted by fitting the data at other voltage steps with the power law, as illustrated in Fig. 6(c).

# D. Verification of the extracted model

As the original mission for developing a model is to use it to make prediction, a model should be validated by verifying its prediction capability.

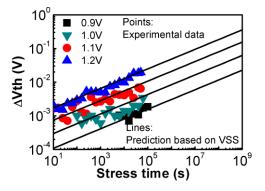

The test data under high stress biases  $(1.3 \sim 1.7 \text{ V})$  in Fig. 6 was used to extract the HCA model. We now verify its capability of predicting the HCA under low operation biases  $(0.9 \sim 1.2 \text{ V})$ . Fig. 8 shows that the model prediction (lines) agree well with the mean test data. It should be emphasized that the test data in Fig. 8 themselves were not used for fitting the model parameters.

Based on the extracted model with n=0.29 and m=9, Fig. 8 projects a mean  $\Delta V th_L E=18$  mV under an operation voltage of 0.9 V for 10 years. Adding the WDF, we have  $\Delta V th_L E=25.5$  mV. Once the mean,  $\mu$ , is predicted, the next task is to determine the standard deviation,  $\sigma$ .

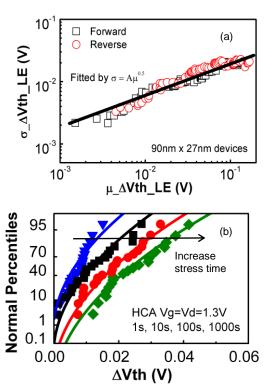

It has been proposed that the time-dependent DDV follows a defect-centric model [21,22,33]. This model predicts that the relation between  $\mu$  and  $\sigma$  is [33],

$$\sigma = \sqrt{2\eta\mu} \,, \qquad (3)$$

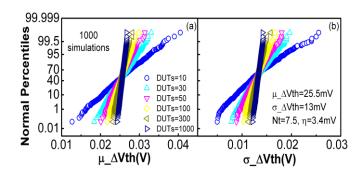

where  $\eta$  is the average impact of a trap on the device. Fig. 9(a) shows that HCA-induced DDV follows this relationship well. For a given predicted  $\mu,$  the corresponding  $\sigma$  can be determined from (3) fitted in Fig. 9(a). For example, for  $\mu{=}25.5$  mV, the corresponding  $\sigma$  is 13.0 mV. Fig. 9(b) shows that the statistical distribution of HCA-induced DDV agrees well with the defect-centric model.

### E. Assessing the accuracy of statistical properties, $\mu$ and $\sigma$

As mentioned earlier, HCA tests are time consuming and only a limited number of DUTs can be used in practice for extracting the statistical properties: mean ( $\mu$ ) and standard deviation ( $\sigma$ ). For a given number of DUTs, the question is how accurate the extracted  $\mu$  and  $\sigma$  is. This information is missing from early works and we will develop a new method to address it next. The results in this section are from simulation.

The defect-centric model has been verified based on the test results of 92,000 DUTs from 4000 lots [22] and the HCA reported here also follows it well. We can use this model to assess the accuracy of  $\mu$  and  $\sigma$  extracted from a given number of DUTs by generating HCA in each hypothetic device, as detailed below.

To determine the statistical distribution of the defect-centric model, two parameters are needed: the average number of traps per device, Nt, and the average  $\Delta V$ th induced by one trap,  $\eta$ . The  $\eta$  can be estimated from (3) and Fig. 9(a) and is  $\sim$  3.4 mV. With a typical lifetime criteria of 25  $\sim$  50 mV, Nt will be in the range of 7  $\sim$  15.

Once  $\eta$  and Nt is known, the number of traps in a hypothetic device, nt, can be randomly generated by using Poisson distribution and the threshold voltage shift induced by a trap,  $\Delta V th$ , i, can be obtained by using the exponential distribution, according to the defect-centric model [21,34]. The total  $\Delta V th$  of this device is the sum of each-trap induced shift,

$$\Delta Vth = \sum_{i=1}^{nt} \Delta Vth, i.$$

(4)

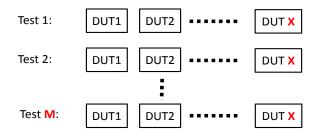

We will use Nt=7.5 and  $\eta$ =3.4 mV to demonstrate the method. The  $\Delta$ Vth for a hypothetic device, DUT1, is calculated according to (4). If we assume X devices have been used for evaluating  $\mu$  and  $\sigma$  in a test, i.e. the test 1 in Fig. 10, we can statistically calculate the  $\Delta$ Vth for these X devices. These X  $\Delta$ Vth can then be used to calculate one  $\mu$  and one  $\sigma$ , as represented by a data point in Figs. 11(a)&11(b), respectively.

Fig. 7. The mean of  $40~90\times27$ nm devices agrees well with one  $900\times27$ nm for VSS stresses.

Fig. 8. A comparison of the model prediction with the test data for  $\Delta V th$ . The model parameters in eq. (1) were extracted from VSS accelerated tests (see Fig. 7). The test data at lower voltages in this figure were not used for extracting the model parameters.

Fig. 9. Statistics of HVA-induced DDV. The lines are fitted with the defect-centric distribution. (a) Sigma versus mean. (b) Distribution after different stress time.

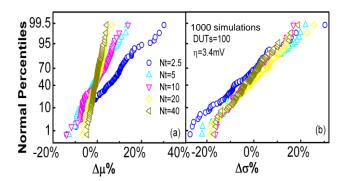

If another test engineer repeated the same test, i.e. the test 2 in Fig.10, a different group of X devices would be used, producing a different  $\mu$  and  $\sigma$  and give another data point in Fig. 11. Fig. 11 shows the statistical spread for 1000 tests, i.e. M=1000 in Fig. 10, when X DUTs were used for each test. The X was varied between 20 and 1000. As expected, the spread becomes increasingly larger when a smaller number of DUTs were used for the test.

Fig. 10. An illustration of statistical tests: In a hypothetic Test 1, engineer 1 used X DUTs for extracting the  $\mu$  and  $\sigma$  of HCA. In test 2, engineer 2 also used X DUTs, but will obtain different  $\mu$  and  $\sigma$ , because a different set of devices were used.

The number of DUTs is not the only parameter controlling the accuracy of  $\mu$  and  $\sigma$ . Fig. 12 shows that for a given X=100, the spread reduces for higher Nt, because a higher number of traps per device averages out device variations to a certain extent.

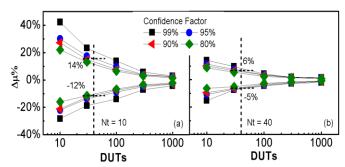

This work used 40 DUTs and we now assess the accuracy of the evaluated  $\mu$  and  $\sigma.$  Fig. 13(a) shows that the evaluated  $\mu$  has an accuracy within  $\pm 14\%$  for Nt=10,with a 95% confidence. To assess the impact of Nt, Fig. 13(b) shows that the accuracy reaches  $\pm 6\%$  when Nt=40. If 1000 DUTs were used, the accuracy will improve to  $\pm 2.6\%$  for Nt=10 and  $\pm 1.3\%$  for Nt=40.

Fig. 11. The  $\mu$  (a) and  $\sigma$  (b) extracted for different DUTs (X in Fig. 12). For a given X, the tests were repeated 1000 times (M=1000 in Fig. 12).

Fig. 12. The impact of the average number of traps, Nt, per DUT on the  $\mu$  (a) and  $\sigma$  (b) extracted for DUTs=100 when the tests were repeated 1000 times (M=1000 in Fig. 10).

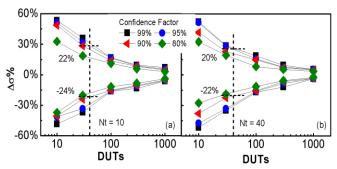

The corresponding  $\sigma$  is given in Fig. 14. When DUTs=40, the evaluated  $\sigma$  has an accuracy within  $\pm 24\%$  for Nt=10, not as accurate as  $\mu$ . An increase of Nt to 40 only makes a modest

improvement to  $\pm 22\%$ . With 1000 DUTs, an accuracy of  $\pm 5\%$  can be achieved for Nt=10.

Fig. 13. The dependence of the accuracy of mean value,  $\mu$ , on the number of DUTs used in a test for Nt=10 (a) and Nt=40 (b). The accuracy with a 95% confidence is marked out for 40 devices.

Fig. 14. The dependence of the accuracy of standard deviation,  $\sigma$ , on the number of DUTs used in a test for Nt=10 (a) and Nt=40 (b). The accuracy with a 95% confidence is marked out for 40 devices.

### IV. CONCLUSION

This work investigates the key issues and provides solutions for characterizing the hot carrier aging of nano-devices. It is shown that the WDF is not caused by the HCA, so that they must be excluded, when extracting the HCA time-exponent. This can be achieved by using the lower envelope of WDF. The commercial source-and-measure unit measures a data point by taking the average within a period. This includes a part of WDF, resulting in an under-estimation of time exponent. The voltage exponent can be extracted by using the VSS technique, reducing the number of tests by ~80%. HCA follows the defect-centric model well. Based on this model, the accuracy of the mean and standard deviation of device-to-device variation can be estimated for a given number of DUTs. For 40 DUTs with an average 10 traps per device, the accuracy for  $\mu$  and  $\sigma$  is  $\pm 14\%$  and  $\pm 24\%$ , respectively with a 95% confidence.

# REFERENCES

- [1] C. Hu, S. C. Tam, F. C. Hsu, P. K. Ko, T. Y. Chan, and K. W. Terrill, "Hot-Electron-Induced MOSFET Degradation-Model, Monitor, and Improvement", *IEEE Trans. Electron Devices*, vol. ED-32, no. 2, pp. 375-385, 1985.

- [2] P. Heremans, R. Bellens, G. Groseneneken, and H. E. Maes, "Consistent model for the hot-carrier degradation in n-channel and p-channel MOSFET's,", *IEEE Trans. Electron Devices*, vol. 35, no. 2, pp. 2194-2209, 1988.

- [3] J. F. Zhang and W. Eccleston, "Effects of high field injection on the hot carrier induced degradation of submicron pMOSFET's," *IEEE Trans. Electron Devices*, vol. 42, no.7, pp. 1269-1276, 1995.

- [4] A. Bravaix, Y. M. Randriamihaja, V. Huard, D. Angot, X. Federspiel, W. Arfaoui, P. Mora, F. Cacho, M. Saliva, C. Besset, S. Renard, D. Roy, E. Vincent, "Impact of the gate-stack change from 40nm node SiON to 28nm High-K Metal Gate on the Hot-Carrier and Bias Temperature damage", IRPS 2013,pp 2D.6.1-2D.6.9.

- [5] M. Duan, J. F. Zhang, A. Manut, Z. Ji, W. Zhang, A. Asenov, L. Gerrer, D. Reid, H. Razaidi, D. Vigar, V. Chandra, R. Aitken, B. Kaczer, and G. Groeseneken, "Hot carrier aging and its variation under use-bias: kinetics, prediction, impact on Vdd and SRAM", *IEDM* 2015 pp. 547-550.

- [6] B. Kaczer, J. Franco, M. Cho, T. Grasser, Ph. J. Roussel, S. Tyaginov, M. Bina, Y. Wimmer, L. M. Procel, L. Trojman, F. Crupi, G. Pitner, V. Putcha, P. Weckx, E. Bury, Z. Ji, A. De Keersgieter, T. Chiarella, N. Horiguchi, G. Groeseneken, and A. Thean, "Origins and Implications of Increased Channel HotCarrier Variability in nFinFETs", IRPS 2015, pp 3B.5.1-3B.5.6.

- [7] N. H. Hsu, J. W. You, H. C. Ma, S. C. Lee, E. Chen, L. S. Huang, Y. C. Cheng, O. Cheng, I. C. Chen, "Intrinsic Hot-Carrier Degradation of nMOSFETs by Decoupling PBTI Component in 28nm High-K/Metal Gate Stacks", *IRPS* 2012, pp XT.13.1-XT.13.4.

- [8] J. H. Stathis, M. Wang, R.G. Southwick, E.Y. Wu, B.P Linder, E.G. Liniger, G. Bonilla, H. Kothari, "Reliability Challenges for the 10nm Node and Beyond," *IEDM* 2014, p. 522-525.

- [9] G. T. Sasse, F. G. Kuper, and J. Schmitz, "MOSFET Degradation Under RF Stress," *IEEE Trans. Electron Devices*, vol. 55, no. 11, pp.3167-3174, 2008.

- [10] A. J. Scholten, D. Stephens, G. D. J. Smit, G. T. Sasse, and J. Bisschop, IEEE Trans. Electron Devices, vol. 58, no. 1, pp.1-8, 2011.

- [11] A. Bravaix, V. Huard, D. Goguenheim, and E. Vincent, "Hot-Carrier to Cold-Carrier Device Lifetime Modeling with Temperature for Low power 40nm Si-Bulk NMOS and PMOS FETs," *IEDM* 2011, p.622-625.

- [12] K. T. Lee, C. Y. Kang, O. S. Yoo, R. Choi, B. H. Lee, J. C. Lee, H. D. Lee, and Y. H. Jeong, "PBTI-Associated High-Temperature Hot Carrier Degradation of nMOSFETs With Metal-Gate/High-k Dielectrics", *IEEE Trans. Electron Devices*, vol. 29, no. 4, pp. 389-391, 2008.

- [13]C. Liu, K. T. Lee, S. Pae, and J. Park, "New Observations on Hot Carrier induced Dynamic Variation in Nano-scaled SiON/Poly, HK/MG and FinFET devices based on On-the-fly HCI Technique:The Role of Single Trap induced Degradation," *IEDM* 2014, p 836-839.

- [14] S. E. Rauch and G. La Rosa, "The energy-driven paradigm of NMOSFET Hot-carrier effects," *IEEE Trans. Device Mater. Rel.*, vol. 5, no. 4, pp. 701–705, 2005.

- [15] P. Magnone, F, Crupi, N. Wils, H. P. Tuinhout, and C. Fiegna, "Characterization and Modeling of Hot Carrier-Induced Variability in Subthreshold Region", *IEEE Trans. Electron Devices*, vol. 59, no. 8, pp. 2093-2099, 2012.

- [16] M. Bina, K. Rupp, S. Tyaginov, O. Triebl, and T. Grasser, "Modeling of Hot Carrier Degradation Using a Spherical Harmonics Expansion of the Bipolar Boltzmann Transport Equation", *IEDM* 2012, pp 713-716.

- [17] Y. M. Randriamihaja, A. Zaka, V. Huard, M. Rafik, D. Rideau, D. Roy, "Hot Carrier Degradation: From Defect CreationModeling to Their Impact on NMOS Parameters", *IRPS* 2012, pp. XT.15.1-XT.15.4.

- [18] Failure Mechanisms and Models for Semiconductor Devices, JEDEC, Alexandria, VA, USA, 2011.

- [19] M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, T. Schram, R. Ritzenthaler, G. Groeseneken, and A. Asenov, "New analysis method for time-dependent device-to-device variation accounting for within-device fluctuation," *IEEE Trans. Electron Dev.*, vol. 60, no. 8, pp. 2505-2511, 2013.

- [20] M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, T. Schram, R. Ritzenthaler, G. Groeseneken, and A. Asenov, "Development of a Technique for Characterizing Bias Temperature Instability-Induced Device-to-Device Variation at SRAM-Relevant Conditions". *IEEE Trans. Electron Devices*, vol. 61, no. 9, pp. 3081-3089, 2014.

- [21] B. Kaczer, T. Grasser, P. J. Roussel, J. Franco, R. Degraeve, L. A. Ragnarsson, E. Simoen, G. Groeseneken, and H. Reisinger, "Origin of NBTI variability in deeply scaled pFETs," *IRPS* 2010, pp. 26–32.

- [22] C. Prasad, M. Agostinelli, J. Hicks, S. Ramey, C. Auth, K. Mistry, S. Natarajan, P. Packan, I. Post, S. Bodapati, M. Giles, S. Gupta, S. Mudanai, K. Kuhn "Bias Temperature Instability Variation on SiON/Poly, HK/MG and Trigate Architectures," *IRPS* 2014, pp. 6A.5.1-6A.5.7

- [23] A. Bravaix, C. Guerin, V. Huard, D. Roy, J. M. Roux, and E. Vincent, "Hot-Carrier acceleration factors for low power management in DC-AC stressed 40nm NMOS node at high temperature," *IRPS* 2009, pp. 531–548.

- [24] S. F. W. M. Hatta, Z. Ji, J. F. Zhang, M. Duan, W. Zhang, N. Soin, B. Kaczer, S. De Gendt, and G. Groeseneken, "Energy distribution of positive charges in gate dielectric: probing technique and impacts of different defects", *IEEE Trans. Electron Dev.*, vol. 60, no. 5, pp. 1745-1753, 2013.

- [25] A. Kerber and T. Nigam, "Correlation of BTI induced device parameter degradation and variation in scaled Metal Gate /High-k CMOS technologies," *IRPS* 2014, pp. 6A.6.1–6A.6.6.

- [26] M. Duan, J. F. Zhang, Z. Ji, J. G. Ma, W. Zhang, B. Kaczer, T. Schram, R. Ritzenthaler, G. Groeseneken, and A. Asenov, "Key issues and techniques for characterizing Time-dependent Device-to-Device Variation of SRAM," *IEDM* 2013 pp. 774-777.

- [27] M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, T. Schram, R. Ritzenthaler, A. Thean, G. Groeseneken, and A. Asenov, "Time-dependent variation: A new defect-based prediction methodology," VLSI Tech. Symp. 2014, pp.74-75.

- [28] R. Gao, Z. Ji, S. M. Hatta, J. F. Zhang, J. Franco, B. Kaczer, W. Zhang, M. Duan, S. De Gendt, D. Linten, G. Groeseneken, J. Bi and M. Liu, "Predictive As-grown-Generation (A-G) model for BTI-induced device/circuit level variations in nanoscale technology nodes," *IEDM* 2016, pp. 778-781.

- [29] Z. Ji, S. F. W. M. Hatta, J. F. Zhang, J. G. Ma, W. Zhang, N. Soin, B. Kaczer, S. De Gendt, and G. Groeseneken, "Negative bias temperature instability lifetime prediction: Problems and solutions," *IEDM* 2013, pp. 413-416.

- [30] F.-C. Hsu, K.-Y. Chiu, "Temperature Dependence of Hot-Electron-Induced Degradation in MOSFET's", *IEEE Elec. Device Lett.*, vol. 5, no.5, pp. 148-150, 1984.

- [31] C. Z. Zhao, J. F. Zhang, M. B. Zahid, B. Govoreanu, G. Groeseneken, and S. De Gendt, "Determination of capture cross sections for as-grown electron traps in HfO<sub>2</sub>/HfSiO stacks," *J. Appl. Phys.*, 100, pp. Art. No.093716, 2006.

- [32] Z. Ji, J. F. Zhang, W. Zhang, X. Zhang, B. Kaczer, S. De Gendt, G. Groeseneken, P. Ren, R. Wang, and R. Huang, "A single device based Voltage Step Stress (VSS) Technique for fast reliability screening," *IRPS*, 2014, GD-2.1-GD-2.

- [33] L. M. Procel, F. Crupi, J. Franco, L. Trojman, and B. Kaczer, "Defect-Centric Distribution of Channel Hot Carrier Degradation in Nano-MOSFETs," *IEEE Electron. Dev. Lett.*, vol. 35, no. 12, pp. 1167-1169, Dec, 2014.