## The over-reset phenomenon in Ta<sub>2</sub>O<sub>5</sub> RRAM device investigated by the RTN-based defect probing technique

Zheng Chai, Weidong Zhang, Pedro Freitas, Firas Hatem, Jian Fu Zhang, John Marsland, Bogdan Govoreanu, Ludovic Goux, Gouri Sankar Kar, Steve Hall, Paul Chalker and John Robertson

Abstract— Despite the tremendous efforts in the past decade devoted to the development of filamentary resistive-switching devices (RRAM), there is still a lack of in-depth understanding of its over-reset phenomenon. At higher reset stop voltages that exceed a certain threshold, the resistance at high resistance state reduces, leading to an irrecoverable window reduction. The over-reset phenomenon limits the maximum resistance window that can be achieved by using a higher V<sub>reset</sub>, which also degrades its potential in applications such as multi-level memory and neuromorphic synapses. In this work, the over-reset is investigated by cyclic reset operations with incremental stop voltages, and is explained by defect generation in the filament constriction region of Ta<sub>2</sub>O<sub>5</sub> RRAM devices. This is supported by the statistical spatial defects profile obtained from the random telegraph noise based defect probing technique. The impact of forming compliance current on the over-reset is also evaluated.

Index Terms—Resistive switching, RRAM, over-reset, defect profile, random telegraph noise, Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>

Resistive-switching random access memories (RRAMs) have attracted extensive interest in the past decade as a promising candidate for future non-volatile memory applications [1-5]. RRAM devices can be categorized into either filamentary or non-filamentary [6,7] types. The filamentary type has a relatively longer development history and represents the current mainstream RRAM technology. Tremendous effort has been devoted to improving their performance such as endurance, retention, on/off window, etc. A large resistance window (RW) is always desirable for achieving better performance in applications such as multi-level memory [4] and neuromorphic synapses [8].

Resistive switching in filamentary devices has been attributed to the reversible migration of either metal ions in CBRAMs [9-11] or oxygen ions/vacancies in RRAMs [2-6]. A conductive filament is generated in RRAM during the forming through a field assisted and thermally activated hopping process. During alternate reset and set operations, the filament ruptures and restores repeatedly, leading to the high resistance state and low resistance state, respectively (HRS/LRS). It has been observed in RRAMs with various oxides such as  $HfO_2$  and  $Ta_2O_5$  [12, 13] that once  $V_{reset}$  increases beyond a certain level,  $R_{HRS}$  will start to decrease instead

Manuscript received xx. This work was supported by the EPSRC of U.K. under Grants EP/M006727/1, EP/M00662X/1, and EP/M009297/1.

The review of this paper was arranged by Editor Albert Chin.

- Z. Chai, W. Zhang, P. Freitas, F. Hatem, J. F. Zhang, J. Marsland are with the Department of Electronics and Electrical Engineering, Liverpool John Moores University, L3 3AF Liverpool, U.K. (e-mail:W.Zhang@ljmu.ac.uk).

- B. Govoreanu L. Goux, and G.S.Kar are with IMEC, 3001 Leuven, Belgium.

- S. Hall and P. Chalker are with University of Liverpool, UK, L69 3GJ.

- J. Robertson is with University of Cambridge, UK, CB2 1PZ.

of further increase; it is difficult to recover from the consequent window reduction [12, 13]. This over-reset phenomenon will therefore limit the achievable RW by using a higher  $V_{reset}$ .

The over-reset phenomenon has been explained by the migration of defects near the bottom electrode (BE) moving back into the constriction region of the filament at higher reset voltages, which re-connects the defect-rich filamentary regions near the top electrode (TE) and BE. This effect leads to a reduced resistance at HRS [12]. An alternative explanation is by the horizontal out-diffusion of defects from the filament into the surrounding dielectrics which forms additional conduction paths, hence the higher conduction current and lower resistance [13]. However, there is a lack of direct experimental evidence to support either of the above assumptions. By using the random telegraph noise (RTN)-based defect probing technique (RDT) developed in our recent work [6, 7], we provide a novel microscopic insight into the defect's spatial locations and compare the defect profiles after normal- and over- reset. The over-reset can be explained by defect generation in the filament constriction region at higher reset voltages. The impact of the compliance forming current on over-reset is also evaluated and discussed.

The  $Ta_2O_5$  filamentary RRAM devices used in this work were fabricated in a cross-point structure with a size of 75 nm  $\times$  75 nm. The device consists of a TiN/ $Ta_2O_5$ /TaOx/TaN/TiN stack. The TiN BE was sputtered at room temperature and patterned, followed by the ALD deposition of a 4-nm-thick high-quality stoichiometric  $Ta_2O_5$  layer. A nonstoichiometric 20-nm-thick TaOx film was then deposited by reactive DC magnetron sputtering using a Ta target in oxygen ambient. Without breaking the vacuum, a 10-nm-thick TaN capping layer was sputtered followed by a 30-nm-thick TiN film sputtering to form the TE. A long wire was patterned to connect the probe pad to the TE, enabling an integrated access resistance which effectively suppresses reset current overshoot [14]. We have also observed similar over-reset in other devices with either a Ti/ $Ta_2O_5$ (15nm)/ Pt stack [15] or a TiN/Hf(10nm)/ $HfO_2$ (5nm)/TiN stack [6].

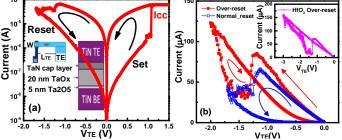

DC electrical measurements were carried out by using a Keysight B1500A semiconductor parameter analyzer with the bias applied to the TE, and the BE at ground. A forming step using the positive voltage sweep in the fresh device activates the reversible resistive switching behavior, which is capped by a compliance current (Icc) to protect the device from hard breakdown. The device structure and its I-V characteristics are shown in Fig. 1(a). It is switched between LRS and HRS during the positive set and negative reset voltage sweeps, respectively. In our previous work [6, 7], RTN has been used as the electrical measurement technique to evaluate the defect profile, providing a defect-level explanation of switching mechanisms in filamentary [6] and non-filamentary

[7] devices. The over-reset phenomenon is investigated in this work by the RDT technique carried out in both normal-reset and over-reset devices for comparison. The origin of RTN is attributed to the random electron trapping/de-trapping process in a defect located in the oxide [16]. The spatial and energy location of defects can be extracted from the dependence of time constants on the TE bias. To obtain the statistical defect profile, the device was switched on and off repeatedly for 100 cycles under fixed conditions, and the RTN measurement was carried out after each reset. The accumulative occurrence of defects at HRS can therefore be used to evaluate the statistical defect profile. Details and discussion of this technique can be found in refs. [6, 7].

Fig.1 (a) The structure (inset) and bipolar resistive switching characteristics of a 75 nm  $\times$ 75 nm  $\times$ 720, memory cell. (b) Comparison of normal reset (Vstop=-1.7V) and over-reset (Vstop=-2V) of the  $\text{Ta}_2\text{O}_5$  RRAM. The inset shows the over-reset phenomenon in HfO<sub>2</sub> RRAM devices (Vstop=-3V).

I-V characteristics of a normal reset at a stop voltage of -1.7 V and an over-reset at a stop voltage of -2 V are compared in Fig. 1(b). Both devices were formed with an Icc of 20 μA. It is clear that the currents overlap in a large part of the upward voltage sweep, suggesting that both devices start from the same LRS level, and the reset process is similar for the bias level up to -1.7 V. Since the over-reset stop voltage is higher, its current starts to increase from -1.7 V onward, and also becomes higher during the downward voltage sweep, leading to the over-reset, i.e., a lower resistance at HRS. As shown in the inset of Fig. 1(b), a similar over-reset phenomenon is also observed in HfO<sub>2</sub> RRAM devices, suggesting it is a universal issue for filamentary RRAM devices.

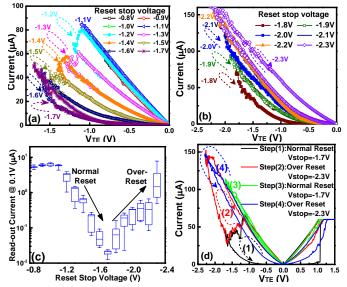

To further demonstrate the impact of over-reset on the HRS, the reset bias sweep cycle (0 V $\rightarrow$ V<sub>reset,stop</sub>  $\rightarrow$ 0 V) was repeated with the stop voltage incremented for each cycle, without invoking the set sweep in between. I-V curves during the reset and over-reset cycles, and the resistance read-out current after each reset cycle measured at V<sub>read</sub>=0.1 V, are shown in Fig. 2 (a)-(c), respectively. The device reset starts from V<sub>reset</sub> = -1.1 V, reaching the minimum HRS current at V<sub>reset</sub> = -1.7 V, and the over-reset starts from there onwards, the downward sweep current becomes higher than the upward sweep, and the read-out current also starts to increase, leading to lower HRS resistance. The upward and downward I-V curves of adjacent sweeps agree well, supporting the view that the resistance switching occurs at the higher range of V<sub>reset</sub> during each cycle. This phenomenon is contrary to the expectation that a larger V<sub>reset</sub> should always lead to a higher resistance at HRS.

The over-reset phenomenon causes irrecoverable damage to the resistance window, as shown in Fig. 2(d). After the normal set and reset switching cycle in step (1), the device underwent an over-reset and set cycle with a higher reset stop voltage at  $V_{reset} = -2.3 \text{ V}$  in step (2). After the over-reset, the window almost disappears in step (3) in which the device is set and reset with the

same conditions used in step (1), demonstrating that the detrimental effect of over-reset on RW. RW can only be partially recovered in step (4) even if  $V_{\text{reset}, \text{stop}}$  is increased to the value used in step (2), as the current sweeping direction is reversed. This clearly shows that the over-reset causes irrecoverable reduction to RW, even at higher reset voltage and current, therefore higher power consumption. The physical mechanism of over-reset is explored next with the RTN based defect probing technique.

Fig. 2. (a) I-V curves of a  $Ta_2O_5$  device being reset with incremental  $V_{reset,stop}$  in the range from -0.8 V to -1.7 V. (b) I-V curves of device being over-reset with  $V_{reset,stop}$  in the range from -1.8 V to -2.3 V. (c) The read-out current at  $V_{read}$ =0.1 V, measured after each cycle, against  $V_{reset,stop}$  on 8 devices under the same condition. (d) I-V curves of a  $Ta_2O_5$  device going through 4 set and reset cycles sequentially with different reset conditions. The set condition is fixed in each cycle at  $Icc = 60~\mu A$ .

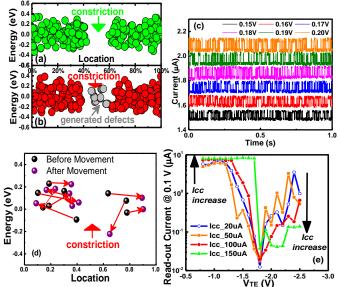

Defect locations in the X<sub>T</sub>-E<sub>T</sub> plane are extracted using the RDT technique described in refs. [6, 7] in detail, and compared after the normal reset and over- reset. The device was switched on and off repeatedly for 100 cycles under fixed conditions for normal reset and over-reset, respectively. The extracted defects are plotted as spheres and the corresponding statistical profiles of the defect occurrence at HRS are shown in Fig. 3(a)-(b). The typical RTN data are shown in Fig. 3(c). For the normal reset device, a region with no defect occurrence is observed at the center of the filament, as shown in Fig. 3(a). This result indicates that the filament constriction location is centered in the Ta<sub>2</sub>O<sub>5</sub> layer of our TiN/TaO<sub>x</sub>/Ta<sub>2</sub>O<sub>5</sub>/TiN device. Early work has reported that the filament in TaOx/Ta<sub>2</sub>O<sub>5</sub> dual-layer RRAM with Pt [17] or Ir [18, 19] metal electrodes ruptures in the Ta<sub>2</sub>O<sub>5</sub> layer near the TE interface, by the redox reaction of oxygen ions or vacancies. Since filament growth/dissolution dynamics is strongly dependent on the oxide and electrode materials and their combinations, the centered constriction location in our device is mostly likely caused by the lower Schottky barrier and lesser scavenging power of the TiN electrode used in this work, and the similar oxygen scavenging power of the nonstoichiometric TaOx layer on top of the Ta<sub>2</sub>O<sub>5</sub> switching layer, which leads to a more symmetric hour-glass shaped filament in the Ta<sub>2</sub>O<sub>5</sub> layer [20]. In our previous work we have observed that in HfO<sub>2</sub> devices, the constriction is located near to, but not at, the BE [6]. This difference can be attributed to the Hf cap layer used under the TE in HfO2 devices, which has stronger oxygen scavenging power

than the TiN BE, so that more oxygen vacancies are generated near the Hf cap, pushing the constriction region towards the BE.

Fig. 3. Statistical defect profile in the filament region of  $Ta_2O_5$ , after (a) normal- and (b) over- reset, respectively. For the normal-reset device,  $V_{\text{reset}} =$  -1.7 V,  $I_{cc} = 60~\mu\text{A}$ . For the over-reset device,  $V_{\text{reset}} =$  -2.3 V,  $I_{cc} = 60~\mu\text{A}$ . (c) Typical RTN measured at various TE biases, from which the emission/capture time constants dependence on bias are obtained to extract the defect location [6, 7]. (d) Defect movements detected during the over-reset. There is no defect movement observed within the constriction, where the defects are generated. (e) Incremental reset voltages applied on devices formed with different Icc, affecting the over-reset phenomenon.

In the over-reset  $Ta_2O_5$  device, as shown in Fig. 3(b), the constriction is also observed at the center of the filament, but there are several clusters, each consisting of several defects as labelled with grey color, being detected within the constriction. A cluster of defects observed at the same location is caused by the same defect repeatedly detected by the RTN technique during a number of the set and reset cycles, indicating that a cluster is actually only one defect that is generated at a fixed location and hardly moves during the switching cycles. The defect generation process causing the over-reset effect could be similar to that causing the permanent component of NBTI/PBTI degradations occurred in conventional high-k metal oxide gate dielectrics [21, 22]. Once generated, these defects cannot move, or be involved in the redox reaction of "normal" mobile defects moving into/out of the constriction during resistive switching [6]. The defect generation could also follow a power law for electric field acceleration with a power factor in the range of 2 and 3. The on-set of over-reset effect observed in the experiments in this work could be explained by the acceleration of defect generation at higher electric field, which happens to overtake the normal reset process at -1.7 V. To verify that the defects generated in the constriction are different from those "normal" ones, we look into the defect movement during the over-reset operations, where defect movements are extracted from the abrupt jump in read current and simultaneous changes in RTN signals, as introduced in detail in [6]. As shown in Fig. 3(d), defects outside of the constriction at HRS are mobile. However, we cannot observe any defect movement occurred to the defects generated during over-reset within the constriction at the center of the filament, i.e. they are not mobile. This is a strong indication that these generated immobile defects are different from those "normal" mobile defects responsible for resistive switching [6, 7], therefore causing partially irrecoverable over-reset phenomenon,

due to the co-existence of both types of defects, and both of them could be originated from the positively charged oxygen vacancies, within a few tenths of eV from the electrode's Fermi level [6, 23].

In early work [12] the over-reset has been interpreted as the activation and movement of defects from the BE side into the constriction, subsequently moving further towards TE under a higher reset stop voltage. This results in the constriction being gradually narrowed and shifted. But this assumption cannot explain why this type of defect movement is not reversible. In another work [13], the assumption of horizontal out-diffusion of defects from the filament into the surrounding dielectrics, leading to additional conduction paths, has been used to explain the over-reset. Our results cannot completely rule out this possibility but do provide an alternative explanation supported with experimental evidence. Additional immobile defects are generated in the constriction under strong reset field during over-reset. These facilitate current conduction typically trap-assisted-tunneling, leading to lower resistance at HRS. Meanwhile, their existence in the constriction leads to lower local electric field and makes the reset operation by normal defect movement less effective, even under the over-reset condition. This explains why the RW cannot be fully recovered.

Since the over-reset causes irreversible window reduction, it is desirable to alleviate this phenomenon. As shown in Fig. 3(d), devices formed under different Icc were tested to evaluate its impact, using the same incremental  $V_{\text{reset, stop}}$  method as shown in Fig. 2. The higher forming I<sub>cc</sub> leads to higher read-out current at LRS, due to the formation of a stronger filament. All devices reach the maximum HRS at around -1.7 V, with a steeper reset process at higher  $I_{\infty}$ . Interestingly, the extent of over-reset is reduced by using higher I<sub>cc</sub>, which can be explained as follows. The stronger filament formed at higher  $I_{cc}$  can only be ruptured at higher  $V_{reset}$ , leading to a more abrupt reset process. The conduction at HRS becomes less sensitive to the newly-generated defects in the constriction during over-reset, due to the overall larger effective filament cross section caused by higher  $I_{cc}$  [4]. Using a higher  $I_{cc}$ can alleviate, to some extent, but cannot completely avoid the over-reset problem, due to the defect generation in the filament constriction. A higher forming compliance current will lead to a number of side effects, such as higher power consumption, greater probability of device breakdown, larger resistance variation. The trade-off between higher Icc and lower level of over-reset should be carefully considered in practical application. It cannot be the ultimate solution for memory applications that primarily pursue low-current operation, therefore. Further efforts should be made to increase the critical reset voltage that causes the over-reset, potentially by using materials having lower defect generation rates and higher breakdown voltages.

In summary, the statistical defect profile in the conductive filament of  $TiN/TaO_x/Ta_2O_5/TiN$  RRAM devices has been analyzed using the RTN-based defect tracking technique. It is revealed that the constriction region is located at the center of the filament in the  $Ta_2O_5$  layer. The irrecoverable over-reset is caused by the generation of immobile defects in the constriction region which facilitates current conduction at HRS and lowers the local field in following set/reset operations. It is also found that a higher forming compliance current can alleviate, to certain extent, the over-reset phenomenon. These findings provide valuable information for improving the on/off window in filamentary metal-oxide RRAM devices.

## **REFERENCES**

- [1] S. Yu, P. Y. Chen, "Emerging Memory Technologies: Recent Trends and Prospects," *IEEE Solid State Circuits Mag.*, vol. 8, no. 2, pp. 43-56, June 2016. DOI: 10.1109/MSSC.2016.2546199

- [2] A. Chen, "A review of emerging non-volatile memory (NVM) technologies and applications," *Solid-State Electronics*, vol. 125, pp. 25-38, Nov. 2016. DOI: 10.1016/j.sse.2016.07.006

- [3] H. S. P. Wong, H. Y. Lee, S. Yu, Y. S. Chen, Y. Wu, P. S. Chen, B. Lee, F. T. Chen and M. J. Tsai, "Metal—Oxide RRAM," *Proc. IEEE*, vol. 100, no. 6, pp. 1951-1970, May 2012. DOI: 10.1109/JPROC.2012.2190369

- [4] D. Ielmini, "Resistive switching memories based on metal oxides: mechanisms, reliability and scaling," Semiconductor Science and Technology, vol. 31, no. 6, p. 063002, May 2016. DOI: 10.1088/0268-1242/31/6/063002

- [5] R. Waser and M. Aono, "Nanoionics-based resistive switching memories," Nat. Mater., vol. 6, p. 833–840, Nov. 2007. DOI: 10.1038/nmat2023

- [6] Z. Chai, J. Ma, W. D. Zhang, B. Govoreanu, J. F. Zhang, Z. Ji, M. Jurczak, "Probing the Critical Region of Conductive Filament in Nanoscale HfO<sub>2</sub> Resistive-Switching Device by Random Telegraph Signals," *IEEE Trans. Electron Devices*, vol. 64, no. 10, pp. 4099 - 4105, Aug. 2017. DOI: 10.1109/TED.2017.2742578

- [7] J. Ma, Z. Chai, W. Zhang, J. Zhang, Z. Ji, B. Benbakhti, B. Govoreanu, E. Simoen, L. Goux, A. Belmonte, R. Degraeve, G. Kar, M. Jurczak, "Investigation of pre-existing and generated defects in non-filamentary a-Si/TiO<sub>2</sub> RRAM and their impacts on RTN amplitude distribution," *IEEE Trans. Electron Devices*, vol. 65, no. 3, March 2018. DOI: 10.1109/TED.2018.2792221

- [8] R. Liu, H. Y. Lee, S. Yu, "Analyzing Inference Robustness of RRAM Synaptic Array in Low-Precision Neural Network," in 47th European Solid-State Device Research Conference (ESSDERC), Sept. 2017, DOI: 10.1109/ESSDERC.2017.8066581

- [9] M. Wang, C. Bi, L. Li, S. Long, Q. Liu, H. Lv, N. Lu, P. Sun and M. Liu, "Thermoelectric Seebeck effect in oxide-based resistive switching memory," *Nat. Commun.*, vol. 5, 4598 (2014), DOI:10.1038/ncomms5598

- [10]P. Sun, N. Lu, L. Li, Y. Li, H. Wang, H. Lv, Q. Liu, S. Long, S. Liu and M. Liu, "Thermal crosstalk in 3-dimensional RRAM crossbar array", Sci. Rep., 5:13504, 2015 DOI: 10.1038/srep13504

- [11]P. Sun, L Li, N. Lu, Y. Li, M. Wang, H. Xie, S. Liu and M. Liu, "Physical model of dynamic Joule heating effect for reset process in conductive-bridge random access memory," *J Comput. Electron.*, 2014 13:432–438 DOI: 10.1007/s10825-013-0552-x

- [12]T. H. Park, S. J. Song, H. J. Kim, S. Chung, B. Y. Kim, K. J. Lee, K. M. Kim, B. J. Choi and C. S. Hwang, "Thickness effect of ultra-thin Ta<sub>2</sub>O<sub>5</sub> resistance switching layer in 28 nm-diameter memory cell," *Sci. Rep.*, vol. 5, p. 15965, Nov. 2015. DOI: 10.1038/srep15965

- [13] T. H. Park, H. J. Kim, W. Y. Park, S. G. Kim, B. J. Choi and C. S. Hwang, "Roles of conducting filament and non-filament regions in the Ta<sub>2</sub>O<sub>5</sub> and HfO<sub>2</sub> resistive switching memory for switching reliability," *Nanoscale*, vol. 9, pp. 6010-6019, Mar. 2017. DOI: 10.1039/C7NR01243H

- [14] Y. S. Fan, L. Zhang, D. Crotti, T. Witters, M. Jurczak, and B. Govoreanu, "Direct Evidence of the Overshoot Suppression in Ta<sub>2</sub>O<sub>5</sub>-Based Resistive Switching Memory With an Integrated Access Resistor," *IEEE Electron*

- Device Lett., vol. 36, no. 10, pp. 1027-1029, Oct. 2015. DOI: 10.1109/LED.2015.2470081

- [15] N. Sedghi, H. Li, I.Brunell, K. Dawson, R. Potter, Y. Guo, J.Gibbon, V. Dhanak, W. Zhang, J. Zhang, J. Robertson, S. Hall, P.Chalker, "The role of nitrogen doping in ALD Ta<sub>2</sub>O<sub>5</sub> and its influence on multilevel cell switching in RRAM", *Appl. Phys. Lett.*, 110, 102902, Mar. 2017 DOI: 10.1063/1.4978033

- [16] M. J. Kirton and M. Uren, "Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frequency (1/f) noise," Adv. Phys., vol. 38, no. 4, pp. 367-468, 1989. DOI: 10.1080/00018738900101122

- [17]Y. -B. Kim, S. R. Lee, D. Lee, C. B. Lee, M. Chang, J. H. Hur, M. -J. Lee, G. -S. Park, C. J. Kim, U. -I. Chung, I. -K. Yoo and K. Kim, "Bi-layered RRAM with Unlimited Endurance and Extremely Uniform Switching", in VLSI Symp. Tech. Dig., pp. 52-53, 2011.

- [18]Z. Wei, Y. Kanzawa, K. Arita, Y. Katoh, K. Kawai, S. Muraoka, S. Mitani, S. Fujii, K.Katayama, M. Iijima, T. Mikawa, T. Ninomiya, R. Miyanaga, Y. Kawashima, K. Tsuji, A. Himeno, T. Okada, R. Azuma, K. Shimakawa, H. Sugaya, and T. Takagi; R. Yasuhara, K.Horiba, H. Kumigashira, and M. Oshima, "Highly Reliable TaOx ReRAM and Direct Evidence of Redox Reaction Mechanism", in *IEDM Tech. Dig.*, 2008, DOI: 10.1109/IEDM.2008.4796676]

- [19]T. Ninomiya, T. Takagi, Z. Wei, S. Muraoka, R. Yasuhara, K. Katayama, Y. Ikeda, K. Kawai, Y. Kato, Y. Kawashima, S. Ito, T. Mikawa, K. Shimakawa and K. Aono, "Conductive Filament Scaling of TaOx Bipolar ReRAM for Long Retention with Low Current Operation", in VLSI Symp. Tech. Dig., pp.73–74, 2012, DOI: 10.1109/VLSIT.2012.6242467

- [20] R. Degraeve, A. Fantini, S. Clima, B. Govoreanu, L. Goux, Y.Y. Chen, D.J. Wouters, Ph. Roussel, G.S. Kar, G. Pourtois, S. Cosemans, J.A. Kittl, G. Groeseneken, M. Jurczak and L. Altimime, "Dynamic 'Hour Glass' Model for SET and RESET in HfO2 RRAM," in VLSI Symp. Tech. Dig., June 2012. DOI: 10.1109/VLSIT.2012.6242468

- [21]J. H. Stathis, S. Mahapatra and T. Grasser, "Controversial issues in negative bias temperature instability, *Microelectronics Reliability*, vol. 81, February 2018, Pages 244-251, DOI: 10.1109/VLSIT.2012.6242467

- [22]J.F. Zhang, Z. Ji, W. Zhang, "As-grown-generation (AG) model of NBTI: A shift from fitting test data to prediction," *Microelectronics Reliability*, vol. 80, January 2018, Pages 109-123, DOI: 10.1016/j.microrel.2017.12.035

- [23]T. Grasser, "Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities," *Microelectronics Reliability*, vol. 52, no. 1, pp. 39-70, 2012, DOI: 10.1016/j.microrel.2011.09.002