# As-grown-Generation (A-G) Model for Positive Bias Temperature Instability (PBTI)

Rui Gao, Zhigang Ji, Member, IEEE, Jian Fu Zhang, John Marsland and Wei Dong Zhang

Abstract— Positive Bias Temperature Instability (PBTI) is poised to cause significant degradation to nFETs with deep scaling into nanometers. It is commonly modelled by a power law fitted with measured threshold voltage shift. For the first time, this work shows that such models do not warrant PBTI prediction outside the stress conditions used for the fitting. The underlying cause for this failure is the errors in the extracted power exponent. Based on the understanding of different types of defects, we develop a robust As-grown-Generation (A-G) model and demonstrate its capability for accurate prediction of PBTI under both DC and AC conditions. The generation-induced degradation is found to play a key role. Analysis reveals that, although PBTI is usually smaller than NBTI within the typical test time window, it can exceed NBTI by the end of device lifetime.

Index Terms—PBTI, NBTI, electron traps, HKMG, Reliability

#### I. INTRODUCTION

Ageing has become a critical concern for CMOS technologies as scaling is reaching nano-scale regime [1-8]. Thorough examination and certification of reliable operation throughout the entire application lifetime is required during design. Emerging applications like the Internet of Things (IoT) or wearables usually require strict resiliency and long lifetimes [9]. For example, some biomedical applications require a lifetime of more than 50 years for medical implants. An accurate long-term lifetime prediction is the ultimate task of ageing evaluation.

Bias Temperature Instability (BTI) has been considered as one of the important ageing mechanisms. Extensive efforts have been made in investigating the Negative Bias Temperature Instability (NBTI) for pFETs. The recent use of the multi-layer gate material, however, has led to considerable Positive Bias Temperature Instability (PBTI) for nFETs [1-8]. From the application perspective, it has been reported that PBTI can be the dominating reliability issue for Field-Programmable Gate Arrays (FPGAs) [10] and Ring Oscillators (RO) [11].

Despite industry-wide characterization of various aspects of PBTI phenomena and general consensus regarding its empirical features [1-11], the detailed mechanism of the degradation is not fully understood. Charging of pre-existing traps and/or generating new traps in the dielectric are considered to be the root of PBTI [12]. Due to the lack of well-accepted PBTI model, the classic power law as described in Eqn (1) is widely used for lifetime prediction [13], where A, m and n represent the pre-factor, voltage and time exponents, respectively.

$$\Delta V_{th} = A \cdot V_{gov}^m \cdot t^n \ . \tag{1}$$

Manuscript received MMM DDD, 2018. The review of this paper was arranged by Editor T. Grasser. The test samples were supplied by IMEC. This work was supported by the Engineering and Physical Science Research Council of UK under the grant no. EP/L010607/1.

The authors are with the Department of Electronics and Electrical Engineering, Liverpool John Moores University, L3 3AF, U.K. The corresponding author is Z. Ji. (e-mail: z.ji@ljmu.ac.uk).

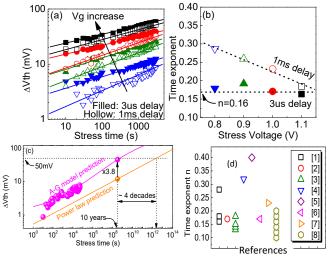

One set of typical PBTI results with different stress gate bias, Vgst, and measurement delays are shown in **Fig.1a**. It is clear that PBTI depends on both Vgst and the delay between stress and measurement. The time exponents are extracted and plotted in **Fig. 1b**. When measured with 1 ms delay, the time exponent declines as voltage increases [1], making it impossible for predicting the long term PBTI under real use conditions [14].

**Fig. 1. (a)** A comparison of PBTI under accelerated stress with 1 ms and 3 μs measurement delay.  $\Delta V$ th is monitored at sensing drain current close to Vth. The symbols are test data and the lines are fitted with power law. **(b)** The fitted time exponents. **(c)** A comparison of test data (symbols) with prediction by the model extracted from the filled symbols in (a) (the lower line) and from the A-G model proposed in this work (the upper line). **(d)** A summary of PBTI time exponent reported by early works [1-8].

The apparent time exponent is close to a constant, when measurement delay is minimized to 3  $\mu s$ . However, the classic power law model extracted from these data failed to predict the PBTI even just 0.1V below the lowest Vgst used for model parameter extraction, as shown in **Fig.1c**. When fitting the measured  $\Delta V th$ , the uncertainties for the time exponent reported by early works in **Fig.1d** [1-8] do not warrant prediction. There is a need for a test-proven method to characterize and model PBTI induced degradation, enabling reliable prediction.

The central objective of this work is to develop a model for long-term PBTI prediction under both AC and DC operation conditions. By separating different types of defects and understanding their kinetics, the proposed model provides excellent predictive capability. The model is then used to assess the long-term PBTI under real use conditions. It is found that the lifetime for DC PBTI can be overestimated by 4 decades by the model extracted from the filled symbols in **Fig.1a**, as shown in **Fig.1c**. In addition, although PBTI-induced degradation can be smaller than NBTI within typical test time window, we will show that long-term PBTI can overtake NBTI.

The paper is organized as follows: The details of devices and experiments are described in Section II. Section III shows how different types of defects can be experimentally separated. Based on the extracted kinetics for each type of defect, the A-G model for PBTI is proposed and validated under both DC and AC operation conditions in Section IV. Section V discusses the long-term PBTI-induced degradation under real use conditions and Section VI concludes this paper.

### II. DEVICES AND EXPERIMENT

nFinFETs fabricated using a Hf-based high-k oxide stack and a metal gate are used to demonstrate the proposed model. An equivalent oxide thickness of 1 nm was obtained by adopting a thin TiN metal gate, inducing Si in-diffusion, and reducing the interfacial oxide thickness [15]. Fast measurement of Id-Vg within 3 μs on Keysight B1530 is used in this work [16]. The threshold voltage degradation is monitored by sensing at a constant Id of 500nA\*W/L around threshold voltage. Unless otherwise specified, temperature is 125 °C.

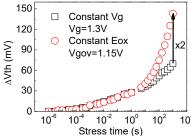

Although PBTI is considered as an electric-field driven phenomenon [17], the tests in literatures were usually performed under constant Vgst against stress time. The underlying assumption is that the total degradation,  $\Delta$ Vth, is much smaller than the applied voltage and thus the change in electric field over the dielectric, Eox, during the stress can be neglected. **Fig.2** compared the PBTI degradation under the constant-Vgst and constant-Eox condition. The constant-Eox is maintained by adding  $\Delta$ Vth measured in the last step to the Vgst(time=0). Although the difference in Fig.2 is small initially, it becomes considerable as the  $\Delta$ Vth increases for longer stress time. In this work, tests were carried out under constant-Eox, unless otherwise specified.

Fig. 2. A comparison between constant Vgst and constant Eox stress for PBTI.

## III. DEFECTS UNDER PBTI STRESS

There is no consensus on the defects and mechanisms of PBTI. Some groups ascribe the degradation to filling pre-existing electron traps, such as oxygen vacancies in the high-k layer [18]. Other groups proposed that stress-induced defect generation may also makes considerable contribution [13,19,20]. In order to model PBTI, it is important to separate different types of defects and model the kinetics of each type separately. In the following, we will show that through separating different types of defects experimentally, accurate PBTI model with predictive capability can be extracted.

A. Generated Defects (GD): characterization and modelling

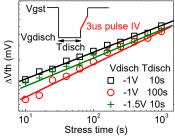

For NBTI, it is reported that GD can depend on measurement conditions (e.g. discharging time, Tdisch, and the discharge

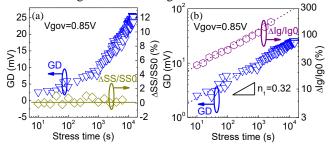

voltage, Vgdisch) [21]. This is also the case for the GD induced by PBTI. One example is shown in **Fig.3**: if different Tdisch/Vgdisch is used, the extracted GD kinetics varies. For NBTI, this is because not only as-grown traps, but also some GDs, are discharged [21]. By applying the Stress-Discharging-Recharging (SDR) technique, the discharged GDs are refilled, allowing all GDs being captured. Using all GDs obtained in this way, a reliable power law is obtained, which is independent of measurement conditions [21].

Fig. 3. PBTI-induced GD generation after applying different discharge voltage, Vgdisch, for different discharge time, Tdisch. The waveform for the measurement is shown in the inset.

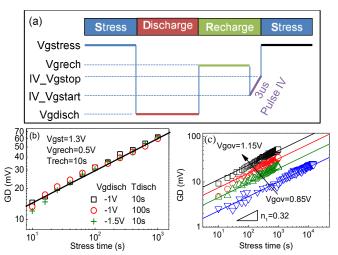

In this work, the SDR technique is applied for PBTI with the waveform shown in **Fig.4a**. The details about this technique can be found in [21]. As shown in **Fig.4b**, the dependence of GD extraction on Vgdisch and Tdisch are removed with SDR.

To study the dependence on stress conditions, GD were measured under different stress overdrive voltages, Vgov=Vgst-Vth. As in **Fig.4c**, they are well described by,

$$GD = g_1 \cdot V_{gov}^{m1} \cdot t^{n_1}. \quad (2)$$

It is worth of noting that the extracted GD has a Vgov-independent time exponent of 0.32. This is larger than that extracted from the total  $\Delta V$ th in **Fig.1a** and most of the values reported by early works [1-8] in **Fig.1d**. It is also larger than the ~0.2 reported for NBTI [21]. From a circuit point of view, the large time exponent for PBTI can impact the long-term reliability, as will be further elaborated in Section V.

The atomic structure of GD remains unknown and the electrical measurement used here does not give direct information on it. To test if GD is interface states, we study the sub-threshold swing (SS) against stress time. An increase in SS is considered as an indicator for interface states and/or border traps generation [7,22]. As shown in **Fig.5a**, with a substantial GD, there is little change in the SS. This indicates that the GD is oxide traps, rather than interface states.

To further explore the defects responsible for GD, Fig.5b shows that GD and stress-induced-leakage current (SILC) have the same time exponent. This strong correlation supports that they originate from the same generation process. It is reported that the defects responsible for the intrinsic breakdown are the generated electron traps, rather than hole traps [23]. Hydrogenous species has been proposed to cause the generation [24] and one may speculate that the generated defect contains hydrogen. Whether it contains hydrogen before the generation is not known. It is commonly accepted that SILC and intrinsic breakdown are caused by the same types of defects, which are randomly distributed in the oxide [25]. For intrinsic breakdown, one may speculate that foreign elements are not needed in the structure before defect generation.

**Fig. 4. (a)** The Stress-Discharging-Recharging (SDR) test procedure for GD extraction. **(b)** The PBTI-induced GD extracted by SDR under different Vgdisch and Tdisch. **(c)** GD kinetics under different stress Vgov. Time exponents are ~0.32 and independent of Vgov. The symbols are from the SDR measurement and the lines are he fitted power law, i.e. Eqn (2).

## B. Pre-existing defects: characterization and modelling

Pre-existing defects originate from the fabrication imperfectness. By definition, their charging and discharging kinetics will not be affected by the device's stress history. Therefore, they can be readily characterized by using heavily stressed devices. Here significant amount of GDs have already been generated, so that there is little further generation in the following pre-existing defect characterization. This suppresses the interference of trap generation on the characterization.

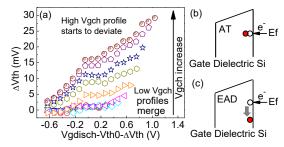

To understand pre-existing traps, their discharge properties are studied. For each set of symbols in **Fig.6a**, traps were first charged under a constant Vgch-Vth and the highest point represents the charged level. The trapped charges were then progressively discharged by stepping Vgdisch-Vth in the negative direction and each more negative Vgdisch-Vth step gives one lower point. After completing one discharge sequence, a higher Vgch-Vth is applied to charge the traps to a higher level, followed by a new discharge sequence to give the next set of symbols in **Fig.6a**.

When Vgch-Vth is low, the discharge profiles are independent of Vgch-Vth, i.e. they overlap well. However, when Vgch-Vth increases further, they deviate from each other and are higher for higher Vgch-Vth. This is because there are two different types of electron traps, as illustrated in **Fig. 6b&c.** One of them captures an electron without changing its energy level (**Fig. 6b**) and is named as As-grown-Traps (ATs). In contrast, after capturing one electron, the energy level of the other type shifts downwards from their ground/neutral state (**Fig. 6c**). This is named as Energy-Alternating-Traps (EADs).

Under low Vgch-Vth, charging is dominated by ATs. Since their energy level does not change after charging, their discharge profiles overlap. Under high Vgch-Vth, however, both ATs and EADs were charged. As the charged EADs have lowered its energy level, they do not discharge immediately when Vgdisch-Vth starts reducing from the Vgch-Vth. This results in the higher discharge profiles for higher Vgch-Vth in **Fig.6a**. EADs can only be neutralized when their lowered

charge states are reached under more negative Vgdisch-Vth. In contrast, the additional ATs charged under a higher Vgch-Vth will be discharged as soon as Vgdisch-Vth is lowered.

Fig. 5. (a) A comparison of GD and SS against stress time. Negligible  $\Delta$ SS/SS0 indicates little interface states generation in PBTI. (b) A comparison of kinetics for GD and SILC. The SILC current is taken at Vgov of 0.85V.

**Fig. 6 (a).** The discharge profiles of pre-existing traps using the method in ref 26. The traps were first charged under Vgch=Vg-Vth=0.3 V and the subsequent discharging was recorded to give the lowest set of symbols. Vgch was then raised to charge the traps again, following by discharge for the next set of symbols. This charge-discharge sequence was repeated until Vgch reached 1.1V, which corresponds to the highest set of symbols. Charging of AT (b) and EAD (c): The energy level after charging does not change for AT, but lowers for EAD.

Based on the above, AT can be extracted by adding the additional discharge for two consecutive Vgch-Vth levels to the overlapping discharge profile, as illustrated in Fig. **7a**: starting with the discharge profile at the lowest Vgch-Vth in which only AT traps are involved, the additional discharging trace under the next charging level is shifted down to align these two curves at the last point of the lower curve. By following this procedure up to the highest Vgch-Vth, the distribution of AT is extracted for the whole voltage range. Once AT is known, EAD can then be extracted by subtracting AT, as shown in **Fig. 7b**. AT dominates initially, while EAD follows a power law. Further details can be found from our early works [26, 27].

**Fig. 7. (a)** The extraction of ATs. For each higher set of symbols, they cover an additional voltage range, as represented by the short solid lines. Using the lowest set of symbols as the base, these short lines were shifted downward until they all joined together to give a single profile over the whole voltage range, which are the ATs. The details are given in refs. 26&27. **(b)** An example of separating EADs from ATs. After ATs were extracted, EADs were obtained by subtracting ATs.

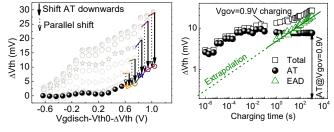

The kinetics for EAD and AT under different overdrive voltages are extracted and shown in **Figs.8a&b**, respectively. ATs clearly saturates, confirming their 'As-grown' nature. Empirically, the saturation level, AT<sub>sat</sub>, can be well modelled with Eqn (3) and its charging kinetics with Eqn (4) [28],

$$AT_{sat} = p_1 \cdot \exp(p_2 \cdot V_{gov}), \quad (3)$$

$$AT = AT_{sat} \cdot \left[1 - \exp\left(-\frac{tch}{\tau}\right)^{\gamma}\right], \quad (4)$$

where p1, p2,  $\tau$  and  $\gamma$  are constants and extracted from the test data. EADs follow a power law with Eqn (5).

$$EAD = g_2 \cdot V_{gov}^{m_2} \cdot t^{n_2}$$

, (5)

where  $g_2$ ,  $m_2$ , and  $n_2$  are fitting parameters. What is worth of noting is that, although both EAD and GD follow power law, their time and voltage exponents are quite different (see Table I) and they must be modeled separately, therefore.

Fig. 8. (a) EAD and (b) AT charging kinetics under different Vgov.

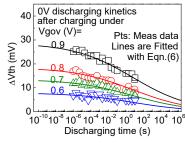

As most circuits operate under AC condition, pre-existing traps charge-discharge dynamically. The discharging is directly measured and shown in **Fig. 9**. It can be described by the universal recovery curve in Eqn. (6) [29],

$\Delta Vth_{tdisch} = \Delta Vth_{tdisch=0} \cdot \left(1 + B \cdot T_{disch}^{\beta}\right)^{-1}, \ \ (6)$  where B and  $\beta$  are fitting parameters.

**Fig. 9.** The measured discharging kinetics of the pre-existing traps (Symbols) and the fitted lines with Eqn (6).

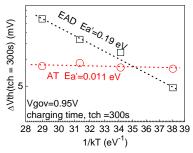

We further explored the apparent activation energy, Ea', of AT and EAD, as shown in Fig.10. When compared with AT, EAD has a much larger Ea', suggesting its thermally activated process. One may speculate that the structure of EAD relaxes following trapping: capturing one electron could lead to re-arrangement of microscopic structure in terms of local bond length and angle, which in turn lowered the energy level [29, 30]. In contrast, little change in energy levels of AT after trapping indicates little structure relaxation. This, together with the different trapping kinetics in Fig.8 and the different temperature dependence in Fig. 10, support that ATs and EADs are different types of defects.

AT and EADs are also clearly different from GD: (i) There is no GD in fresh devices; (ii) Majority of GD will not discharge when AT and EAD are neutralized (see **Fig.7a**), indicating that

GD has deeper energy levels; (iii) They have different kinetics. These differences should be taken into account for atomistic modelling in future.

**Fig. 10.** The Arrhenius plot for AT and EAD. To extract the apparent activation energy, Ea', for each type of defect, both ATs and EADs are measured after charging up for 300s at different temperature.

#### IV. A-G MODEL AND VALIDATION

#### A. Model construction

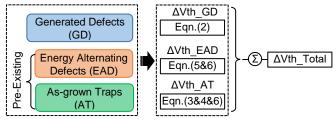

Based on the above knowledge of defects, an A-G model can be built with the architecture in **Fig.11.** The model parameters for each defect are shown in Table I. They were obtained through fitting the data of short Vg-accelerated DC stress, as described in Section III. For a given set of inputs: Vg, frequency, and duty factor, the total  $\Delta V$ th equals to the sum of all charged defects.

Fig. 11. The AG model framework.

**TABLE I** A-G model parameters extracted from short Vg-accelerated DC stress described in Section III.

|              | GD    |      | EAD   |      | AT         |      |   |      | Discharge |      |

|--------------|-------|------|-------|------|------------|------|---|------|-----------|------|

| Param -eters | $g_1$ | 2.75 | $g_2$ | 7.28 | <b>p</b> 1 | 0.29 | τ | 2e-4 | В         | 0.79 |

|              | $m_1$ | 5.23 | $m_2$ | 3.28 | p2         | 3.55 | γ | 1    | β         | 0.13 |

|              | $n_1$ | 0.32 | $n_2$ | 0.2  |            |      |   |      |           |      |

## B. Model validation for predictive capability

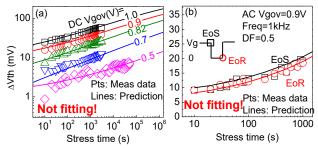

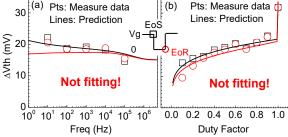

The proposed A-G model is of value only if it can predict the PBTI degradation at the low use bias and longer time, outside the range used for fitting the model parameters. The constant-Eox paradigm is necessary for model parameter extraction, but the circuits operate under constant-Vg condition. To test the predictive capability of A-G model, PBTI degradation under several constant Vgst conditions were measured. Specifically, a relatively long test time is used for the lowest Vgst, which is limited by the minimum-measurable degradation. ΔVth under constant Vg is predicted by the model framework in Fig.11 with Eqns (2-6). The excellent agreement between measurement and prediction for both DC and AC PBTI validates the predictive capability of the A-G model, as shown in Fig.12a&b. The frequency and duty factor dependences can also be predicted well in Fig.13a&b.

**Fig. 12.** A comparison of measurement and prediction with the A-G model for: (a) DC constant voltage stress, and (b) AC stress under Vgov =0.9V, 1kHz DF=0.5. For both DC and AC stresses, Vgov=Vgst-Vth(time=0) and Vgst was a constant for each set of symbols, i.e. Vgst was not adjusted for  $\Delta$ Vth. These test data were not used for fitting the model parameters.

**Fig. 13.** Validation of prediction capability of AG model under different frequency (a) and Duty Factor (b). Vgov of 0.9V is used.

It is worth of pointing out that this good agreement is not from the fitting. This is because the model parameter extraction is based on the data from short-term DC constant-Eox tests, while the test data under constant-Vgst in Figs.12&13 were not used for the fitting. Indeed, the lowest Vgov=0.5 V in Fig.12a is well outside the range of stress biases used to extract the model parameter in Fig.4c. Therefore, PBTI cannot be modelled reliably by simply fitting test data with a power law and a defect based A-G model should be used.

# V. IMPLICATION TO PRACTICAL DEVICE OPERATION

Based on the established A-G model, PBTI can be predicted under operation condition (solid lines in **Fig. 1c**). If the prediction is made from the classical power law fitted with the total  $\Delta V$ th (the filled symbols in **Fig.1a**), there is a clear gap between the measured data and the prediction (the lower line in **Fig.1c**). In the short term, this gap may appear insignificant (~2mV), but it leads to an overestimation of lifetime by over 4 orders of magnitude.

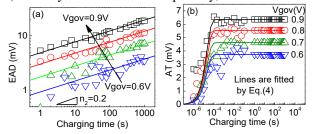

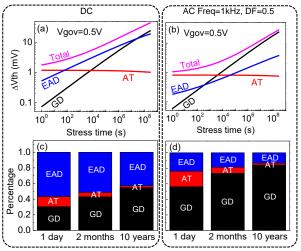

The contribution from each type of defect under DC and AC real use conditions is assessed in **Fig. 14a-d. Fig. 14a** shows PBTI kinetics under DC condition. ATs reduce slightly for longer time, because the surface potential varies when GD and EAD increases under a constant Vg. Although AT becomes insignificant by the end of device lifetime, they must be taken into account during the PBTI test, so that an accurate time exponent can be extracted for GDs and EADs. EADs are one major component at both short and long time for DC PBTI.

Due to their larger time exponent, GDs increase faster than EADs and overtake EADs when approaching 10 years. Quantitatively, **Fig. 14c** shows the relative contributions of each defect at 1 day, 2 months and 10 years. By the end of 10 years, the contribution from GD increases to ~60%.

The degradation kinetics under AC PBTI condition is shown in **Fig. 14b**. Compared with DC, PBTI under AC is smaller. This is mainly due to the reduction of EAD, which discharges effectively during Vg=0 phase. On the other hand, GDs are similar for both DC and AC. At 10 years, GDs contribute to over 80% of the total degradation, as shown in **Fig. 14d**.

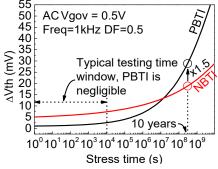

In recent years, most of test data report that PBTI is smaller than NBTI under the same electric field [31, 32]. The test time, however, is limited typically to less than 10<sup>4</sup> sec. In order to compare the long term NBTI and PBTI, we extracted and validated the A-G model for both of them from the same wafer. The predicted degradations under real-use condition are compared in **Fig. 15.** It is clear that when test time is short (e.g. <10k), NBTI is indeed larger. At 10 years, however, PBTI overtakes NBTI by a factor of 1.5, because of the time exponent of GD is ~0.32 for PBTI and ~0.2 for NBTI.

**Fig. 14.** Kinetics of different components against stress time under DC (a) and 1kHz (b) PBTI stress. The normalized contribution of different components under different stress time is given in (c) DC & (d) AC stress.

**Fig. 15.** A comparison of NBTI and PBTI under typical use bias of Vgov=0.5 V. Both are calculated from A-G model with parameters extracted from p- and n- FETs on the same wafer.

## VI. CONCLUSIONS

In this work, for the first time, we demonstrate that the common power law model extracted from  $\Delta V$ th do not warrant predicting PBTI outside the test conditions used for fitting model parameters. An A-G model is proposed, which can predict PBTI not only under DC but also under AC conditions with different frequency and duty factor. This excellent predictive capability is validated through comparison between measured data and the prediction from the model. Further

analysis based on the established model reveals that although PBTI can be smaller than NBTI within typical test time window, it becomes larger towards the end of device lifetime due to its larger time exponent. The simplicity of the model and its parameter extraction makes the proposed methodology favorable for future process qualification and circuit level reliability evaluation.

#### REFERENCES

- [1] D. P. Ioannou, S. Mitt, and G. LaRosa, "Positive bias temperature instability effects in advanced high-k metal gate NMOSFETs," in Proc. IEEE IRW Final Rep., 2008, pp. 55-57. DOI: 10.1109/IRWS.2008.4796085.

- [2] A. Kerber, S. A. Krishnan, and E. A. Cartier, "Voltage Ramp Stress for Bias Temperature Instability Testing of Metal-Gate/High-Stacks," IEEE Electron Device Lett., vol. 30, no. 12, pp. 1347-1349, 2009. DOI: 10.1109/LED.2009.2032790.

- [3] G. Krause, R. Geilenkeuser, M. Trentzsch, F. Graetsch, and L. Herrmann, "Application of fast wafer-level reliability PBTI tests for screening of High-k/Metal Gate process splits," in Proc. IEEE IRW Final Rep., 2009, pp. 66-69. DOI: 10.1109/IRWS.2009.5383032.

- [4] C. Schlünder, H. Reisinger, S. Aresu, and W. Gustin, "On the PBTI degradation of pMOSFETs and its impact on IC lifetime," in Proc. IEEE IRW Final Rep., 2011, pp. 7-11. DOI: 10.1109/IIRW.2011.6142576.

- [5] K. Rott, H. Reisinger, S. Aresu, C. Schlünder, K. Kölpin, W. Gustin, and T. Grasser, "New insights on the PBTI phenomena in SiON pMOSFETs," Microelectron. Rel., vol. 52, no. 9, pp. 1891-1894, 2012. DOI: 10.1016/j.microrel.2012.06.015.

- [6] J. Yang, M. Masuduzzaman, K. Joshi, S. Mukhopadhyay, J. Kang, S. Mahapatra, and M. A. Alam, "Intrinsic correlation between PBTI and TDDB degradations in nMOS HK/MG dielectrics," in Proc. IRPS, 2012, pp. 5D. 4.1-5D. 4.7. DOI: 10.1109/IRPS.2012.6241855.

- [7] N. H.-H. Hsu, J.-W. You, H.-C. Ma, S.-C. Lee, E. Chen, L. Huang, Y.-C. Cheng, Y.-C. Cheng, and I. Chen, "Intrinsic hot-carrier degradation of nMOSFETs by decoupling PBTI component in 28nm high-k/metal gate stacks," in Proc. IRPS, 2012, pp. XT. 13.1-XT. 13.4. DOI: 10.1109/IRPS.2012.6241943.

- [8] W. Mizubayashi, T. Mori, K. Fukuda, Y. Liu, T. Matsukawa, Y. Ishikawa, K. Endo, S. O'uchi, J. Tsukada, and H. Yamauchi, "Accurate prediction of PBTI lifetime for N-type fin-channel tunnel FETs," in IEDM Tech. Dig., 2014, pp. 34.3. 1-34.3. 4.DOI: 10.1109/IEDM.2014.7047167.

- [9] D. Blaauw, D. Sylvester, P. Dutta, Y. Lee, I. Lee, S. Bang, Y. Kim, G. Kim, P. Pannuto, and Y.-S. Kuo, "IoT design space challenges: Circuits and systems," in *VLSI Symp. Tech. Dig.*, 2014, pp. 1-2. DOI: 10.1109/VLSIT.2014.6894411.

- [10] C. S. Chen and J. T. Watt, "Characterization and simulation of NMOS pass transistor reliability for FPGA routing circuits," in Proc. ICMTS, 2013, pp. 216-220. DOI: 10.1109/ICMTS.2013.6528175.

- [11] D. P. Ioannou, S. Mittl, and D. Brochu, "Burn-in stress induced BTI degradation and post-burn-in high temperature anneal (Bake) effects in advanced HKMG and oxynitride based CMOS ring oscillators," in Proc. IRPS, 2012, pp. 5C. 2.1-5C. 2.5. DOI: 10.1109/IRPS.2012.6241849.

- [12] M. Duan, J. F. Zhang, Z. Ji, W. D. Zhang, D. Vigar, A. Asenov, L. Gerrer, V. Chandra, R. Aitken, and B. Kaczer, "Insight Into Electron Traps and Their Energy Distribution Under Positive Bias Temperature Stress and Hot Carrier Aging," IEEE Trans. Electron Devices, vol. 63, no. 9, pp. 3642-3648, 2016. DOI: 10.1109/TED.2016.2590946.

- [13] X. Garros, L. Brunet, M. Rafik, J. Coignus, G. Reimbold, E. Vincent, A. Bravaix, and F. Boulanger, "PBTI mechanisms in La containing Hf-based oxides assessed by very Fast IV measurements," in IEDM Tech. Dig., 2010, pp. 4.6. 1-4.6. 4. DOI: 10.1109/IEDM.2010.5703297.

- [14] Z. Ji, L. Lin, J. F. Zhang, B. Kaczer, and G. Groeseneken, "NBTI lifetime prediction and kinetics at operation bias based on ultrafast pulse measurement," IEEE Trans. Electron Devices, vol. 57, no. 1, pp. 228-237, 2010. DOI: 10.1109/TED.2009.2037171.

- [15] L, Ragnarsson, Z. Li, J. Tseng, T. Schram, E. Rohr, M. J. Cho, T. Kauerauf, T. Conard, Y. Okuno, B. Parvais, P. Absil, S. Biesemans, and T. Y. Hoffmann, "Ultra low-EOT (5A) gate-first and gate-last high performance CMOS achieved by gate-electrode optimization," in IEDM Tech. Dig., 2009, pp. 1-4. DOI: 10.1109/IEDM.2009.5424254.

- [16] Z. Ji, J. F. Zhang, and W. Zhang, "A New Mobility Extraction Technique Based on Simultaneous Ultrafast Id-Vg and Ccg-Vg Measurements in

- MOSFETS," IEEE Trans. Electron Devices, vol. 59, no. 7, pp. 1906-1914, 2012. DOI: 10.1109/TED.2012.2196519.

- [17] M. Cho, J. D. Lee, M. Aoulaiche, B. Kaczer, P. Roussel, T. Kauerauf, R. Degraeve, J. Franco, L, x00C, Ragnarsson, and G. Groeseneken, "Insight Into N/PBTI Mechanisms in Sub-1-nm-EOT Devices," IEEE Trans. Electron Devices, vol. 59, no. 8, pp. 2042-2048, 2012. DOI: 10.1109/TED.2012.2199496.

- [18] T. Grasser, B. Kaczer, and W. Goes, "An energy-level perspective of bias temperature instability," in Proc. IRPS, 2008, pp. 28-38. DOI: 10.1109/RELPHY.2008.4558859.

- [19] E. Cartier and A. Kerber, "Stress-induced leakage current and defect generation in nFETs with HfO 2/TiN gate stacks during positive-bias temperature stress," in Proc. IRPS, 2009, pp. 486-492. DOI: 10.1109/IRPS.2009.5173301.

- [20] F. Crupi, R. Degraeve, A. Kerber, D. H. Kwak, and G. Groeseneken, "Correlation between Stress-Induced Leakage Current (SILC) and the HfO/sub 2/bulk trap density in a SiO/sub 2//HfO/sub 2/stack," in Proc. IRPS, 2004, pp. 181-187. DOI: 10.1109/RELPHY.2004.1315321.

- [21] R. Gao, A. B. Manut, Z. Ji, J. Ma, M. Duan, J. F. Zhang, J. Franco, S. W. M. Hatta, W. D. Zhang, and B. Kaczer, "Reliable Time Exponents for Long Term Prediction of Negative Bias Temperature Instability by Extrapolation," IEEE Trans. Electron Devices, vol. 64, no. 4, pp. 1467-1473, 2017. DOI: 10.1109/TED.2017.2669644.

- [22] D. Ang, G. Du, Y. Hu, S. Wang, and C. Ng, "Energy distribution and electrical characteristics of NBTI induced Si/SiON interface states," in *Proc. IRPS*, 2008, pp. 737-738. DOI: 10.1109/RELPHY.2008.4559014.

- [23] W. D. Zhang, J. F. Zhang, C. Z. Zhao, M. H. Chang, G. Groeseneken, and R. Degraeve, "Electrical signature of the defect associated with gate oxide breakdown." *IEEE Electron Dev.Lett.*, vol.27, no.5, pp.393-395, 2006. DOI: 10.1109/LED.2006.873384.

- [24] D. J. DiMaria and J. H. Stathis, "Anode hole injection, defect generation, and breakdown in ultrathin silicon dioxide films," *J. Appl. Phys.*, vol. 89, no.9, pp.5015-5024, 2001. DOI: 10.1063/1.1363680.

- [25] R. Degraeve, G. Groeseneken, R. Bellens, J. L. Ogier, M. Depas, P. J. Roussel, and H. E. Maes, "New insights in the relation between electron generation and the statistical properties of oxide breakdown," *IEEE Trans. Electron Dev.*, vol. 45, no. 4, pp.904-911, 1998. DOI: 10.1109/16.662800.

- [26] Z. Ji, X. Zhang, J. Franco, R. Gao, M. Duan, J. F. Zhang, W. D. Zhang, B. Kaczer, A. Alian, and D. Linten, "An investigation on border traps in III–V MOSFETs with an In 0.53 Ga 0.47 As channel," IEEE Trans. Electron Devices, vol. 62, no. 11, pp. 3633-3639, 2015. DOI: 10.1109/TED.2015.2475604.

- [27] P. Ren, R. Gao, Z. Ji, H. Arimura, J. F. Zhang, R. Wang, M. Duan, W. Zhang, J. Franco, S. Sioncke, D. Cott, J. Mitard, L. Witters, H. Mertens, B. Kaczer, A. Mocuta, N. Collaert, D. Linten, R. Huang, A. V. Y. Thean, and G. Groeseneken, "Understanding charge traps for optimizing Si-passivated Ge nMOSFETs," in VLSI Symp. Tech. Dig., 2016, pp. 1-2. DOI: 10.1109/VLSIT.2016.7573367.

- [28] S. Zafar, A. Callegari, E. Gusev, and M. V. Fischetti, "Charge trapping related threshold voltage instabilities in high permittivity gate dielectric stacks," *J. Appl. Phys.*, Vol. 93, No. 11, pp.9298-9303, 2003. DOI: 10.1063/1.1570933

- [29] T. Grasser, "Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities," *Microelectronics Reliability*, vol. 52, pp. 39–70, 2012. DOI: 10.1016/j.microrel.2011.09.002.

- [30] D. Liu, Y. Guo, L. Lin, and J. Robertson, "First-principles calculations of the electronic structure and defects of Al2O3," J. Appl. Phys., vol. 114, no. 8, pp. 083704-1 - 083704-5, 2013. DOI: 10.1063/1.4818475.

- [31] V. P.-H. Hu, M.-L. Fan, C.-Y. Hsieh, P. Su, and C.-T. Chuang, "FinFET SRAM cell optimization considering temporal variability due to NBTI/PBTI, surface orientation and various gate dielectrics," *IEEE Trans. Electron Devices*, vol. 58, no. 3, pp. 805-811, 2011. DOI: 10.1109/TED.2010.2099661.

- [32] B. P. Linder, A. Dasgupta, T. Ando, E. Cartier, U. Kwon, R. Southwick, M. Wang, S. Krishnan, M. Hopstaken, and M. Bajaj, "Process optimizations for NBTI/PBTI for future replacement metal gate technologies," in *Proc. IRPS*, 2016, pp. 4B-1-1-4B-1-5. DOI: 10.1109/IRPS.2016.7574532.