# TDDB mechanism in a-Si/TiO<sub>2</sub> non-filamentary RRAM device

J. Ma, Z. Chai, W. Zhang, J. F. Zhang, J. Marsland, B. Govoreanu, R. Degraeve, L. Goux, G. S. Kar

Abstract—Mechanisms of time-dependent-dielectric-breakdown (TDDB) in non-filamentary a-Si/TiO<sub>2</sub> RRAM cell (a-VMCO) have been examined in this work, including defects generation in the grain boundary, defects clustering and different defects generation rates in a-Si and TiO2 layers. The unique feature of a bimodal Weibull distribution at low resistance state (LRS) and a single shallow slope distribution at high resistance state (HRS) cannot be explained by the above mechanisms. By using a combination of constant-voltage-stress (CVS), time-to-breakdown Weibull distribution and random-telegraph-noise (RTN) based defect profiling in devices of various sizes, layer thickness and processes, it is revealed that the defect profile is modulated when switching between HRS and LRS and the correlation of defect profile modulation with local defect generation rate can explain the difference in Weibull distributions at HRS and LRS. The transition from bimodal distribution at LRS to a single-steepslope with thinner a-Si layer, and the good area scaling of Weibull distribution at HRS but not at LRS, can also be explained. The critical layers affecting the TDDB in a-VMCO are identified, providing useful guidance for device performance improvement.

Index Terms—Time-to-breakdown, TDDB, Si, TiO<sub>2</sub>, a-VMCO, Dielectrics, RRAM, Weibull Distribution, RTN.

#### I. INTRODUCTION

esistive switching memory is a promising emerging non-volatile memory [1-8]. Good characteristics have been achieved in various binary metal-oxide based devices (RRAM), such as NiO [2],  $TiO_2$  [3, 4],  $HfO_2$  [5, 6], and Ta<sub>2</sub>O<sub>5</sub> [7, 8]. In filamentary type RRAM, forming operation is normally needed to create a conductive filament first, and the switching between high resistance state (HRS) and low resistance state (LRS) can be considered as a progressive 'soft breakdown' and "recovery" process, controlled by oxygen vacancy modulation in the filament constriction [2-10]. Reliability issues in these devices such as retention, endurance and variability have been extensively studied [5-10]. Timedependent-dielectric-breakdown (TDDB) has also been used to investigate the forming, switching and breakdown mechanisms [11-13]. Degradation of the critical filamentary constriction region will lead to endurance failure such as memory state stuck at either HRS or LRS or breakdown [6-13].

In contrast, resistance switching in the non-filamentary type RRAM has been attributed to the uniform defect profile modulation at the interface either with the electrode [14] and/or between two dielectric layers [15-16]. The vacancy modulated conductive oxide RRAM (a-VMCO) has demonstrated good

Manuscript received MM/DD/2018. This work was supported by the EPSRC of U.K. under Grants EP/M006727/1 and EP/S000259/1. The review of this paper was arranged by Editor X. Y.

J. Ma, Z. Chai(Z.Chai@ljmu.ac.uk), W. Zhang (W.Zhang@ljmu.ac.uk), J. F. Zhang, J. Marsland are with the Department of Electronics and Electrical Engineering, Liverpool John Moores University, L3 3AF Liverpool, U.K. B. Govoreanu, R. Degraeve L. Goux, and G.S.Kar are with IMEC, 3001 Leuven, Belgium.

non-filamentary properties, such as area-dependent resistance switching, larger than ×10 resistance window, self-rectifying and self-compliance [15-16]. Its reliability issues such as retention, noise and the differences from the filamentary RRAM have been discussed in detail [17]. Further optimization was explored, for example, by using higher set/reset voltage to improve the resistive window, but this leads to degradation and causes device breakdown [18]. The breakdown mechanism in a-VMCO RRAM has not been characterized in detail yet.

The time-to-breakdown Weibull plot has been extensively used to analyze the dielectric breakdown mechanism [19-21]. In addition to the well accepted percolation model with random defect generation, further investigations have been carried out recently to explain the bimodal Weibull distribution observed in nanoscale dielectrics, for example, by the localized defect generation in grain boundaries of polycrystalline materials [22-24], defect clustering effect in SiO<sub>2</sub> or high-k oxide materials [12], or different defect generation rates in dual dielectric layers [25,26]. In this work, we will investigate the TDDB mechanism in non-filamentary a-VMCO by using the constant voltage stress (CVS) combined with Weibull plot and random telegraph noise (RTN) based defect profiling technique. In the following sections, its unique features of TDDB dependence on voltage polarity, dielectric layer thickness and cell areas will be studied to identify the breakdown mechanism.

## II. DEVICES AND EXPERIMENTS

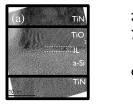

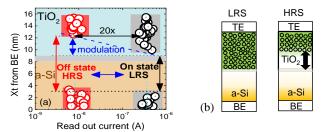

As shown in **Fig. 1a**, a-VMCO devices were fabricated with a CMOS-compatible process: The active stack consists of an 8 nm PVD amorphous silicon (a-Si) layer and on top of it, an 8nm ALD TiO<sub>2</sub> layer crystallized in anatase phase [15]. The stack is sandwiched by TiN bottom electrode (BE) and top electrode (TE). The TiO<sub>2</sub> layer serves as resistive switching layer and the a-Si acts as the barrier and oxygen-scavenging layer.

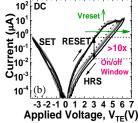

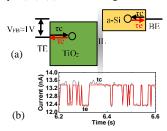

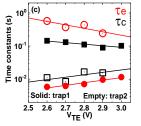

The a-VMCO features forming free, self-compliance, and analogue switching characteristics [16], as shown in the DC I-V characteristics in Fig. 1b. The on/off window can be enhanced by increasing the reset voltage (V<sub>reset</sub>), but further increase will lead to degradation and cause hard breakdown [17]. In order to investigate the defects' profile and their impact, RTN measurements are carried out at incremental biases for both LRS and HRS, and the typical RTN measurement procedure and results are given in Fig. 2a-2c. Details of the defects and profile extraction methods and considerations can be found in refs. [18, 28]. Constant voltage stresses (CVS) are carried out to characterize the TDDB performance, which is interrupted at pre-set internals by RTN measurements to analyze the defect profiles. For each bias condition, 40-50 devices with the same size were stressed and the current was measured until reaching hard breakdown. To avoid the resistive switching during stress, CVS were applied with negative bias polarity when the cell is intrinsically at LRS, and with positive

polarity after it has been reset to HRS first. Table 1 summarizes the devices being used.

Fig. 1 (a) TEM cross-section of a-VMCO RRAM with 1-nm SiOx interfacial layer (IL). (b) DC switching I-V at increased Vreset. Vread=3V. Cell size 40nm.

Fig. 2 (a) Illustration of the energy band diagram of a-VMCO. (b) A typical RTN signal. (c) Typical RTN time constants extracted against V<sub>TE</sub> [18, 28].

| Table 1: Summary of devices used in this work |    |                               |                                 |

|-----------------------------------------------|----|-------------------------------|---------------------------------|

| Sample                                        | #  | Layer & thickness             | Process                         |

|                                               | W1 |                               | Standard                        |

| Standard a-                                   | W2 | 8nmTiO <sub>2</sub> /8nm a-Si | Improved PDA                    |

| VMCO RRAM                                     | W3 |                               | Additional pre-TiO <sub>2</sub> |

|                                               |    |                               | deposition cleaning             |

| a-Si MSM                                      | W4 | 5nm a-Si                      | Standard                        |

| Thin a-VMCO                                   | W5 | 8nmTiO <sub>2</sub> /5nm a-Si | Standard                        |

| Thin a-VMCO                                   | W6 | 8nmTiO <sub>2</sub> /4nm a-Si | Standard                        |

| Thin a-VMCO                                   | W7 | 8nmTiO <sub>2</sub> /3nm a-Si | Standard                        |

All the above samples have sizes ranging from 40nm\*40nm to 170nm\* 170nm. Specific sizes used in each figure are given in the respective captions. More detailed device information can be found in refs. [15-18].

#### III. RESULTS AND DISCUSSIONS

#### A. Polarity and material dependent TDDB

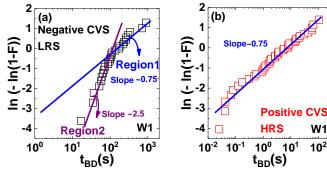

TDDB of the standard a-VMCO cell with 8nm a-Si/8nm TiO<sub>2</sub> stack (W1/P1) is examined first. The time-to-failure at hard breakdown, t<sub>BD</sub>, are extracted and its Weibull plot is shown in Fig.3a&b at opposite stress polarities, respectively [11-13].

Fig. 3 Weibull distribution of time-to-failure for (a) Negative CVS of -3.5V at LRS (on-state) (b) Positive CVS of +6.6V at HRS (off-state). V<sub>stress</sub> is applied on a fresh device at -3.5V for LRS and at +6.6V after reset to HRS. Device structure: W1, 8 nm a-Si/8 nm TiO2. Cell size: 40 nm.

W1

10<sup>2</sup>

10<sup>1</sup>

For negative CVS (LRS), it exhibits the bimodal distribution behavior. For positive CVS (HRS), a single-shallow-slope Weibull distribution is observed, which is similar to the shallow one of the negative CVS. This voltage polarity dependence of breakdown and Weibull slopes have not been observed in the dielectrics in MIM capacitors or MOSFETs [11-13, 19-26].

It is generally well accepted that a percolation path will be gradually formed during the stress through random defect generation, leading to an abrupt hard breakdown and the conventional single Weibull slope with good area scaling, as observed in thicker dielectric layers [19-21]. Bimodal slopes have also been reported in nanoscale dielectrics, and several different explanations have been provided [12, 22-26]. In dielectrics with grains and grain boundaries (GB) [22-24], the steep Weibull slope at the lower percentile was attributed to breakdown at GBs leading to early device failure, and the upper percentile was mostly related to grain breakdown. Similar bimodal distribution has been observed in dual-layer structures with a transition from a steep Weibull slope at low percentiles to a shallow slope at high percentiles [25-26], and has been explained by the difference in defect generation rates in the two layers [26]. Defect clustering model has also been developed to explain the bimodal distribution in nanoscale dielectrics, by introducing the non-uniform clustering defect generation [12]. However, the co-existence of single and bimodal distributions at opposite stress polarities in a-VMCO devices in Fig. 3 has not been observed in other devices. It cannot be explained by the above mechanisms, either.

Fig.4 Weibull distribution of time-to-failure for the MSM devices with a single 8-nm amorphous-Si layer (W4), stressed at -2.0 V. Device size: 40 nm.

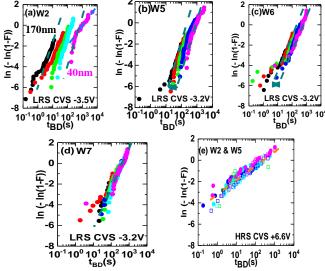

To further investigate the failure mechanism responsible for the bimodal distribution at negative CVS in a-VMCO (Fig.3a), Metal-(a-Si)-Metal (MSM) devices consisting of a single amorphous-Si layer with the same thickness as the a-Si barrier layer in a-VMCO RRAM cells [29] are stressed at negative bias. As shown in Fig. 4, the t<sub>BD</sub> Weibull distribution for a-Si MSM has a single slope, which is the same as the shallow slope in Fig. 3a and in Fig. 3b, suggesting that the a-Si layer is responsible for the shallow slope breakdown in all these cases and the presence of TiO<sub>2</sub> reduces the early breakdown probability and causes the early steep slope at LRS. This seems agreeing well with the explanation in ref. [26] that the defect generation rate in the a-Si layer may be substantially lower than that in the TiO<sub>2</sub> layer, leading to the bimodal distribution in Fig. 3a. If this is the case, question remains as why it cannot be applied to TDDB at HRS (Fig. 3b) where a single shallow slope dominates.

### B. Area and thickness dependent TDDB

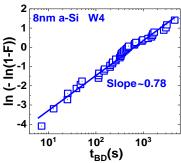

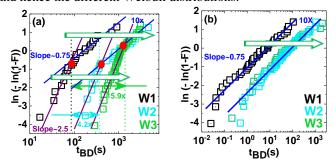

Conventionally, time-to-failure follows the same Weibull distribution after area-scaling [19-20]. To further examine the Weibull slopes and the responsible failure mechanism, negative and positive CVS were performed in a-VMCO devices with different sizes and a-Si layer thickness (W2, W5-W7). The  $t_{\rm BD}$  of large cells are scaled to the reference  $t_{\rm BD}$  of the minimal cell by a vertical shift of  $\ln(A_i/A_{\rm Ref})$  in the Weibits plots, where  $A_{\rm Ref}$  is minimal cell area (40\*40nm) and  $A_i$  is the area of larger cells.

Fig. 5 (a)-(d) Area scaling results at negative CVS (LRS) with different a-Si thickness: (a) 8 nm (b) 5 nm (c) 4 nm (d) 3 nm. The TiO<sub>2</sub> layer thinness is 8 nm. Device sizes range between 40nm, 60nm, 90nm, 120nm and 170nm. The scaling of Weibull distribution at negative CVS improves with a-Si layer becomes thinner. Devices with thinner a-Si layers (W5-W7) are stressed under the same CVS voltage at -3.2 V. (e) Weibull distributions have good area-scaling at positive CVS showing a single shallow slope.

The area scaling results at negative CVS (LRS) with different a-Si thickness are shown in Figs. 5a-5d. Devices with 8nm a-Si do not scale well with area, but it improves for thinner a-Si and the distribution becomes dominated by the steeper slope. In contrast, devices stressed at positive CVS (HRS), as shown in Figs. 5e, scale well with area, exhibiting the shallow slope only. It is clear that the stress polarity has a significant impact on the Weibull distribution and also on how the device size and layer thickness affects the breakdown mechanism. This cannot be explained by the previously proposed mechanisms. Next we will first describe in Section III.C the defect profile difference between HRS at positive CVS and LRS at negative CVS, and also the physical process of bimodal TDDB caused by different defect generation rates. Based on their correlation, we will then investigate the TDDB polarity dependence in Section III.D.

### C. Defect profile modulation and TDDB process

Defects profiles have been extracted in our precious work for both HRS and LRS using RTN signals in an unstressed a-VMCO device [18], as shown in Fig. 6a. Defects exist in both TiO<sub>2</sub> and a-Si layers. At HRS, there is defects-'less' region at TiO<sub>2</sub> side of TiO<sub>2</sub>/a-Si interfacial layer (IL), which does not exist at LRS, suggesting that defect profile modulation occurs predominantly at TiO<sub>2</sub> side of IL. The resistance states, represented by the read out

current at  $V_{TE} = 3$  V, are correlated well with the 'defects-less' region, as it becomes wider at HRS and narrower at LRS, as illustrated in Fig. 6b, confirming that the defect profile modulation in TiO<sub>2</sub> near the IL is responsible for the resistive switching. Note that this defect profile modulation is caused by the movement of pre-existing defects in un-stressed devices which have uniform spatial distribution in the lateral direction as shown in Fig. 6b [15-18], instead of by those defects generated by the stress. The nature of the defects responsible for resistive switching in a-VMCO device has been investigated in our previous works [15-18]. Switching in a-VMCO devices has been attributed to the distribution modulation of positively charged oxygen vacancies in the TiO2 switching layer, through field-accelerated drift of the defects. This profile modulation of pre-existing defects provides a foundation for analyzing the TDDB mechanism in a-VMCO RRAM

Fig. 6 Defects profile extracted based on RTN at LRS ('o') and HRS ('o'). (a) the distribution plotted vs resistance state by plotting  $X_T$  (from BE) vs.  $I_{read}$  measured at  $V_{TE}$ =3.0. Defect profile modulation predominantly occurs in a 'defect-less' region in TiO<sub>2</sub> near IL. (b) 'Defect-less' region becomes wider at HRS, resulting in higher resistance.

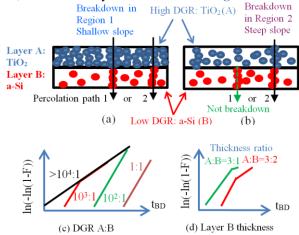

For the physical process of bimodal Weibull distribution, Raghavan et al [24, 25] reported that it could be explained and modelled by the much higher new defect generation rates (DGR) in localized grain boundaries in high-k layer. The bimodal distribution occurs only in small size devices due to the random distribution of GB where some devices may have many GBs while others may only have a few, as shown in Figs. 7a&b. For large size devices, the average distribution of GB across the HK film leads to a single slope, hence an overall area scaling is not valid [25]. This seems to agree well with Fig. 5a. Wu et al further developed the non-uniform defect clustering generation model to explain the bimodal distribution [12]. As shown in the TEM image in Fig. 1a, there indeed exists grains and grain boundaries in the TiO<sub>2</sub> layer, which may intrinsically lead to localized or clustered defect generation and higher generation rates, and contribute to the bimodal distribution.

Nigam et al [26] demonstrated that the difference in defect generation rates of the two layers can also change the Weibull distribution from bimodal to a single slope. For devices in region 1 in Fig.3a, the number of GBs and defects generated in the top TiO<sub>2</sub> layer happens to be sufficiently high so that breakdown can take place anywhere through the top layer, which acts effectively as an electrode and the breakdown is controlled by the bottom a-Si layer only, as shown in Fig. 7a, resulting in the shallow slope.

For devices in region 2 in Fig.3a, GBs and defects generated in the top TiO<sub>2</sub> layer is not sufficient to always warrant a conduction path when the bottom a-Si layer breaks down, as illustrated by the dashed green arrow in Fig.7b. The top layer

here can provide additional protection, so that the breakdown probability at low  $t_{BD}$  reduces in region 2 in Fig.3a, resulting in the steep slope that deviates from the shallow slope in region 1. In another word, the breakdown at low  $t_{BD}$  is controlled by both layers, as illustrated by the black arrow in Fig.7b.

Fig. 7 Schematic illustration of the breakdown process for dual-layer dielectric stack (a) for devices in the region 1 in Fig. 2a and (b) in the region 2. The dashed green arrow indicates that the stack does not break down when the bottom layer is broken. The black arrow indicates the possible breakdown path of the stack. The impact of (c) DGR ratio in two layers and (d) a-Si layer thickness on Weibull distribution as in Ref. [26].

The results in ref. [26] can be briefly summarized in Figs. 7c &d as, (1) TDDB distributions are bimodal when defect generation rate is significantly different in the two layers (Fig. 7c A:B=10<sup>2</sup>~10<sup>4</sup>), where the shallow TDDB slope is limited by the more robust layer B and the Weibull slope is that of B (Fig. 7a); The steep slope occurs in devices that TDDB is limited by lucky events in both layers (Fig. 7b) and the slope is that of the entire thick stack; (2) When the difference in DGR is small (1~10<sup>2</sup>), only steep slope can be observed (Fig. 7c); (3) When the difference is huge (>10<sup>4</sup>), only shallow slope can be observed (Fig. 7c); (4) A thinner layer B leads to further decrease of the shallow slope, and an increase of the Weibit value where the transition occurs so that smaller sample sizes are required to observe the shallow part of the TDDB distributions due to area scaling effect (Fig. 7d) [19-20].

In the next section, we will examine the correlation between defect profile modulation in a-VMCO and the DGR difference as proposed above, and analyze its impact on the polarity, area and thickness dependence of Weibull distribution observed in a-VMCO devices.

## D. Correlation between defect profile and DGR

Since a-VMCO is at HRS when stressed at positive CVS, and is at LRS at negative CVS, the difference in pre-existing defect profile should have a significant impact on the breakdown process and mechanism, as illustrated in **Figs. 8(a-c)** by a picture of TDDB mechanism in a-VMCO RRAM. The pre-existing defect profile modulation occurs predominantly at TiO<sub>2</sub> side of IL, leading to the switching between HRS and LRS. Defect generation by CVS (•) will form a percolation path leading to the breakdown [18]. The different Weibull distributions observed in a-VMCO can be explained as follows.

As shown in Fig. 8(a), at HRS ( $^{\circ}$ ), the defects- $^{\circ}$ less' region at TiO<sub>2</sub> side of TiO<sub>2</sub>/a-Si interfacial layer (IL) region, which

does not exist at LRS, leads to ×10 higher overall device resistance. The good agreement between the shallow slopes in a-VMMCO in Fig. 3b and in the single a-Si layer MSM device shown in Fig. 4 where the TiO2 layer is absent support the TDDB is controlled by the a-Si layer. The absence of preexisting defects in the TiO<sub>2</sub>/IL region under positive CVS at HRS widens the high-resistance "defect-less" region at TiO<sub>2</sub> side of IL, as shown in Fig. 5b. The much higher resistance in this TiO<sub>2</sub> region leads to a very high internal electric field. Since defect generation generally follows a power law against the stress voltage and stress time,  $\Delta N = A \cdot V^m \cdot t^n$ , [23-26], where  $\Delta N$  is the amount of degradation induced by defect generation, m and n are the power factors for stress voltage and time, respectively, and A is a constant. Higher internal electric field significantly increases the DGR, so that the breakdown is dominated by a-Si as shown in Fig. 7a, and hence the single slope and good area scaling under positive CVS shown in Fig. 3b & Fig. 5e. This also agrees well with the explanation in Fig. 7c when the DGR ratio is larger than 10<sup>4</sup>.

Fig. 8 The overall picture illustrating the failure mechanisms in a-VMCO RRAM (a) at positive CVS, (b) at negative CVS and (c) for thinner a-Si stack at negative CVS.

In contrast, at LRS, the pre-existing defects move back to  $TiO_2$  side of  $TiO_2$ /a-Si IL region (' $\circ$ '), as shown in Fig. 8(b), similar to that occurred in a fresh device (Fig. 6a), leading to ×10 lower device resistance, lower internal electric field in TiO<sub>2</sub>, and a relatively lower local DGR. The smaller difference in DGR between TiO2 and a-Si layers results in the bimodal Weibull distribution at LRS in Fig. 3a, as the shallow slope of the bimodal distribution occurs in devices with higher DGRs in TiO<sub>2</sub> layer, in which the breakdown is controlled by the more robust a-Si layer, hence the shallow slope (Fig.7a). This is similar to what happened at positive CVS. The steep slope occurs in devices with less GBs and lower DGRs in TiO2, in which the breakdown is dominated by lucky events in the entire stack. The steep slope is determined by the full thickness of the complete stack, as shown in Fig. 7b and also in Fig. 7c when the DGR ratio is between  $10^2$  and  $10^4$ .

To further examine the above analysis, TDDB in devices with different process conditions that lead to different qualities in TiO<sub>2</sub> layer and at its interface are measured. As shown in Fig. 9a & b, W2/P2 has an improved overall processing condition with better quality in both TiO<sub>2</sub> and a-Si layer than W1/P1. The t<sub>BD</sub> has improved ~10 times at both CVS polarities when compared to W1. The process of W3 is improved over W2 by adding a specific cleaning treatment prior to the TiO<sub>2</sub> deposition; hence improved the quality of the TiO2 only. Interestingly, as shown in Fig, 9a, further improvement of the TiO<sub>2</sub> quality alone leads to a further improvement only in the steep slope region at negative CVS, where the value of steep slope is unchanged but the Weibit at the transition point from steep slope to shallow slope becomes higher. This agrees well with refs. [25, 26] that moderately less GBs and lowered DGRs in TiO<sub>2</sub> layer will lead to longer T<sub>BD</sub> in the steep slope region only, as shown in Fig. 7c. Furthermore, the improvement of TiO<sub>2</sub> quality in W3 is not sufficient enough to reduce its DGR significantly at the high local Eox under positive CVS, so that the TDDB at positive CVS in W2 and W3 is not affected and is still dominated by the a-Si, as shown in Fig. 9b. This result provides strong support for the correlation between defect profiles at HRS/LRS and defect generation rates during TDDB, and hence the different Weibull distributions.

Fig. 9 Comparison of Weibull distribution of time-to-failure in processes W1, W2 and W3 for (a) Negative CVS at -3.5V, LRS (on state) (b) Positive CVS at +6.6V, HRS (off state). Cell size is 40 nm.

The above correlation can also explain the different TDDB area and thickness dependence at positive and negative stress polarities observed in Fig. 5a-5e. At positive CVS, the higher defect generation rate in the wide "defect-less" region in TiO<sub>2</sub> leads to a single breakdown mechanism controlled by a-Si, hence the single shallow slope and good area scaling in the Weibull distribution even when the a-Si layer is thinner, because the overall defect generation rate in a-Si is much lower than that in TiO<sub>2</sub>.

At negative CVS, the difference in defect generation rate in a-Si and  $TiO_2$  is smaller, but still exists, in the 8-nm  $TiO_2$  / 8-nm a-Si device (W2). This leads to the bimodal distribution and prevents the good area scaling [25]. When a-Si becomes thinner (**Fig. 5b-d**) and stressed under the same voltage, the steep slope becomes dominant and the area-scaling is improved. This is because Eox in both layers increases proportionally, so that the Eox value in a-Si increases much more due to its much higher resistance than the  $TiO_2$  at LRS, leading to a higher DGR in a-Si (**Fig. 8c**), which is getting closer to that in  $TiO_2$  eventually in devices with 3-nm a-Si layer and the breakdown is controlled by the entire stack. The Weibull distribution becomes

dominated by one single steep slope, and hence the better area scaling. This also agrees with Fig. 7d that reducing the thickness of the more robust layer in the dual layer structure leads to an increase of the Weibit value where the transition occurs and eventually a transition of Weibull distribution from bimodal slopes to a single steeper slope, as the dominating layer for TDDB shifts from the more robust layer to the entire stack [26].

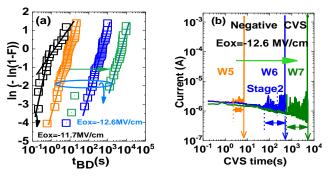

To further support this analysis, Weibull distributon at negative CVS with a-Si thichness ranging from 8 nm to 3 nm, all stressed under similar electric field, are compared in Fig. 10a. Reducing a-Si thickness leads to the steep slope becomes slightly shallwer when all thinner devices are stressed at the same Eox =-12.6 MV/cm, apart from the occasional early failures due to lower yield. This again agrees well with Fig. 7d, indicating that TDDB is controlled by the entire stack. Furthermore, t<sub>DB</sub> under the same Eox has sinificantly improved for thinner a-Si, as confirmed in Fig. 10b, indicating the better overall stack quality is achieved with thinner a-Si layer.

Fig. 10 (a) Time-to-failure Weibull distribution of devices with same Eox but different a-Si thickness, under negative CVS. Device size: 40 nm; TiO<sub>2</sub> thickness: 8 nm; a-Si thickness (from left to right): 8 nm (W1), 5 nm (W5), 4 nm (W6), 3 nm (W7); Thinner a-Si leads to steep slope and longer t<sub>BD</sub> at same Eox. (b) I-t curves comparison under the same negative electric field for thinner stacks in W5, W6 and W7.

Based on the results obtained in this work, several factors and their correlations should be considered in order to improve the TDDB in a-VMCO, including the pre-existing defect profile modulation, its impact on local electric field and DGR, the thickness of the a-Si layer, the quality of the dieletric layers and their interface. The quality of a-Si layer determines the higher percentile at negative CVS and the overall performance at positive CVS, as the defect-'less' region in a-Si is the last strong hold before the device breakdown. Using thinner a-Si layer may improve the area scaling at negative CVS, and the resultant lower yield and higher DGR may need to be mitigated, possibly by keeping the same Eox in the a-Si layer. The quality of the TiO<sub>2</sub> layer is also critical, because it, combined with the a-Si layer, determines the lower percentile of the bimodal Weibull distribution at negative CVS.

## IV. CONCLUSIONS

TDDB characteristics and mechanism in non-filamentary a-VMCO RRAM are investigated in this work by using CVS and Weibull distributions combined with the defect profile modulation obtained from the RTN technique. The unique feature of a bimodal Weibull distribution at LRS and a single shallow slope distribution at HRS, including its stress polarity, device area

and a-Si layer thickness dependence, can be explained by the correlation between defect profile modulation and different defect generation rates in different layers and in grain boundaries in TiO<sub>2</sub>. The critical layers affecting the TDDB performance are identified, which provides useful guidance for device performance improvement.

#### REFERENCES

- [1] H.-S. P. Wong, H.-Y. Lee, S. Yu, Y.-S. Chen, Y. Wu, P.-S. Chen, B. Lee, F. T. Chen, and M.-J. Tsai, "Metal–oxide RRAM," *Proceedings of the IEEE*, vol. 100, no. 6, pp. 1951-1970, Jun, 2012. *DOI*: 10.1109/JPROC.2012.2190369

- [2] U. Russo, D. Ielmini, C. Cagli, and A. L. Lacaita, "Filament conduction and reset mechanism in NiO-based resistive-switching memory (RRAM) devices," *IEEE Trans. Electron Devices*, vol. 56, no. 2, pp. 186-192, Feb, 2009. DOI: 10.1109/TED.2008.2010583.

- [3] D. Carta, I. Salaoru, A. Khiat, A. Regoutz, C. Mitterbauer, N. M. Harrison, and T. Prodromakis, "Investigation of the switching mechanism in TiO2-based RRAM: a two-dimensional EDX approach," ACS Appl. Mater. Interfaces, vol. 8, no. 30, pp. 19605-19611, July, 2016. DOI: 10.1021/acsami.6b04919

- [4] D.-H. Kwon, K. M. Kim, J. H. Jang, J. M. Jeon, M. H. Lee, G. H. Kim, X.-S. Li, G.-S. Park, B. Lee, and S. Han, "Atomic structure of conducting nanofilaments in TiO<sub>2</sub> resistive switching memory," *Nat. Nanotechnol.*, vol. 5, no. 2, pp. 148-153, Feb, 2010. DOI: 10.1038/nnano.2009.456

- [5] B. Govoreanu, G. Kar, Y. Chen, V. Paraschiv, S. Kubicek, A. Fantini, I. Radu, L. Goux, S. Clima, and R. Degraeve, "10×10 nm<sup>2</sup> Hf/HfO<sub>x</sub> crossbar resistive RAM with excellent performance, reliability and low-energy operation," in *IEDM Tech. Dig.*, 2011, pp. 31.36. 31-31.36. 34. DOI: 10.1109/IEDM.2011.6131652

- [6] Y. Y. Chen, L. Goux, S. Clima, B. Govoreanu, R. Degraeve, G. S. Kar, A. Fantini, G. Groeseneken, D. J. Wouters, and M. Jurczak, "Endurance/Retention Trade-off on HfO<sub>2</sub>/Metal Cap 1T1R Bipolar RRAM," *IEEE Trans. Electron Devices*, vol. 60, no. 3, pp. 1114-1121, Mar, 2013. DOI: 10.1109/TED.2013.2241064

- [7] N. Sedghi, H. Li, I. Brunell, K. Dawson, R. Potter, Y. Guo, J. Gibbon, V. Dhanak, W. Zhang, and J. Zhang, "The role of nitrogen doping in ALD Ta<sub>2</sub>O<sub>5</sub> and its influence on multilevel cell switching in RRAM," *Appl. Phys. Lett.*, vol. 110, no. 10, pp. 102902, Mar, 2017. DOI: 10.1063/1.4978033

- [8] L. Goux, A. Fantini, A. Redolfi, C. Chen, F. Shi, R. Degraeve, Y. Y. Chen, T. Witters, G. Groeseneken, and M. Jurczak, "Role of the Ta scavenger electrode in the excellent switching control and reliability of a scalable low-current operated TiN\ Ta<sub>2</sub>O<sub>5</sub>\ Ta RRAM device," in VLSI Symp. Tech. Dig., 2014, pp. 1-2. DOI: 10.1109/VLSIT.2014.6894401

- [9] R. Degraeve, A. Fantini, S. Clima, B. Govoreanu, L. Goux, Y. Y. Chen, D. Wouters, P. Roussel, G. S. Kar, and G. Pourtois, "Dynamic 'hour glass' model for SET and RESET in HfO<sub>2</sub> RRAM," in VLSI Symp. Tech. Dig., 2012, pp. 75-76. DOI: 10.1109/VLSIT.2012.6242468

- [10] S. Clima, Y. Y. Chen, C. Y. Chen, L. Goux, B. Govoreanu, R. Degraeve, A. Fantini, M. Jurczak, and G. Pourtois, "First-principles thermodynamics and defect kinetics guidelines for engineering a tailored RRAM device," J. Appl. Phys., vol. 119, no. 22, pp. 225107, Jun, 2016. DOI: 10.1063/1.4953673

- [11] R. Degraeve, P. Roussel, L. Goux, D. Wouters, J. Kittl, L. Altimime, M. Jurczak, and G. Groeseneken, "Generic learning of TDDB applied to RRAM for improved understanding of conduction and switching mechanism through multiple filaments," in *IEDM Tech. Dig.*, 2010, pp. 28.24. 21-28.24. 24. DOI: 10.1109/IEDM.2010.5703438

- [12] E. Wu, B. Li, J. Stathis, R. Achanta, R. Filippi, and P. McLaughlin, "A time-dependent clustering model for non-uniform dielectric breakdown," in *IEDM Tech. Dig.*, 2013, pp. 15.13. 11-15.13. 14. *DOI*: 10.1109/IEDM.2013.6724635

- [13] S. Long, X. Lian, C. Cagli, L. Perniola, E. Miranda, M. Liu, and J. Suñé, "A model for the set statistics of RRAM inspired in the percolation model of oxide breakdown," *IEEE Electron Device Lett.*, vol. 34, no. 8, pp. 999-1001, Aug, 2013. *DOI*: 10.1109/LED.2013.2266332

- [14] K. Baek, S. Park, J. Park, Y.-M. Kim, H. Hwang, and S. H. Oh, "In situ TEM observation on the interface-type resistive switching by electrochemical redox reactions at a TiN/PCMO interface," *Nanoscale*, vol. 9, no. 2, pp. 582-593, Jan, 2017. *DOI*: 10.1039/C6NR06293H

- [15] B. Govoreanu, D. Crotti, S. Subhechha, L. Zhang, Y. Chen, S. Clima, V. Paraschiv, H. Hody, C. Adelmann, and M. Popovici, "A-VMCO: A novel forming-free, self-rectifying, analog memory cell with low-current operation, nonfilamentary switching and excellent variability," in VLSI Symp. Tech. Dig., 2015, pp. T132-T133. DOI: 10.1109/VLSIT.2015.7223717

- [16] B. Govoreanu, L. Di Piazza, J. Ma, T. Conard, A. Vanleenhove, A. Belmonte, D. Radisic, M. Popovici, A. Velea, and A. Redolfi, "Advanced a-VMCO resistive switching memory through inner interface engineering with wide (> 10²) on/off window, tunable μA-range switching current and excellent variability," in VLSI Symp. Tech. Dig., 2016, pp. 1-2. DOI: 10.1109/VLSIT.2016.7573387

- [17] S. Subhechha, B. Govoreanu, Y. Chen, S. Clima, K. De Meyer, J. Van Houdt, and M. Jurczak, "Extensive reliability investigation of a-VMCO nonfilamentary RRAM: Relaxation, retention and key differences to filamentary switching," in *Proc. IRPS*, 2016, pp. 6C-2-1-6C-2-5. *DOI*: 10.1109/IRPS.2016.7574568

- [18] J. Ma, Z. Chai, W. D. Zhang, J. F. Zhang, Z. Ji, B. Benbakhti, B. Govoreanu, E. Simoen, L. Goux, and A. Belmonte, "Investigation of Preexisting and Generated Defects in Nonfilamentary a-Si/TiO<sub>2</sub> RRAM and Their Impacts on RTN Amplitude Distribution," *IEEE Trans. Electron Devices*, vol. 65, no. 3, pp. 970-977, 2018. *DOI*: 10.1109/TED.2018.2792221

- [19] R. Degraeve, G. Groeseneken, R. Bellens, J. L. Ogier, M. Depas, P. J. Roussel, and H. E. Maes, "New insights in the relation between electron trap generation and the statistical properties of oxide breakdown," *IEEE Trans. Electron Devices*, vol. 45, no. 4, pp. 904-911, Apr, 1998. *DOI*: 10.1109/16.662800

- [20] J. Stathis, "Percolation models for gate oxide breakdown," J. Appl. Phys., vol. 86, no. 10, pp. 5757-5766, Nov, 1999. DOI: 10.1063/1.371590

- [21] J. Fothergill, "Estimating the cumulative probability of failure data points to be plotted on Weibull and other probability paper," *IEEE transactions on Electrical Insulation*, vol. 25, no. 3, pp. 489-492, June, 1990. DOI: 10.1109/14.55721

- [22] K. Yew, D. S. Ang, and G. Bersuker, "Bimodal Weibull Distribution of Metal/High-k Gate Stack TDDB—Insights by Scanning Tunneling Microscopy," *IEEE Electron Device Lett.*, vol. 33, no. 2, pp. 146-148, Feb, 2012. DOI: 10.1109/LED.2011.2174606

- [23] N. Raghavan, K. L. Pey, K. Shubhakar, and M. Bosman, "Modified Percolation Model for Polycrystalline High-k Gate Stack With Grain Boundary Defects," *IEEE Electron Device Lett.*, vol. 32, no. 1, pp. 78-80, Jan, 2011. DOI: 10.1109/LED.2010.2085074

- [24] N. Raghavan, K. L. Pey, K. Shubhakar, X. Wu, W. Liu, and M. Bosman, "Role of grain boundary percolative defects and localized trap generation on the reliability statistics of high-κ gate dielectric stacks," in *Proc. IRPS*, 2012, pp. 6A. 1.1-6A. 1.11. *DOI*: 10.1109/IRPS.2012.6241862

- [25] N. Raghavan, A. Padovani, X. Wu, K. Shubhakar, M. Bosman, L. Larcher, and K. Pey, "The "buffering" role of high-κ in post breakdown degradation immunity of advanced dual layer dielectric gate stacks," in *Proc. IRPS*, 2013, pp. 5A. 3.1-5A. 3.8. *DOI*: 10.1109/IRPS.2013.6532020

- [26] T. Nigam, A. Kerber, and P. Peumans, "Accurate model for time-dependent dielectric breakdown of high-k metal gate stacks," in *Proc. IRPS*, 2009, pp. 523-530. *DOI*: 10.1109/IRPS.2009.5173307

- [27] Z. Chai, J. Ma, W. Zhang, B. Govoreanu, E. Simoen, J. Zhang, Z. Ji, R. Gao, G. Groeseneken, and M. Jurczak, "RTN-based defect tracking technique: Experimentally probing the spatial and energy profile of the critical filament region and its correlation with HfO<sub>2</sub> RRAM switching operation and failure mechanism," in VLSI Symp. Tech. Dig., 2016, pp. 1-2. DOI: 10.1109/VLSIT.2016.7573402

- [28] L. Zhang, B. Govoreanu, A. Redolfi, D. Crotti, H. Hody, V. Paraschiv, S. Cosemans, C. Adelmann, T. Witters, and S. Clima, "High-drive current (> 1MA/cm²) and highly nonlinear (> 10³) TiN/amorphous-Silicon/TiN scalable bidirectional selector with excellent reliability and its variability impact on the 1S1R array performance," in *IEDM Tech. Dig.*, 2014, pp. 6.8. 1-6.8. 4. DOI: 10.1109/IEDM.2014.7047000