# Characterization of negative bias temperature instability of Ge MOSFETs with GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stack

J. Ma, J. F. Zhang, Z. Ji, B. Benbakhti, W. Zhang, X. F. Zheng, J. Mitard, B. Kaczer, G. Groeseneken, S. Hall, J. Robertson, and P. Chalker

Abstract—Ge is a candidate for replacing Si, especially for pMOSFETs because of its high hole mobility. For Si-pMOSFETs, negative bias temperature instabilities (NBTI) limit their lifetime. There is little information available for the NBTI of Ge-pMOSFETs with Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stack. The objective of this work is to provide this information and to compare the NBTI of Ge- and Si-pMOSFETs. New findings include: (i) The time exponent varies with stress biases/field when measured by either the conventional slow DC or pulse I-V technique, making the conventional Vg-accelerated method for predicting the lifetime of Si-pMOSFETs inapplicable to Ge-pMOSFETs used in this work; (ii) The NBTI is dominated by positive charges (PC) in dielectric, rather than generated interface states; (iii) The PC in Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> can be fully annealed at 150 °C; and (iv) The defect losses reported for Si sample were not observed. For the first time, we report that the PCs in oxides on Ge and Si behave differently and, to explain the difference, an energy-switching model is proposed for hole traps in Ge-MOSEFTs: their energy levels have a spread below the edge of valence band, i.e. Ev, when neutral, lift well above Ev after charging, and return below Ev following neutralization.

Index Terms—Ge MOSFETs, Ge/GeO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, NBTI, High-k on Ge, Hole traps, Positive charges, Degradations, Lifetime.

## I. INTRODUCTION

The successful downscaling of Si MOSFETs has enabled a continuous increase of devices per chip and the operation speed since 1960s, but it is approaching its end since the device is running out of atoms and its leakage and variability is becoming intolerable [1-6]. To continue improving device speed, much effort has been made to replace Si by high mobility semiconductors [1-4]. Ge is a strong candidate, especially for pMOSFETs because its intrinsic hole mobility is about 4 times of that for Si.

Promising results have already been demonstrated for Ge pMOSFETs through two approaches. One is to use a Si-cap of several mono-layers [1, 2, 4]. This offers good compatibility with existing Si processes and the gate dielectric stack used is often the same as that for Si. However, the interface states are relatively high, the Si-cap increases the separation between gate and channel, and there are difficulties in making Ge nMOSFETs of good performance [7]. The other approach is

Manuscript received MMM DDD, 2013. This work was supported by the Engineering and Physical Science Research Council of UK under the grant no. EP/I012966/1. The review of this letter was arranged by Editor X.Y.

J. Ma, J. F. Zhang, Z. Ji, B. Benbakhti, and W. Zhang are with the School of Engineering, John Moores University, Liverpool L3 3AF, U.K. (e-mail: J.F.Zhang@ljmu.ac.uk).

X. F. Zheng is with Xidian University, Xi'an, China. J. Mitard, B. Kaczer, and G. Groeseneken are with IMEC, Leuven B3001, Belgium. G. Groeseneken is also with KU Leuven. S. Hall and P. Chalker are with University of Liverpool. J. Robertson is with University of Cambridge.

preparing  $GeO_2$ /high-k stack directly on Ge~[2, 3, 8-10]. By controlling the interaction of  $GeO_2$  with Ge~and suppressing the evaporation of GeO, it has been reported that the interface states can be as low as that for  $SiO_2$ /Si [8, 9, 11]. This approach offers the potential for fabricating Ge~nMOSFETs [8, 12, 13].

The process for fabricating Ge MOSFETs is becoming sufficiently mature and reproducible to warrant research into their reliability and some encouraging results have been reported [7, 14, 15]. Good TDDB data were obtained [14], but electron trapping is high [16], similar to that in the early stage of developing high-k/SiON stack for Si [17-20]. For Si-based CMOS technologies, the negative bias temperature instability (NBTI) is the most severe reliability issue, since it results in a lifetime of pMOSFETs shorter than that of nMOSFETs [21, 22]. With Si-capped Ge MOSFETs, it has been reported that NBTI can be lower than its Si counterpart [2, 14, 15, 23]. For the Ge pMOSFETs without a Si-cap layer, however, there is little information available on the NBTI.

The <u>central objective</u> of this work is to provide the information on the NBTI of Ge pMOSFETs with a Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> structure. The results will be compared with both Si/SiON, Si/SiON/high-k stacks, and Si-capped Ge MOSFETs and similarities and differences will be highlighted. The dependence of NBTI on both stress field and temperature is investigated. Attention will be paid to the defects responsible for NBTI and the relative contribution from generated interface states will be estimated. It is found that the positive charges (PCs) in the oxides on Ge and Si behave differently and, when measured by either the conventional slow DC or pulse I-V technique, the conventional lifetime prediction method developed for Si based on the constant power exponent is not applicable to Ge pMOSFETs used in this work. A defect energy switching model is proposed to explain the differences.

# II. DEVICES AND EXPERIMENTS

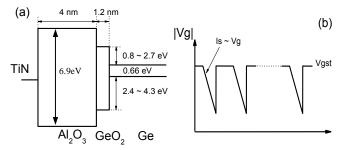

The gate dielectric stack used for the majority of tests in this work is shown in Fig. 1(a). The Ge layer is 700 nm and grown directly on Cz-Si wafers. To minimize interface states, a 1.2 nm GeO<sub>2</sub> was prepared by exposing clean Ge surface to an atomic oxygen flux at a low temperature of 150 °C for 20 min. A 4 nm Al<sub>2</sub>O<sub>3</sub> was then produced by molecular beam deposition in the same chamber [24], resulting in a SiO<sub>2</sub> equivalent oxide thickness of 2.35 nm for the stack. Although Al<sub>2</sub>O<sub>3</sub> only has a modest dielectric constant, it can suppress the evaporation of GeO and, in turn, the deterioration of GeO<sub>2</sub>/Ge interface [25]. The device was annealed post-metallization in forming gas at 350 °C for 20 min. The channel length used in this work is typically 1 µm and the width is 50 µm. The pMOSFETs have a 10 nm PVD TiN metal gate. For the purpose comparison, other structures

Ge/Si-cap/SiO<sub>2</sub>/HfO<sub>2</sub>, Si/SiON/High-k, and Si/SiON and their details will be given in figure captions or legends.

The test follows the standard 'stress-and-sense' procedure [26, 27] and a typical Vg waveform is given in Fig. 1(b). To monitor the threshold voltage shift, i.e.  $\Delta V th$ , the stress was periodically interrupted and the source current, i.e. Is, instead of Id, versus Vg was recorded under a drain bias of Vd = -100 mV by using a Vg ramp to minimize the impact of junction leakage.  $\Delta V th$  was extracted from the Vg shift at a constant Is =  $100 \times W$  / L nA [28].

Fig. 1 (a) Schematic energy band diagram and structure of the used sample. (b) The gate bias waveform used in tests. Vgst is the stress bias.

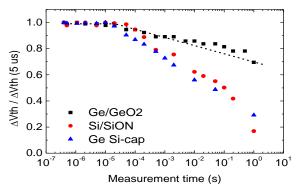

Fig. 2 Dependence of  $\Delta V$ th on the measurement time for different samples. The stress field over the interfacial layer is 6.5 MV/cm for Ge/GeO<sub>2</sub> and 10 MV/cm for both Si/SiON and Si-capped Ge sample. The stress time is 1 ks and temperature is 20 °C. During the measurement period, Vg was kept negative and did not reach zero, as shown in Fig. 1(b).

The temperature used is in the range of  $20 \sim 125$  °C and the stress and measurement were performed at the same temperature, unless otherwise specified. The electric field over the interfacial GeO<sub>2</sub> layer was calculated from Eox=(Vg-Vth)×3.9/(6×EOT), where EOT is the SiO<sub>2</sub> equivalent thickness and the GeO<sub>2</sub> has a dielectric constant of 6 [29].

The measurement time, tm, can be defined as the time for sweeping Vg from the stress level Vgst to the measurement Vg for Is =  $100 \times W$  / L nA (see the ramp in Fig. 1(b)). Reliable measurements were obtained only for tm>0.4  $\mu$ s and the recovery for shorter time could not be assessed. Fig. 2 shows that the recovery is negligible when tm increases from ~0.4  $\mu$ s to ~10  $\mu$ s and tm=5  $\mu$ s is used here to minimize recovery. When tm=1 sec, recovery lowers  $\Delta V$ th by 70~80% for Si/SiON and the Si-capped Ge sample, but only ~30% for Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>, so that  $\Delta V$ th is relatively stable for the latter.

In this work, both tm=5 µs [27, 30] and tm=1 sec [31-33] were used. Although tm=5 µs minimizes recovery, agreement has not been reached on the NBTI kinetics even for

Si/SiON[34-36]. Under the conventional slow DC measurement of tm=1 sec, however, it is widely accepted that  $\Delta$ Vth follows a power law and the Vg-accelerated lifetime prediction method is established [37] and some industrial researchers preferred tm=1 s (e.g. [38]). It is of importance to find out whether this method is applicable for Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>.

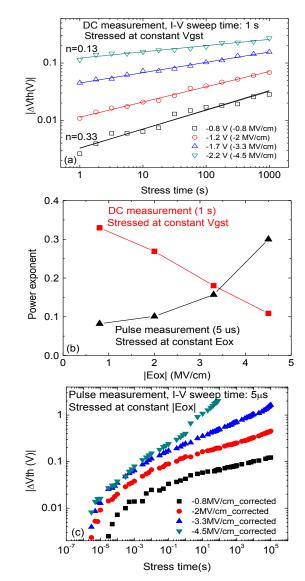

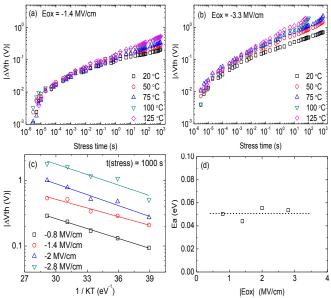

Fig. 3 (a) NBTI degradation kinetics under different stress biases at 20 °C measured by slow DC I-V of tm= 1 s. The solid lines were fitted with a power law. The stress Vg does not change with time and Eox in the legend is the field strength over GeO<sub>2</sub> at the start of stress. (b) The time exponent at different Vgst for DC and Eox for pulse measurement extracted within the time range of 1 s to 1000 s. (c) NBTI kinetics under constant stress Eox at 20 °C measured by pulse I-V of tm=5 $\mu$ s. The stress |Vg| was increased with time to maintain a constant Eox, here.

# III. RESULTS AND DISCUSSIONS

### A. NBTI under different stress fields

The Vg-accelerated lifetime prediction method for Si/SiON requires the time exponent of  $\Delta V$ th to be independent of the stress Vg [27, 37]. When using this method, the stress bias, i.e. Vgst, typically does not change with time and tm is ~seconds. We applied these test conditions first to the Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and

Fig. 3(a) shows that  $\Delta V$ th was substantial even under an operational bias level of -1.2 V (Eox=-2 MV/cm) and it is Vg-accelerated. The defect density in the current Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> is clearly too high to meet the lifetime required for commercial application. It is of interest, however, to study their properties and dynamics, since the past experiences from high-k/SiON stack on Si show that the nature of the defects does not change when their density reduces substantially through process optimization [39, 40].

Although Fig. 3(a) appears similar to the conventional Si/SiON where  $\Delta V$ th follows a power law against stress time [27],  $\log |\Delta V$ th| versus  $\log (time)$ , however, is not a parallel shift for different Vgst and the time exponent, n, reduces from 0.33 at Vgst=-0.8 V to 0.13 at Vgst=-2.2 V in Fig. 3(b), despite that the  $|Eox| \le 4.5$  MV/cm used here is well within the range typically used for Si MOSFETs when observing a constant time exponent [27, 41].

A possible explanation for the lower n at higher Vgst is that, when the stress was carried out under constant bias Vgst, the formation of positive charges lowers the |Eox| near the Ge/dielectric interface. At higher Vgst, there are more PCs, leading a larger reduction in |Eox| near Ge, lowering  $|\Delta Vth|$  and in turn n. This PCs-induced |Eox| reduction can be corrected by increasing Vgst<sub>i</sub> for a stress step i from the Vgst at the start of stress by  $\Delta Vth_{i-1}$ , so that the effective stress bias, (Vgst-Vth), and Eox is kept constant. To suppress the recovery during measurement and the consequent underestimation of  $\Delta Vth$ , tm=5 µs was used and Fig. 3(c) gives the result under constant stress Eox. The degradation does not follow a power law with a single exponent over the whole range of test time in Fig. 3(c), although data between 1 and 1000 sec can be fitted with a power law. The time exponent extracted between 1 and 1000 sec is given in Fig. 3(b), which increases for higher |Eox|. As a result, suppressing recovery during measurements and stressing under constant Eox do not lead to a constant time exponent and the conventional lifetime prediction method cannot be used for the Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> used here.

# B. Effects of stress temperature and anneal

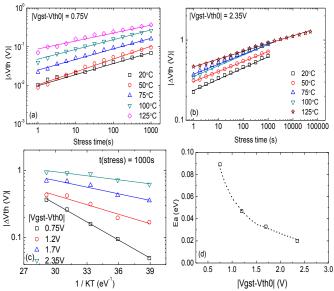

Fig. 4(a) shows the  $\Delta Vth$  under  $|Vgst-Vth0|=0.75\ V$  for different stress temperatures with tm=1 s. As expected, the NBTI is thermally activated. Under a higher  $|Vgst-Vth0|=2.35\ V$ , however, Fig. 4(b) shows that  $\Delta Vth$  tends to become insensitive to temperature as it rises. This leads to a reduction of the activation energy, Ea, for higher Vgst, as shown in Figs. 4(c) and 4(d). Ea was extracted from the Arrhenius plot at 1000 sec in Fig. 4(c). It is an apparent activation energy with the measurement made at the stress temperature [42]. The insensitivity of  $\Delta Vth$  to temperature over 75 °C at  $|Vgst-Vth0|=2.35\ V$  in Fig. 4(b) is not caused by running out of defects, since the longer stress clearly shows that the degradation can be higher.

The temperature-insensitivity of  $\Delta V th$  at a stress time of 1000 sec has not been observed for Si/SiO<sub>2</sub> [43] and Si/SiON/High-k [44] and is worth of further exploring. One possibility is that the recovery during the 1 s measurement delay is also a thermally activated process, compensating the

degradation. Figs. 5(a)-(d) give the results measured with tm=5  $\mu s$  that minimized the recovery. The  $\Delta V th$  appears insensitive to temperature initially (e.g. <1 ms) and the reason is not known at present. For longer stress time, however, it is clearly thermally enhanced and the apparent Ea taken at 1000 sec is insensitive to Eox in Fig. 5(d).

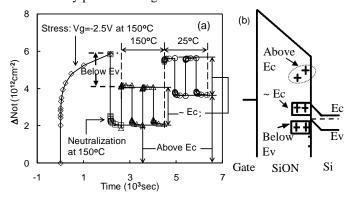

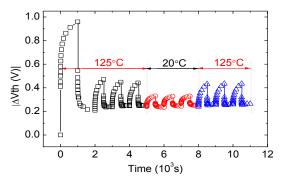

To study the anneal of PCs, a device was exposed to 150 °C after stressing at 20 °C. Fig. 6(a) shows that nearly all PCs can be neutralized in 1800 sec. In comparison, the neutralization is less than half for Si/SiON under similar anneal conditions [45]. The following speculation is made to explain this difference.

It has been reported that the positive charges in SiO<sub>2</sub> can have energy levels above the bottom edge of the Si conduction band, i.e. Ec, making them difficult to reach by free electrons from Si substrate [17, 31-33]. The Ec offset between SiO<sub>2</sub> and Si is around 3.2 eV, so that these traps can be located well above the Si Ec. The Ec offset between GeO<sub>2</sub> and Ge, however, has been reported to be as low as 0.8 eV [46], so that the positive charge in GeO<sub>2</sub> should be closer to Ge Ec, making them relatively easier to neutralize at elevated temperature.

It is worth pointing out that the PCs in  $SiO_2$  can only be fully neutralized when the anneal temperature reached 400 °C [45, 47]. After the anneal, the  $\Delta V$ th in the subsequent stress becomes smaller than that before anneal, because of defect losses and slowdown in SiON [45, 47]. To test if this is also the case for  $Ge/GeO_2/Al_2O_3$ , the device was re-stressed after anneal and Fig. 6(b) clearly shows that  $\Delta V$ th has not been reduced for the re-stress, so that the defect losses and slowdown were not observed here.

Fig. 4 NBTI kinetics under different stress temperatures, tm=1 s, and |Vgst-Vth0|=0.75V (a) and 2.35V (b). (c) is the Arrhenius plot at 1000 sec. (d) gives the extracted apparent activation energy from (c) at different |Vgst-Vth0|.

### C. Contribution of generated interface states

The positive charges responsible for NBTI can originate from both the bulk of gate oxide and the oxide/substrate interface [22, 39, 43, 48]. When NBTI was reported for thick SiO<sub>2</sub> (e.g. 95 nm) in early years, the stress Eox was relatively

low and it was observed that PCs from the oxide and the interface were equally important [43]. For thin (< 3 nm) oxides, however, the stress Eox used is typically higher (e.g. 10 MV/cm) and hole injection occurs [22, 27]. The charging of hole traps leads to a larger contribution of PCs from oxides to  $\Delta V th$  than that from generated interface states [22, 30, 49]. Nitridation introduces additional hole traps, further enhancing the contribution of PC from oxides to  $\Delta V th$  [50, 51]. We now assess the relative importance of PCs from interface states for Ge pMOSFETs of a GeO\_2/Al\_2O\_3 stack.

Fig. 5 NBTI kinetics under different stress temperatures with tm=  $5 \mu s$ . The Eox during stress was kept at a constant of -1.4 MV/cm (a) and -3.3 MV/cm (b). (c) is the Arrhenius plot at 1000 sec. (d) gives the extracted apparent activation energy from (c) at different Eox.

Fig. 6 (a) The  $1^{st}$  stress was under Vg= -2.8 V, 20 °C for 1000 s. The device was then annealed for 20 min at 150 °C in air with all terminals floating. The  $2^{nd}$  stress was under the same conditions as the  $1^{st}$  one. (b) compares the  $\Delta$ Vth for these two stresses by resetting the stress time to zero at the start of the  $2^{nd}$  stress. tm= 1s.

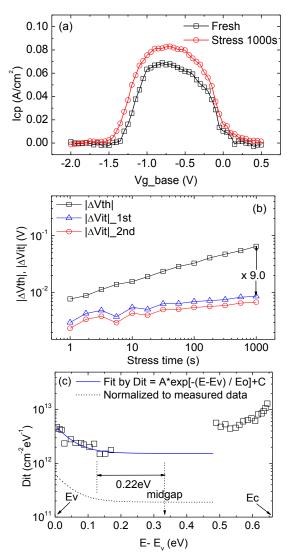

Fig. 7(a) presents a typical result of charge pumping measurements before and after a stress. The generation of interface states clearly can be seen from the raised peak after stress, resulting in an increase of interface state density of  $\Delta Dit = 1.88 \times 10^{11}~\text{cm}^{-2}\text{eV}^{-1}$ . As a first order estimation of the contribution from  $\Delta Dit$  to  $\Delta Vth$ , we assume a uniform energy distribution of interface states. It has been reported that the charge neutrality level is in the lower half of the bandgap for Ge [52], but, for simplicity, we assume that all states between the mid-band and Ev are donor-like and contribute to positive charges. This gives rise to a positive charge of  $\Delta Nit = 0.33 \times \Delta Dit = 6.20 \times 10^{10}~\text{cm}^{-2}$  and a corresponding threshold voltage shift of  $\Delta Vit = \Delta Nit \times q / Cox$  [53]. Fig. 7(b) compares the  $\Delta Vit$  with the measured  $\Delta Vth$ , showing that  $\Delta Vit$  is one order of magnitude smaller.

Fig. 7 (a) The charge pumping current, Icp, before and after a stress under Vgst = -1.2 at 20 °C. (b) A comparison of the 1<sup>st</sup> and 2<sup>nd</sup> order estimated contribution of enerated interface states to the threshold voltage shift with the measured  $\Delta V th.$  (c) The energy distribution reported in ref. [29]. The dashed line is obtained by normalizing the solid line to the measured  $1.88 \times 10^{11}$  cm $^{-2} eV^{-1}$  in the range of 0.22 eV from midgap. The charge pumping amplitude is 1V, frequency is 1 MHz and the rise and fall time is 20 ns.

The  $\Delta$ Dit measured by CP is the average value over an energy range of  $\pm 0.22$  eV centered at midgap in our case [54]. It has been reported that the interface state density rises substantially towards the band edge, so that an assumption of uniform energy distribution can underestimate the contribution of  $\Delta Dit$ . As a second order approximation, we use the energy profile reported in earlier work [29] for Dit. As shown in Fig. 7(c), the solid curve was fitted with the test data by using an expression, Dit =  $A \times \exp[-(E-Ev)/Eo] + C$ , where A, Eo and C are constants. This function was then normalized to the measured ΔDit over the energy range from midgap to 0.22 eV below it, resulting in the dotted line in Fig. 7(c). The positive charges were estimated by integrating the dotted line between midgap and Ev, resulting in  $\Delta Nit = 7.89 \times 10^{10}$  cm<sup>-2</sup>. The corresponding  $\Delta Vit$  is also shown in Fig. 7(b) and its contribution remains insignificant. The stress in Fig. 7 was at 20 °C. At 125 °C, the measured ΔVit (not shown) can be twice as high as that at 20 °C, but it is still only about 1/8<sup>th</sup> of the total ΔVth. We conclude that the NBTI of Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> is dominated by positive charges in the dielectric.

Fig. 8 (a) Different types of PCs in Si/SiON/HfO<sub>2</sub>. After stress and neutralization, Eox =  $\pm$  5MV/cm were applied with alternating polarity to show the traps ~Ec and above Ec at 150 °C and then 25 °C [47]. Vg>0 V reduces  $\Delta$ Not and Vg<0 V increases PCs. (b) illustrates the energy level differences for the three types of PCs.  $\Delta$ Not was measured from the Id-Vg shift at midgap, where interface states are neutral for Si MOSFETs.

# D.Positive charges in dielectric: energy switching model

It has been shown in Section III-A and B that NBTI in the Ge sample behaves differently from that in Si samples. In this section, the cause for these differences will be investigated at the defect level. For Si pMOSFETs, the positive charges (PC) in gate oxides have a complex behavior and have been explained differently by different groups [27, 30, 36, 54-57]. Figs. 8(a)&(b) summarize their typical behavior and one way of characterizing them is to separate them into three groups according to their energy ranges: hole traps below the Si Ev, around Si Ec, and above Si Ec [17, 22, 31-33, 44]. After building up PCs during stress at high |Eox|, substantial neutralization occurs under Vg>0 at a relatively low Eox = 5 MV/cm. By alternating the polarity of Eox =  $\pm 5$  MV/cm, traps around Si Ec can be repeatedly charged and neutralized, and those well above Ec remain charged and are not neutralized. Most traps below Si Ev cannot be re-charged under Eox = -5

MV/cm. In the following, we will show that PCs in GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> on Ge are different.

Fig. 9 shows a typical result for GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> on Ge. Although the first impression is that the PCs behave similarly to those in Si samples, a close inspection, however, reveals several important differences:

Fig. 9 Positive charges in Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> device. The stress was at Vgst = -2.6 V and 125 °C, After a neutralization step at +4.2 MV/cm at 125 °C, Eox =  $\pm$  3.3 MV/cm were applied with alternating gate polarity in a temperature sequence of 125 °C, 20 °C, and 125 °C. The time for switching temperature is 40mins with gate floating and this time was not included in the time axis.

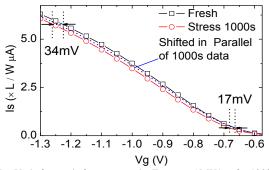

Fig. 10 Is - Vg before and after stress under Eox = -6.5 MV/cm for 1000 s on a Si/SiON/HfO/AlO device. The dotted line is a parallel shift of the line for 1000 sec data until it reached the fresh Is - Vg at low |Vg|. It shows the stressed Is - Vg is not in parallel with the fresh Is - Vg.

- The charge and neutralization of traps around Ec by alternating Vg polarity for Si samples in Fig. 8(a) is insensitive to measurement temperature, i.e. T, since it has an energy level accessible even at room temperature and the charge and neutralization are through carrier tunneling here that is a process insensitive to T. In contrast, Fig. 9 shows that the charge/neutralization cycling in Ge sample reduces for lower T.

- The density of PCs in traps above Ec in Si samples in Fig. 8(a) clearly increase at lower T. After being neutralized at a higher T, the defect energy level remains above Ec. As soon as T is reduced, electrons leave the defects, tunnel into the Si conduction band, recharge the defects, and result in the higher PCs. For the Ge sample, however, Fig. 9 shows that the remaining PCs hardly increase when the temperature lowers from 125 °C to 20 °C.

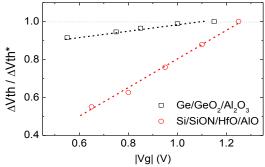

- When Vg sweeps from the stress level in the positive direction to a sensing Vg, some traps in Si samples fall below the Fermi level and are neutralized [22, 27, 30]. Fig. 11 shows that |ΔVth| nearly halved when Vg moves from -1.2 V to -0.6V. In contrast, the change of ΔVth with Vg is

much smaller for Ge samples (Fig. 11), indicating detrapping from traps below Ev for Ge is less important than that in Si.

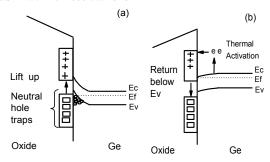

The above differences indicate that the PCs in Ge samples are different from those in Si samples, so that a different model is needed. We propose an 'energy switching model' to explain these differences. The first-principle calculations show that energy levels of a defect in dielectric can strongly depend on its charge states [58, 59]. The 'energy switching' here means that the energy level of a defect switches from one value to another, when its charge-state changes. As illustrated in Fig. 12(a), neutral hole traps have a spread of energy levels below Ev of Ge. Application of higher |Eox| allows charging the traps further below Ev, leading to the field activation of NBTI in Fig. 3(a). Application of higher temperature also charges the hole traps further below Ev, resulting in the higher  $\Delta V$ th at higher temperatures in Figs. 4 and 5.

Fig. 11 Dependence of  $\Delta V$ th on the sensing Vg.  $\Delta V$ th\* is the  $\Delta V$ th measured at the highest sensing |Vg| for a sample. Devices were stressed under an initial Eox = -6.5 MV/cm for 1000 s at  $20 \, ^{\circ}\text{C}$ .

Fig. 12 The energy-switching model for positive charges in Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>. (a) shows charging under Vg < 0, (b) shows neutralization under Vg > 0. ' $\Box$ ' represents neutral hole traps and '+' represents charged hole traps.

After being charged, instead of staying at the same energy level, the defects are lifted to energy levels well above Ge Ev. This allows most hole traps holding their PCs when Vg is swept from stress toward threshold levels, giving rise to the smaller reduction in Fig. 11, when compared with that in Si/SiON

If the energy levels of the lifted PCs were near Ec, their neutralization should be insensitive to temperature, similar to those in Si samples in Fig. 8. Fig. 9 shows that this is not the case for Ge samples, however. On the other hand, if the lifted PCs are above Ec, their neutralization should be thermally enhanced, as illustrated by Fig. 12(b), similar to the PC above Si Ec in Fig. 8(b) [17, 31, 44]. This is confirmed below.

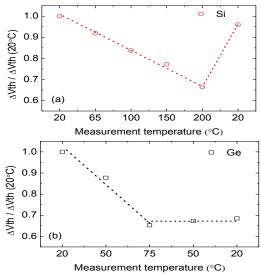

Fig. 13 shows that an increase of T clearly lowers  $\Delta V$ th for both Si (Fig. 13(a)) and Ge (Fig. 13(b)) samples. The thermal activation of neutralization supports the proposition that there are PCs above the Ge Ec. However, when T reduces subsequently,  $\Delta V$ th rises back for Si, but remains the same for Ge samples. This supports the view that, unlike the case of Si samples, the energy level of defects drops back below Ev after neutralization at high T to prevent recharge at the subsequent low T for Ge sample without re-stress, as illustrated in Fig. 12(b). Because the energy level was switched below Ev after neutralization at 125 °C, lowering temperature to 20 °C did not recharge them, unlike the Si sample in Fig. 13(b).

For Ge sample at a time t\*, a signature of the energy-switch after neutralization is that the number of un-neutralized PC is determined by the highest temperature a sample was exposed prior to t\*, rather than the temperature at t\*. In contrast, for Si sample, the lack of energy level switching means that the number of un-neutralized PC at t\* is determined by the temperature at t\*. In another word, one may say that Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> can remember its temperature history, but Si/SiON cannot. The underlying physical mechanism for the energy switching is not known. One speculation is the field-assisted multi-phonon emission during hole trapping [55] and further evidences are needed to support it.

Fig. 13 Impact of measurement temperature on  $\Delta V$ th for (a) Si/SiON and (b) Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>. The lines are a guide for the eye. tm= 1s.

### IV. CONCLUSIONS

This work characterizes the NBTI for Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and compares it with Si samples. Similar to Si samples, NBTI is activated both electrically and thermally for Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>. There are a number of important differences with Si samples and the new findings include: (i) The time exponent is not constant for different stress biases/fields when measured with either slow DC or pulse technique, which makes the conventional Vg acceleration lifetime prediction technique of Si samples inapplicable to the Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>; (ii)  $\Delta$ Vth is

substantially less sensitive to measurement time; (iii) The neutralization can be nearly 100% under a temperature as low as 150  $^{\circ}$ C, in contrast with the 400  $^{\circ}$ C needed by Si sample. (iv) Defect losses were not observed for Ge/GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>.

On defects, the positive charges in  $GeO_2/Al_2O_3$  on Ge dominate the NBTI. They do not follow the same model as that for PCs in SiON/Si and an energy-switching model has been proposed: the energy levels have a spread for neutral hole traps below Ev, lift up after charging, and return below Ev following neutralization. Finally, we point out that these conclusions are drawn based on the samples used in this work and their generic applicability awaits further tests.

### REFERENCES

- [1] M. Caymax, G. Eneman, F. Bellenger, C. Merckling, A. Delabie, G. Wang, R. Loo, E. Simoen, J. Mitard, B. De Jaeger, G. Hellings, K. De Meyer, M. Meuris, and M. Heyns, "Germanium for advanced CMOS anno 2009: a SWOT analysis," in *IEDM Tech. Dig.*, pp. 428-431, 2009.

- [2] C. Le Royer, "Interfaces and performance: What future for nanoscale Ge and SiGe based CMOS?(invited)," *Microelectron. Eng.*, vol. 88, no. 7, pp. 1541-1548, 2011.

- [3] P. C. McIntyre, Y. Oshima, E. Kim, and K. C. Saraswat, "Interface studies of ALD-grown metal oxide insulators on Ge and III–V semiconductors (Invited Paper)," *Microelectron. Eng.*, vol. 86, no. 7–9, pp. 1536-1539, 2009.

- [4] J. Mitard, B. De Jaeger, F. E. Leys, G. Hellings, K. Martens, G. Eneman, D. P. Brunco, R. Loo, J. C. Lin, D. Shamiryan, T. Vandeweyer, G. Winderickx, E. Vrancken, C. H. Yu, K. De Meyer, M. Caymax, L. Pantisano, M. Meuris, and M. M. Heyns, "Record I(ON)/I(OFF) performance for 65nm Ge pMOSFET and novel Si passivation scheme for improved EOT scalability," in *IEDM Tech. Dig.*, pp. 1-4, 2008.

- [5] A. Asenov, B. Cheng, D. Dideban, U. Kovac, N. Moezi, C. Millar, G. Roy, A. R. Brown, and S. Roy, "Modeling and simulation of transistor and circuit variability and reliability," in *Proc. IEEE Custom Integr. Circuits Conf.*, pp. 1-8, 2010.

- [6] M. Duan, J. F. Zhang, Z. Ji, W. D. Zhang, B. Kaczer, T. Schram, R. Ritzenthaler, and G. Groeseneken, "New Analysis Method for Time-Dependent Device-To-Device Variation Accounting for Within-Device Fluctuation," *IEEE Trans. Electron Devices*, vol. 60, no. 8, pp. 2505-2511, 2013.

- [7] J. Mitard, K. Martens, B. DeJaeger, J. Franco, C. Shea, C. Plourde, F. E. Leys, R. Loo, G. Hellings, G. Eneman, E. W. Wei, J. C. Lin, B. Kaczer, K. DeMeyer, T. Hoffmann, S. DeGendt, M. Caymax, M. Meuris, and M. M. Heyns, "Impact of Epi-Si growth temperature on Ge-pFET performance," in ESSDERC, pp. 411-414, 2009.

- [8] A. Toriumi, T. Tabata, C. Hyun Lee, T. Nishimura, K. Kita, and K. Nagashio, "Opportunities and challenges for Ge CMOS Control of interfacing field on Ge is a key (Invited Paper)," *Microelectron. Eng.*, vol. 86, no. 7–9, pp. 1571-1576, 2009.

- [9] R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka, and S. Takagi, "High-Mobility Ge pMOSFET With 1-nm EOT Al<sub>2</sub>O<sub>3</sub>/GeO<sub>x</sub>/Ge Gate Stack Fabricated by Plasma Post Oxidation," *IEEE Trans. Electron Devices*, vol. 59, no. 2, pp. 335-341, 2012.

- [10] L. Nyns, D. Lin, G. Brammertz, F. Bellenger, X. Shi, S. Sioncke, S. Van Elshocht, and M. Caymax, "Interface and Border Traps in Ge-Based Gate Stacks," ECS Trans., vol. 35, no. 3, pp. 465-480, 2011.

- [11] R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka, and S. Takagi, "Al<sub>2</sub>O<sub>3</sub> /GeO<sub>x</sub> /Ge gate stacks with low interface trap density fabricated by electron cyclotron resonance plasma postoxidation," *Appl. Phys. Lett.*, vol. 98, no. 11, pp. 112902-112901-112902-112903, 2011.

- [12] K. Morii, T. Iwasaki, R. Nakane, M. Takenaka, and S. Takagi, "High-Performance GeO<sub>2</sub>/Ge nMOSFETs With Source/Drain Junctions Formed by Gas-Phase Doping," *IEEE Electron Device Lett.*, vol. 31, no. 10, pp. 1092-1094, 2010.

- [13] L. Choong Hyun, T. Nishimura, K. Nagashio, K. Kita, and A. Toriumi, "High-Electron-Mobility Ge/GeO<sub>2</sub> n-MOSFETs With Two-Step Oxidation," *IEEE Trans. Electron Devices*, vol. 58, no. 5, pp. 1295-1301, 2011.

- [14] B. Kaczer, B. De Jaeger, G. Nicholas, K. Martens, R. Degraeve, M. Houssa, G. Pourtois, F. Leys, M. Meuris, and G. Groeseneken,

- "Electrical and reliability characterization of metal-gate/HfO<sub>2</sub>/Ge FET's with Si passivation," *Microelectron. Eng.*, vol. 84, no. 9–10, pp. 2067-2070, 2007.

- [15] J. Franco, B. Kaczer, P. J. Roussel, J. Mitard, M. Cho, L. Witters, T. Grasser, and G. Groeseneken, "SiGe Channel Technology: Superior Reliability Toward Ultrathin EOT Devices—Part I: NBTI," *IEEE Trans. Electron Devices*, vol. 60, no. 1, pp. 396 404, 2013.

- [16] B. Benbakhti, J. F. Zhang, Z. Ji, W. Zhang, J. Mitard, B. Kaczer, G. Groeseneken, S. Hall, J. Robertson, and P. Chalker, "Characterization of Electron Traps in Si-capped Ge MOSFETs with HfO2/SiO2 Gate Stack" *IEEE Electron Device Lett.*, vol. 33, no. 12, pp. 1681-1683, 2012.

- [17] J. F. Zhang, "Defects and instabilities in Hf-dielectric/SiON stacks (Invited Paper)," *Microelectron. Eng.*, vol. 86, no. 7-9, pp. 1883-1887, 2009.

- [18] J. F. Zhang, C. Z. Zhao, M. B. Zahid, G. Groeseneken, R. Degraeve, and S. De Gendt, "An assessment of the location of As-grown electron traps in HfO<sub>2</sub>/HfSiO stacks," *IEEE Electron Device Lett.*, vol. 27, no. 10, pp. 817-820, 2006.

- [19] C. Z. Zhao, and J. F. Zhang, "Effects of hydrogen on positive charges in gate oxides," J. Appl. Phys., vol. 97, no. 7, pp. 073703-073708, 2005.

- [20] C. Z. Zhao, J. F. Zhang, M. B. Zahid, B. Govoreanu, G. Groeseneken, and S. De Gendt, "Determination of capture cross sections for as-grown electron traps in HfO<sub>2</sub>/HfSiO stacks," *J. Appl. Phys.*, vol. 100, no. 9, pp. 093716-093711-093716-093710, 2006.

- [21] N. Kimizuka, T. Yamamoto, T. Mogami, K. Yamaguchi, K. Imai, and T. Horiuchi, "The impact of bias temperature instability for direct-tunneling ultra-thin gate oxide on MOSFET scaling," in VLSI Symp. Tech. Dig., pp. 73-74, 1999.

- [22] J. F. Zhang, Z. Ji, M. H. Chang, B. Kaczer, and G. Groeseneken, "Real Vth instability of pMOSFETs under practical operation conditions," in *IEDM Tech. Dig.*, pp. 817-820, 2007.

- [23] B. Kaczer, J. Franco, J. Mitard, P. J. Roussel, A. Veloso, and G. Groeseneken, "Improvement in NBTI reliability of Si-passivated Ge/high-k/metal-gate pFETs," *Microelectron. Eng.*, vol. 86, no. 7–9, pp. 1582-1584, 2009.

- [24] F. Bellenger, B. De Jaeger, C. Merckling, M. Houssa, J. Penaud, L. Nyns, E. Vrancken, M. Caymax, M. Meuris, T. Hoffmann, K. De Meyer, and M. Heyns, "High FET Performance for a Future CMOS GeO<sub>2</sub>-Based Technology," *IEEE Electron Device Lett.*, vol. 31, no. 5, pp. 402-404, 2010

- [25] K. Kita, S. K. Wang, M. Yoshida, C. H. Lee, K. Nagashio, T. Nishimura, and A. Toriumi, "Comprehensive Study of GeO<sub>2</sub> Oxidation, GeO Desorption and GeO<sub>2</sub>-Metal Interaction-understanding of Ge processing kinetics for perfect interface control," in *IEDM Tech. Dig.*, pp. 1-4, 2009.

- [26] J. F. Zhang, I. S. Al-kofahi, and G. Groeseneken, "Behavior of hot hole stressed SiO<sub>2</sub>/Si interface at elevated temperature," *J. Appl. Phys.*, vol. 83, no. 2, pp. 843-850, 1998.

- [27] Z. Ji, L. Lin, J. F. Zhang, B. Kaczer, and G. Groeseneken, "NBTI Lifetime Prediction and Kinetics at Operation Bias Based on Ultrafast Pulse Measurement," *IEEE Trans. Electron Devices*, vol. 57, no. 1, pp. 228-237, 2010.

- [28] H. Reisinger, O. Blank, W. Heinrigs, A. Muhlhoff, W. Gustin, and C. Schlunder, "Analysis of NBTI Degradation- and Recovery-Behavior Based on Ultra Fast VT-Measurements," in *Proc. IRPS*, pp. 448-453, 2006.

- [29] J. Mitard, F. Bellenger, L. Witters, D. J. B., V. B., L. Nyns, K. Martens, E. Vrancken, G. Wang, D. Lin, R. Loo, M. Caymax, K. De Meyer, M. Heyns, and N. Horiguchi, "Investigation of the electrical properties of Ge/high-k gate stack: GeO2 VS Si-cap," *International Conference on Solid State Devices and Materials*, 2011.

- [30] Z. Ji, J. F. Zhang, M. H. Chang, B. Kaczer, and G. Groeseneken, "An Analysis of the NBTI-Induced Threshold Voltage Shift Evaluated by Different Techniques," *IEEE Trans. Electron Devices*, vol. 56, no. 5, pp. 1086-1093, 2009.

- [31] J. F. Zhang, C. Z. Zhao, A. H. Chen, G. Groeseneken, and R. Degraeve, "Hole traps in silicon dioxides. Part I. Properties," *IEEE Trans. Electron Devices*, vol. 51, no. 8, pp. 1267-1273, 2004.

- [32] C. Z. Zhao, J. F. Zhang, G. Groeseneken, and R. Degraeve, "Hole-traps in silicon dioxides. Part II. Generation mechanism," *IEEE Trans. Electron Devices*, vol. 51, no. 8, pp. 1274-1280, 2004.

- [33] J. F. Zhang, M. H. Chang, and G. Groeseneken, "Effects of measurement temperature on NBTI," *IEEE Electron Device Lett.*, vol. 28, no. 4, pp. 298-300, 2007.

- [34] T. Grasser, B. Kaczer, W. Goes, H. Reisinger, T. Aichinger, P. Hehenberger, P. J. Wagner, F. Schanovsky, J. Franco, M. T. Luque, and

- M. Nelhiebel, "The Paradigm Shift in Understanding the Bias Temperature Instability: From Reaction-Diffusion to Switching Oxide Traps," *IEEE Trans. Electron Devices*, vol. 58, no. 11, pp. 3652-3666, 2011.

- [35] S. Mahapatra, N. Goel, S. Desai, S. Gupta, B. Jose, S. Mukhopadhyay, K. Joshi, A. Jain, A. E. Islam, and M. A. Alam, "A Comparative Study of Different Physics-Based NBTI Models," *IEEE Trans. Electron Devices*, vol. 60, no. 3, pp. 901-916, 2013.

- [36] Y. Gao, D. S. Ang, C. D. Young, and G. Bersuker, "Evidence for the transformation of switching hole traps into permanent bulk traps under negative-bias temperature stressing of high-k P-MOSFETs," in *Proc. IRPS*, pp. 5A.5.1-5A.5.5, 2012.

- [37] JEDEC, Failure Mechanisms and models for Semiconductor Devices, 2011.

- [38] S. Pae, J. Maiz, C. Prasad, and B. Woolery, "Effect of BTI Degradation on Transistor Variability in Advanced Semiconductor Technologies," *IEEE Trans. Dev. Mat. Rel.*, vol. 8, no. 3, pp. 519-525, 2008.

- [39] C. Z. Zhao, J. F. Zhang, C. Mo Huai, A. R. Peaker, S. Hall, G. Groeseneken, L. Pantisano, S. De Gendt, and M. Heyns, "Stress-Induced Positive Charge in Hf-Based Gate Dielectrics: Impact on Device Performance and a Framework for the Defect," *IEEE Trans. Electron Devices*, vol. 55, no. 7, pp. 1647-1656, 2008.

- [40] J. F. Zhang, M. H. Chang, Z. Ji, L. Lin, I. Ferain, G. Groeseneken, L. Pantisano, S. Gendt, and M. M. Heyns, "Dominant Layer for Stress-Induced Positive Charges in Hf-Based Gate Stacks," *IEEE Electron Device Lett.*, vol. 29, no. 12, pp. 1360-1363, Dec, 2008.

- [41] V. D. Maheta, E. N. Kumar, S. Purawat, C. Olsen, K. Ahmed, and S. Mahapatra, "Development of an Ultrafast On-the-Fly I-DLIN Technique to Study NBTI in Plasma and Thermal Oxynitride p-MOSFETs," *IEEE Trans. Electron Devices*, vol. 55, no. 10, pp. 2614-2622, 2008.

- [42] W. Muth, and W. Walter, "Bias temperature instability assessment of nand p-channel MOS transistors using a polysilicon resistive heated scribe lane test structure," *Microelectron. Reliab.*, vol. 44, no. 8, pp. 1251-1262, 2004.

- [43] K. O. Jeppson, and C. M. Svensson, "Negative bias stress of MOS devices at high electric fields and degradation of MNOS devices," J. Appl. Phys., vol. 48, no. 5, pp. 2004-2014, 1977.

- [44] J. F. Zhang, C. Z. Zhao, M. H. Chang, M. B. Zahid, A. R. Peaker, S. Hall, G. Groeseneken, L. Pantisano, S. De Gendt, and M. Heyns, "Impact of different defects on the kinetics of negative bias temperature instability of hafnium stacks," *Appl. Phys. Lett.*, vol. 92, no. 1, pp. 013501-013503, 2008.

- [45] M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, S. De Gendt, and G. Groeseneken, "New insights into defect loss, slowdown, and device lifetime enhancement," *IEEE Trans. Electron Devices*, vol. 60, no. 1, pp. 413 419, 2013.

- [46] L. Lin, K. Xiong, and J. Robertson, "Atomic structure, electronic structure, and band offsets at Ge:GeO:GeO<sub>2</sub> interfaces," *Appl. Phys. Lett.*, vol. 97, no. 24, pp. 242902-242903, 2010.

- [47] M. Duan, J. F. Zhang, Z. Ji, W. Zhang, B. Kaczer, S. D. Gendt, and G. Groeseneken, "Defect loss: A new concept for reliability of MOSFETs," IEEE Electron Device Lett., vol. 33, no. 4, pp. 480-482, 2012.

- [48] S. S. Tan, T. P. Chen, J. M. Soon, K. P. Loh, C. H. Ang, and L. Chan, "Nitrogen-enhanced negative bias temperature instability: An insight by experiment and first-principle calculations," *Appl. Phys. Lett.*, vol. 82, no. 12, pp. 1881-1883, 2003.

- [49] M. H. Chang, and J. F. Zhang, "On positive charge formed under negative bias temperature stress," J. Appl. Phys., vol. 101, no. 2, Jan 15, 2007

- [50] V. Huard, "Two independent components modeling for Negative Bias Temperature Instability," in *Proc. IRPS*, pp. 33-42, 2010.

- [51] S. W. M. Hatta, Z. Ji, J. F. Zhang, M. Duan, W. D. Zhang, N. Soin, B. Kaczer, S. De Gendt, and G. Groeseneken, "Energy Distribution of Positive Charges in Gate Dielectric: Probing Technique and Impacts of Different Defects," *IEEE Trans. Electron Devices*, vol. 60, no. 5, pp. 1745-1753, 2013.

- [52] A. Dimoulas, and P. Tsipas, "Germanium surface and interfaces (Invited Paper)," *Microelectron. Eng.*, vol. 86, no. 7–9, pp. 1577-1581, 2009.

- [53] T. Aichinger, M. Nelhiebel, and T. Grasser, "Refined NBTI characterization of arbitrarily stressed PMOS devices at ultra-low and unique temperatures," *Microelectron. Reliab.*, vol. 53, no. 7, pp. 937-946, 2013.

- [54] L. Lin, Z. Ji, J. F. Zhang, W. Zhang, B. Kaczer, S. De Gendt, and G. Groeseneken, "A Single Pulse Charge Pumping Technique for Fast

- Measurements of Interface States," *IEEE Trans. Electron Devices*, vol. 58, no. 5, pp. 1490-1498, 2011.

- [55] T. Grasser, B. Kaczer, W. Goes, T. Aichinger, P. Hehenberger, and M. Nelhiebel, "A Two-Stage Model for Negative Bias Temperature Instability," in *Proc. IRPS*, pp. 33-44, 2009.

- [56] Z. Y. Liu, H. Darning, W. J. Liu, C. C. Liao, L. F. Zhang, Z. H. Gan, W. Waisum, and L. Ming-Fu, "Comprehensive studies of BTI effects in CMOSFETs with SiON by new measurement techniques," in *Proc. IRPS*, pp. 733-734, 2008.

- [57] T. Grasser, H. Reisinger, P. J. Wagner, F. Schanovsky, W. Goes, and B. Kaczer, "The time dependent defect spectroscopy (TDDS) for the characterization of the bias temperature instability," in *Proc. IRPS*, pp. 16-25, 2010.

- [58] D. Liu, Y. Guo, L. Lin, and J. Robertson, "First-principles calculations of the electronic structure and defects of Al2O3," *J. Appl. Phys.*, vol. 114, no. 8, pp. 083704, 2013.

- [59] J. R. Weber, A. Janotti, and C. G. Van de Walle, "Native defects in Al2O3 and their impact on III-V/Al2O3 metal-oxide-semiconductor-based devices," *J. Appl. Phys.*, vol. 109, no. 3, pp. 033715, 2011.